Project Info

Please check this page frequently for additions.

April 23, update

- Instructions about the waveform and how to submit

April 11, list of updates, for details see below.

- Clock frequency has been specified (800 MHz).

- Availability of Test Bench.

- Notes about power calculation.

- A note about parameter sweeping.

Introduction

The Et4293 project will require to design a so-called Pseudo Random Number Generator (PRNG). This is a counter producing an output sequence that approximates the properties of random numbers. On particular implementation of a PRNG is a so-called linear feedback shift register (LFSR), See LFSR at wikipedia. See Hamburg University for a java-animation of an 8-bit LFSR with the tap-positions as we will use them.

Applications of hardware PRNGs include Spread spectrum communication, Whitening, Monte-carlo simulation, Stream ciphers, Test pattern generation, CRC generation and more.

Our goal will be to develop a PRNG with the following specifications/requirements (also see the Technical Info section below):

- 8 bit PRNG

- Choose between Fibonacci or Galois topology

- Tap positions at 8, 6, 5, 4 for Fibonacci type

- Use equivalent taps (such that they will generate the same sequence) if you use a Galois type topology.

- Clock frequency is 800 Mhz. The clock rise and fall times is 50ps. See the test bench.

- Can use an ideal 2-phase clock.

- Can use latches instead of flip-flops/registers.

- Make sure you have an initialization/power-up mechanism.

- 90 nm UMC CMOS technology

- 10 fF load at each output

The following should be delivered (see below for more details):

- Circuit files

- Poster (design report)

Here are the slides with a reference design.

Design Competition

The goal is to achieve the lowest power consumption, given the (fixed) frequency. The following notes can be made:

- All teams will use the same test bench

- VDD is variable (design specific)

- Area of layout is not of concern

- Bonus points will be awarded (see 'Marks').

Technical Info

- Circuit Style

You are free to use any circuit style (Chapter 6), including but not limited to complementary CMOS, ratioed logic, DCVSL, pass-transistor logic, CPL, dynamic logic. There is no need to stick to a style from the book. - Clocking Scheme

You can use any clocking scheme / Flip Flop type (Chapter 7), and any clocking scheme such as single phase, two phase, four phase, ... However, we will assume that we have an ideal 2-phase clock, that is, with phi and phi' (phi-inverse) readily available. See for example Figure 7.8 of the Rabaey book. There is no need to generate this clock, or to generate the inverse of the clock. If you want, you could use only one phase of the clock. If you want a more elaborate clock, you have to derive it using a proper circuit (for this, you won't need a layout). NOTE Compared to earlier instructions, you now have a 2-phase clock readily available, before it was only a single-phase master clock. - Memory Elements

See Chapter 7 of the Rabaey book, especially Sections 7.1 and 7.2, for information about memory elements. - XOR/XNOR

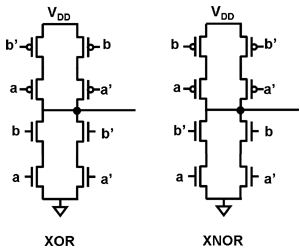

See Chapter 6 of the Rabaey book. While not shown in the book, below is a schematic for a standard xor/xnor circuit in CMOS.

You could think you would need also 2 inverters for generating the a' and b' inputs. (Note: a' means a-inverse.) However, these inverted inputs can be already available since the latch will have an out and an out' output. You are free to use any other XOR/XNOR, e.g. such as shown in Figure 6.47. - initialization/power-up mechanism.

Depending on the use of XOR or XNOR feedback, a shift register state of all-zeros or all-ones will stay forever in that state. Thus, this is called the forbidden combination. Make sure you implement a way to avoid this from (accidentally) happening during power-up, by including a '(re)set' signal to put all the values to all-zeros or all-ones. The test-bench will first fire this signal, before cycling through a number of states. - Power Improvement

Consider any known (or unknown ?) technique to improve power. At the circuit level, such techniques include body bias, sub-threshold logic, ... At the design level, such techniques include automatic sizing.

Probably the main technique will be proper device sizing combined with a reduced supply voltage. - Parameter Sweep

You can get from the TA's a copied handout about how to do parameter sweeping in Spectre. Parameter sweeping allows to run many simulations automatically in a row, while one or more parameters are changing. This can be helpful for the sizing of your design. - * Wave form*

There are no special specifications for the waveform, other than that the circuit 'works'. This means that the right sequence should be produced, for a full cycle of 256 states, when the cycle repeats. There is only one right sequence (apart from the fact that the Galois and Fibonacci produce each others reverse sequence).

Test Bench

Here is the

test bench for download. You

can decompress and untar (using tar xfz Test_bench.tar.gz) this

file, the result will be a library folder. After moving this folder

into your project folder, you can use this test bench for your design.

This is the test bench that we will use for the competition. You should

test your design to see if it can be added to the test bench. The

supply voltage is variable, to be adapted by you according to your

design. Here is the

schematic

of the test bench.

Please note that the test bench has a separate supply for the LFSR block. It is be the average power delivered by this supply that will be measured. is specified in the section Power Measurement below.

Power Measurement

The technique for power measurement has been described in this link. It has been adapted below.

- Change all the subcircuit's Vdd to an inputoutput Pin (you need to get the symbol again after each change)

- Change the test_bench's schematic as the test bench schematic with the link above. ( You need to add Vdc to the inputoutput Pin.)

In Analog Design Environment, go to Outputs, Setup, then a window as below (the setting Outputs window) appears.

Input the name: avepower (note: the window contains a typo, arvpower).

Click calculator open option for the calculator window to pop up.

In the calculator window, first click (it), then click the positive terminal of Vdc on test_bench Schematics, after this, click the minus sign.

Then click (vt), then click the wire between Vdc and Vdd pin, After this click, you need click times sign.

Now you get the Instantaneous power.

Keep the step above, then click the special Functions, find integ, then click.

Then the integ window pops up. Enter the time slot you want to calculate, then click OK.

press enter, click the time slot, like 70n, Then click divide sign /, At this time, the formula should look like the one on graph 3.

- In setting Outputs window, click get expression. You will get the expression you just calculated.

click add and OK.

Then simulate, you will get the average power in Analog Design Environment.

- Do not forget to save state.

Submission

You need to submit a tar or zip file containing your design library, that is, the directory/folder with the schematic files.

Report

The project assignment also includes reporting, in the form of a poster + presentation. The report (poster) should show schematic, design rationale, resulting waveforms, ... In particular, the poster should include the following:

- Why is your design good

- What is special about it

- Present design decisions, trade-offs, ...

- Present overall layout

- Include important schematics, waveforms, ...

- Everything needed for demonstrating functionality and performance References/citations (!)

Further instructions:

- Size is 1 x A1, legible at >2m,

- Time for presentation: 8 minutes

- Easy way for making poster: ppt slides, 6-up handout format enlarged

- Use Minimum number of words, maximum amount of information

Marks

- At least a 6 will be awarded for the design if it is functionally correct.

- The score can be improved based on creativity, elegance, robustness of the design

- Bonus points will be awarded as follows (provided enough

participants):

2 points for winner team

1.5 points for 2nd place, 1 for 3rd, 0.5 for 4th, 5th place - The bonus is to be added to overall mark

Due Date

The due date will be Friday Apr 25. This is the of the 3rd week of the next (4th) lecture period. The presentations, posters and competition will be in the afternoon. It is hoped that everybody can participate, please contact me (Nick) if that is not possible.

Note

- You will also work in teams of 2, please contact me if you want to work alone or in a larger team, or if you can't find a team mate.

- Final grade 50/50% project/exam

- Project: 60/40 design/poster+presentation