## **COMBINATIONAL LOGIC**

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

## **Exam**

- April 3<sup>rd</sup>, 9am 12am

- Written exam, open book, also printed slides with your notes on it.

| Material | Topic         | Remarks                           |

|----------|---------------|-----------------------------------|

| Ch 1     | Intro         | Completely, pay attention to §1.3 |

| Ch 2     | Manufacturing | Only §2.1 - §2.3                  |

| Ch 3     | Devices       | Completely                        |

| Ch 4     | Interconnect  | Except §4.4.5, §4.5               |

| Ch 5     | Inverter      | Completely                        |

| Ch 6     | Combinational | Only §6.1, §6.2                   |

| Ch 7     | Sequential    | Only §7.1, §7.2                   |

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

|                                                          | I .         | March 2008            |             |             |

|----------------------------------------------------------|-------------|-----------------------|-------------|-------------|

|                                                          | Thu<br>20   |                       | Tue<br>25   |             |

| Final Lecture:                                           | 15:45-17:30 | 8:45-10:30            | 10:45-12:30 | 13:45-15:30 |

| March 25, 10:45-12:30                                    | ок          |                       | OK          | OK          |

| Warch 25, 10.45-12.50                                    | ОК          | ОК                    | OK          | OK          |

|                                                          |             | OK                    | OK          | OK          |

| - Doom D (nyobobly)                                      |             |                       | OK          |             |

| Room D (probably)                                        |             | OK                    | OK          | OK          |

|                                                          |             |                       | OK          | OK          |

|                                                          |             | OK                    | OK          |             |

| ■ §7.1 – 7.2                                             |             | OK                    | OK          | OK          |

|                                                          |             | OK                    | OK          | OK          |

|                                                          |             | OK                    | OK          | OK          |

|                                                          |             |                       | OK          |             |

|                                                          |             |                       | OK          |             |

|                                                          | 9           | OK                    | OK          | OK          |

|                                                          | OK          |                       | OK          |             |

|                                                          |             | OK                    | OK          | OK          |

|                                                          |             |                       | OK          | OK          |

|                                                          |             |                       | OK          |             |

|                                                          | 4           | OK                    | OK          | OK          |

|                                                          |             |                       |             |             |

| TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational | 15:45-17:30 | 8:45-10:30<br>3/19/20 | 10:45-12:30 | 13:45-15:30 |

## **Combinational Logic - Outline**

- Conventional Static CMOS basic principles

- **■** Complementary static CMOS

- **Complex Logic Gates**

- VTC, Delay and Sizing

- Ratioed logic

- Pass transistor logic

- Dynamic CMOS gates →only illustration

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

## **Complementary Static CMOS Basic Principles**

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

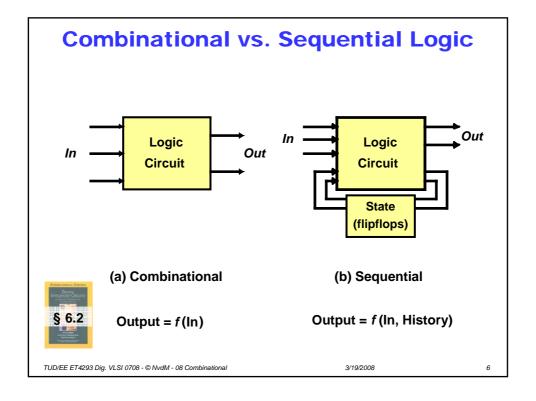

## Reminder

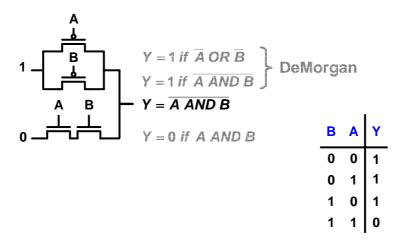

## **DeMorgan Transformations**

$$\overline{A+B} = \overline{A}.\overline{B}$$

$$\overline{A.B} = \overline{A} + \overline{B}$$

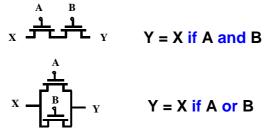

## **NMOS Transistors in Series/Parallel Connection**

Transistors can be thought as a switch controlled by its gate signal

NMOS switch closes when switch control input is high

$$Y = X \text{ if } A \text{ or } B$$

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

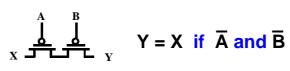

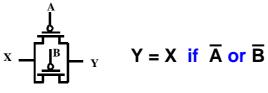

## PMOS Transistors in Series/Parallel Connection

PMOS switch closes when switch control input is low

$$Y = X$$

if ...

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

19/2008

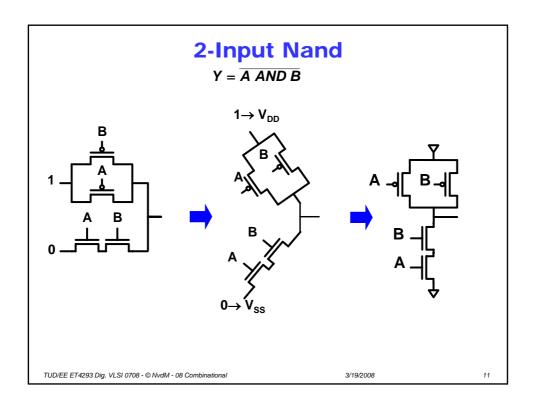

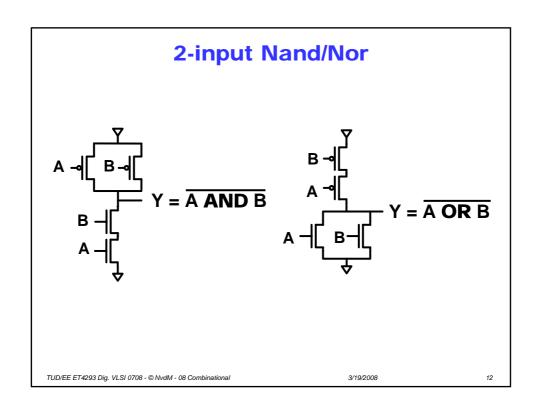

## 2-Input Nand

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

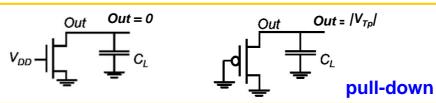

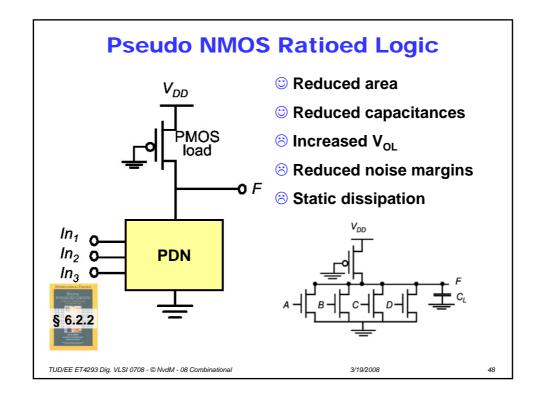

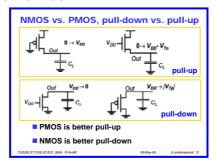

## NMOS vs. PMOS, pull-down vs. pull-up

- PMOS is better pull-up

- NMOS is better pull-down

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

13

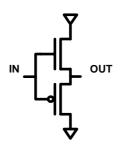

## **Bad Idea**

**Exercise:** Determine logic function

Determine  $V_{out}$ for  $V_{in} = V_{DD}$  and  $V_{in} = V_{SS}$

Why is this a bad circuit?

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

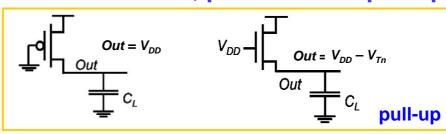

## **CMOS Gate is Inverting**

Assume full-swing inputs (high =  $V_{DD}$ , low =  $V_{SS}$ )

■ Highest output voltage of NMOS is

$$V_{GS}$$

-  $V_{Tn}$  =  $V_{DD}$  -  $V_{Tn}$

- An 1 on NMOS gate can produce a strong 0 at the drain, but not a strong 1

- Lowest output voltage of PMOS is

$$V_{DD} + V_{GS} - V_{Tp} = |V_{Tp}|$$

(with  $V_{GS}$ ,  $V_{Tp} < 0$  for PMOS)

- An 0 on PMOS gate can produce a strong 1 at the drain, but not a strong 0

- Need NMOS for pull-down, PMOS for pull-up

A 1 at input can pull-down, 0 at input can pull-up

**Inverting behavior**

For a non-inverting Complementary CMOS Gate, you can only use 2 inverting gates

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

15

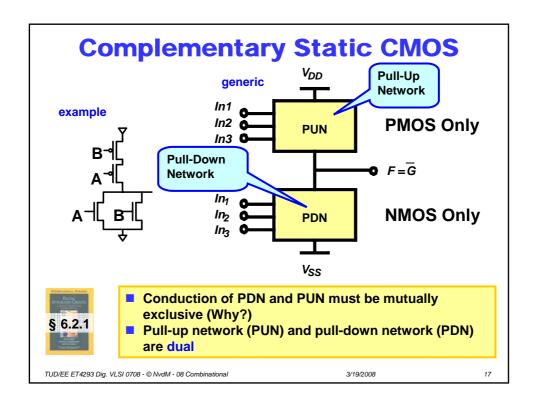

## **Complementary static CMOS**

- **Complex Logic Gates**

- VTC, Delay and Sizing

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinationa

3/19/2008

## **Complementary Static CMOS (2)**

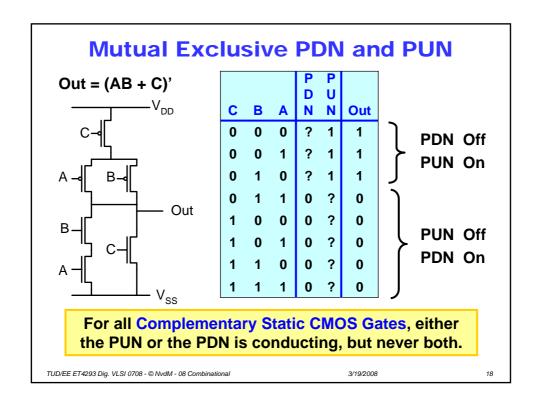

- Conduction of PUN and PDN must be mutually exclusive

- PUN is dual (complement) network of PDN series ⇔ parallel nmos ⇔ pmos

- Complementary gate is inverting

- No static power dissipation

- Need 2N transistors for N-input gate

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

19

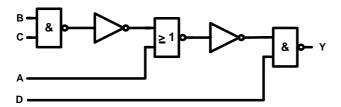

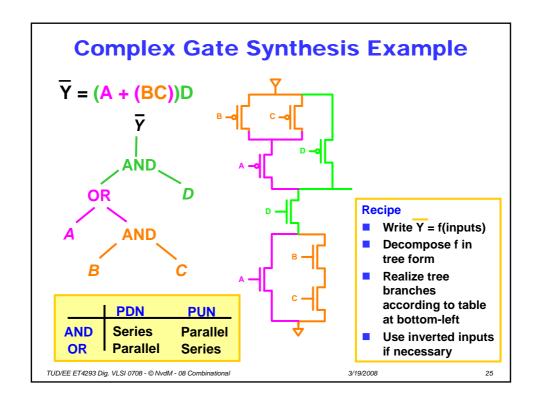

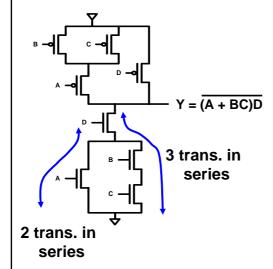

## Implementation of Combinational Logic

- How van we construct an arbitrary combinational logic network in general, using NMOS and PMOS transistors (using Complementary static CMOS)?

- Example: Y = (A + BC)D

- Remember: only inverting gates available

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinationa

3/19/2008

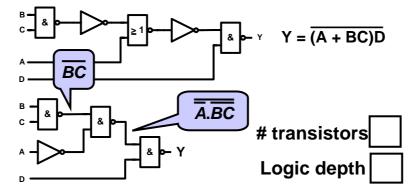

## Implementation of Combinational Logic

- Example: Y = (A + BC)D

- Remember: only inverting gates available

- Logic depth: number of gates in longest path ⇒ DELAY

# transistors

logic depth

Q: Can this be improved?

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

21

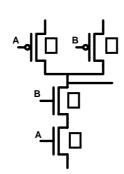

## **Improved Gate Level Implementation**

■ Using DeMorgan  $A + BC = \overline{A.BC}$

Q: Can this be further improved?

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

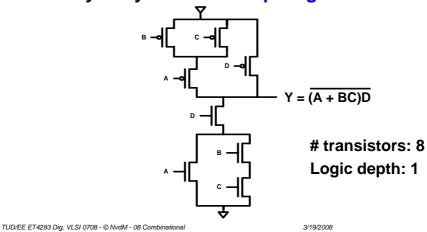

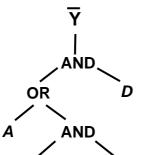

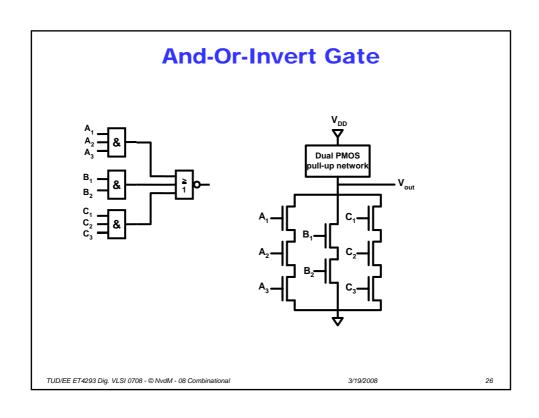

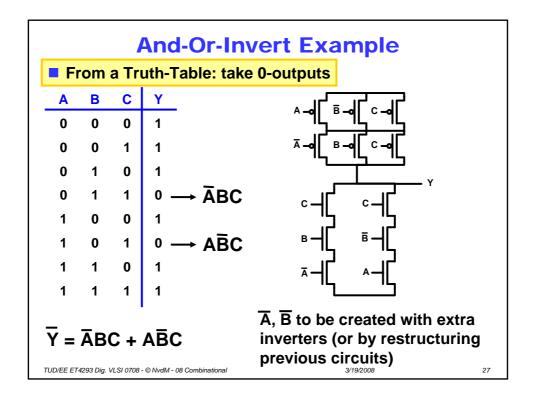

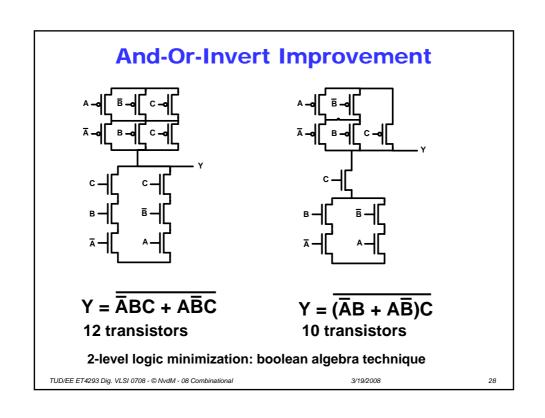

## **Complex CMOS Logic Gates**

- Restriction to basic NAND, NOR etc. not necessary

- Easy to synthesize complex gates

**How to Synthesize Complex Gates**

$$Y = \overline{(A + BC)D}$$

Using tree representation of Boolean function

- Operator with branches for operands

- As a series-parallel network

|     | PDN      | PUN      |

|-----|----------|----------|

| AND | Series   | Parallel |

| OR  | Parallel | Series   |

3/19/2008

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

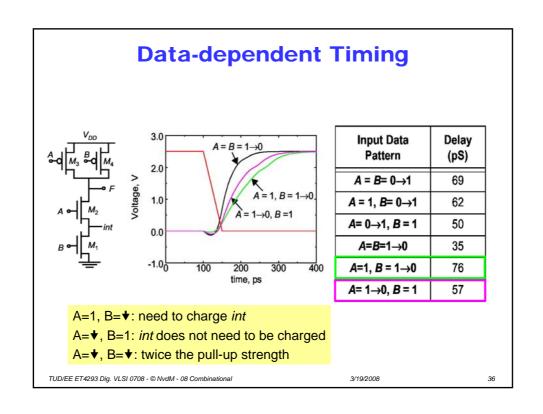

## **CMOS Complex Gate Sizing**

- Function of gate independent of transistor sizes: ratioless

- But current-drive capability (timing) depends on transistor sizes

- Worst-case currentdrive depends on number of transistors in series

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

20

## **CMOS Complex Gate Sizing**

- Assume all transistors will have mininum length L

- Determine  $W_n$  for PDN transistor of inverter that would give the desired 'drive strength'

- For each transistor in PDN of complex gate do the following:

- Determine the length l of the longest PDN chain in which it participates

- Set  $W = l W_n$

- Repeat this procedure for PUN, using  $W_p$  for PUN transistor of inverter.

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

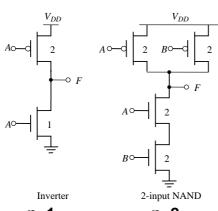

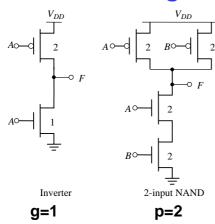

## **Gate Sizing**

- W/L ratios

- what are the W/L of 2-input NAND for same drive strength?

0-th order calculation

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

31

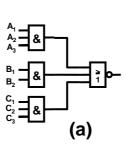

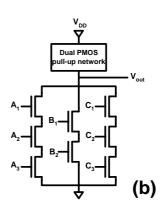

## **Exercise**

#### **Exercise:**

- Perform gate sizing of (a) for nominal drive strength equal to that of min size inverter, assume PU/PD = 3

- Determine PUN of (b)

- Perform gate sizing of (b) for same drive strength (same PU/PD)

- Compare sum of gate areas in (a) and (b). Note: area ~ width

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

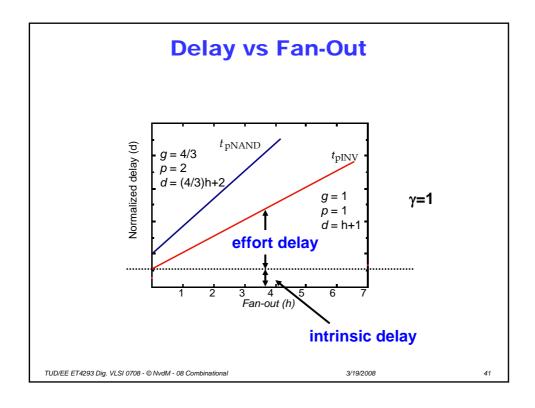

## **Logical Effort Methodology**

Inverter delay:

$$t_{p} = t_{p0} \left( 1 + \frac{f}{\gamma} \right)$$

Gate delay:

$$t_{p} = t_{p0} \left( p + \frac{gf}{\gamma} \right) = t_{p0} \left( p + \frac{h}{\gamma} \right)$$

#### **Logical Effort Methodology Definitions:**

- ratio of intrinsic delay compared to inverter

- electrical effort ratio between C<sub>load</sub> and C<sub>in</sub>

- logical effort ratio of drive strength for same size g

- gate effort  $-h = f \cdot g$

[Logical Effort - Designing Fast CMOS Circuits, Sutherland, Sproul, Harris]

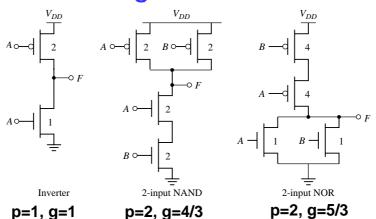

## **Intrinsic Delay**

p=1

p=2

- p ratio of intrinsic delay compared to inverter

- p is ratio of output capacitances if gate is sized for identical drive strength

is (2+2+2)/(2+1) = 2

$$t_{p} = t_{p0} \left( p + \frac{gf}{\gamma} \right)$$

## **Logical Effort**

- g logical effort ratio of drive strength for same size

- g same as ratio of input cap for same strength

- $g_{nand}$  is (2+2)/(2+1) = 4/3

$$t_{p} = t_{p0} \left( p + \frac{gf}{\gamma} \right)$$

- Logical effort: a multi-input gate has more input cap compared to inverter for same drive strength

- Needs to be corrected for in delay calculations

- Can be done by inclusion in electrical effort: replace f by g.f

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

39

## **Logical Effort**

- p ratio of intrinsic delay compared to inverter

- g logical effort ratio of drive strength for same size

- p, g independent of sizing, only topology of circuit

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

## **Add Branching Effort**

Branching effort:

$$b = \frac{C_{on-path} + C_{off-path}}{C_{on-path}}$$

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

## **Multistage Networks**

$$Delay = \sum_{i=1}^{N} (p_i + g_i \cdot f_i)$$

#### Normalized w.r.t. unit delay

Stage effort:  $h_i = g_i f_i$

Path electrical effort:  $F = C_{out}/C_{in}$

Path logical effort:  $G = g_1 g_2 ... g_N$

Branching effort:  $B = b_1 b_2 ... b_N$

Path effort: H = GFB

Path delay  $D = \sum d_i = \sum p_i + \sum h_i$

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

19/2008

43

## **Optimum Effort per Stage**

When each stage bears the same effort:

$$h^N = H$$

$$h = \sqrt[N]{H}$$

Stage efforts:  $g_1 f_1 = g_2 f_2 = \dots = g_N f_N = h$

Effective fanout of each stage:  $f_i = h/g_i$

larger fanout for simpler stages

Minimum path delay

$$\hat{D} = \sum (g_i f_i + p_i) = NH^{1/N} + P$$

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinationa

3/19/2008

## **Optimal Number of Stages**

For a given load, and given input capacitance of the first gate Find optimal number of stages and optimal sizing

$$D = NH^{1/N} + Np_{inv}$$

$$\frac{\partial D}{\partial N} = -H^{1/N} \ln(H^{1/N}) + H^{1/N} + p_{inv} = 0$$

$h = H^{1/\hat{N}}$ Substitute 'best stage effort'

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

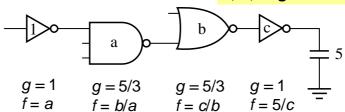

## **Example: Optimize Path**

a, b, c: gate sizes t.b.d.

Effective fanout, F = 5

$$G = \Pi g_i = 25/9$$

$$H = GFB = 125/9 = 13.9$$

$$h = H^{1/4} = 1.93$$

$$a = 1.93$$

$$b = ha/g_2 = 2.23$$

$$b = ha/g_2 = 2.23$$

$c = hb/g_3 = 5g_4/f = 2.59$

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

# Ratioed logic Pass transistor logic

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

## Ratioed Logic V<sub>OL</sub> Computation

I<sub>Dn</sub> (linear) = I<sub>Dp</sub> (saturation)

**Exercise:** verify these assumptions/steps

$$k_n \left( (V_{DD} - V_{Tn}) V_{OL} - \frac{V_{OL}^2}{2} \right) = k_p \left( (-V_{DD} - V_{Tp}) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right)$$

Ignore quadratic terms (they are relatively small)

$$k_n(V_{DD} V_{Tn})V_{OL} \approx k_p(-V_{DD} V_{Tp})V_{DSAT}$$

Ignore, because approximately equal

$$V_{OL} pprox rac{k_p}{k_n} |V_{DSAT}| pprox rac{\mu_p W_p}{\mu_n W_n} |V_{DSAT}|$$

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

49

## **Pass-transistor and Pass-gate circuits**

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinationa

3/19/2008

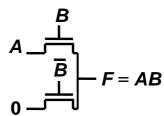

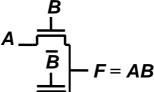

## **Pass Transistor Logic**

- Save area, capacitances

- Need complementary inputs (extra inverters)

#### **But remember:**

§ 6.2.3

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

51

## **Pass Transistor Logic**

- Save area, capacitances

- Need complementary inputs (might mean extra inverters)

- Reduced V<sub>OH</sub>, noise margins 0

- $V_{OH} = V_{DD} \left(V_{Tno} + \gamma \left( \left( \sqrt{|2\phi_f| + V_{OH}} \right) \sqrt{|2\phi_f|} \right) \right)$

- Static dissipation in subsequent static inverter/buffer

- Disadvantages (and advantages) may be reduced by complementary pass gates (NMOS + PMOS parallel)

Exercise: Why is there static dissipation in next conventional gate?

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

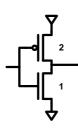

#### **Pass Gates**

Remedy: use an N-MOS and a P-MOS in parallel

- Pass gates eliminate some of the disadvantages of simple pass-transistors

- But also some of the advantages

- Design remains a trade-off!

Pass-gate a.k.a. Transmission-gate

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

53

#### **Exercise**

■ Discuss what happens when you connect the output of a single pass-transistor (not a pass-gate) to the input of another pass-transistor stage (i.e. the gate of another pass-transistor). Why should you never use such a circuit?

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008

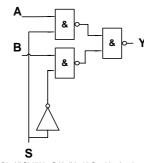

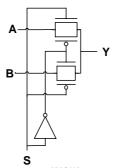

## **Pass Transistor Logic**

- Most typical use: for multiplexing, or path selecting

- Assume in circuit below it is required to either connect A or B to Y, under control by S

- Y = AS + BS' (S' is easier notation for S-bar = S-inverse = S)

- Y = ((AS)' (BS)')' allows realization with 3 NAND-2 and 1 INV: 14 transistors

- Pass gate needs only 6 (or 8) transistors (see also Katz, section 4.2)

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinationa

## **Summary**

- Conventional Static CMOS basic principles

- Complementary static CMOS

- Complex Logic Gates

- VTC, Delay and Sizing

- Ratioed logic

- Pass transistor logic

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 08 Combinational

3/19/2008