#### **Interconnect**

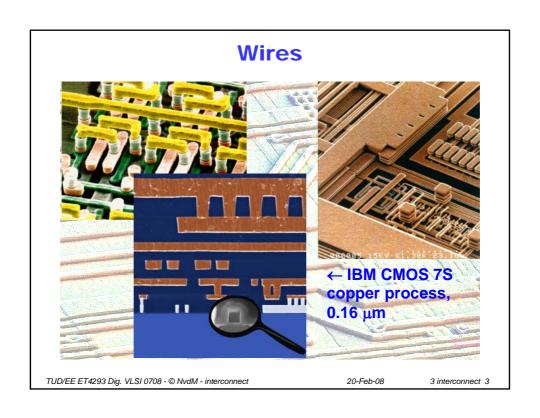

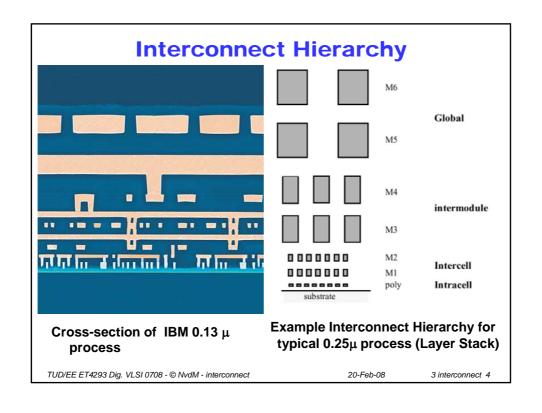

- Wires are not ideal interconnections

- They may have non-negligible capacitance, resistance, inductance

- These are called wire parasitics

- Can dominate performance of chip

- Must be accounted for during design

- Using approximate models

- Detailed post-layout verification also necessary

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

## **Outline**

- Capacitance Area/perimeter model, coupling

- Resistance

**Sheet resistance**

Interconnect delayDelay metrics, rc delay, Elmore delay

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

3 interconnect 5

#### Capacitance

■ Area/perimeter model, coupling

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

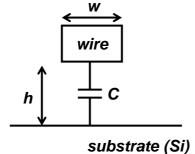

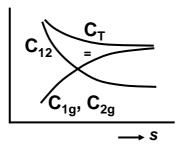

# **Wire Capacitance - Parallel Plate**

$$C = \frac{\varepsilon_0 \varepsilon_r W I}{d}$$

$$\frac{C}{I} = \varepsilon_0 \varepsilon_r \, \frac{w}{h}$$

$$\epsilon_0 = 8.85 \text{ pF/m}$$

$$\varepsilon_{\rm r}$$

= 3.9 (SiO<sub>2</sub>)

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

3 interconnect 7

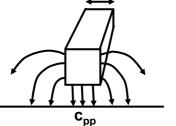

# **Wire Capacitance - Fringing Fields**

$$c_{wire} = c_{fringe} + c_{pp} = \frac{2\pi\varepsilon_{di}}{\log(t_{di}/H)} + \frac{w\varepsilon_{di}}{t_{di}}$$

- Works reasonably well in practice

- Not directly applicable for interconnects with varying widths

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

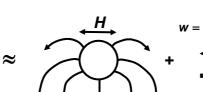

# Wire Capacitance - Area/Perimeter Model

- Ca was calculated with modified wire width

- Formula inapplicable for irregular interconnects (nonconstant width)

3 interconnect 9

■ More practical approximation

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

| $C = A \times C_a + P \times C_p$ | units          | alternative              |

|-----------------------------------|----------------|--------------------------|

| A = Area                          | m²             | $\mu m^2$                |

| C <sub>a</sub> = Area capacitance | F/m²           | aF/μm²                   |

| P = Perimeter                     | m              | $\mu$ <b>m</b>           |

| $C_p$ = Perimeter capacitance     | F/m            | aF/μm                    |

| 1 <i>μ</i> \$                     | $C = \times C$ | $C_a + \prod \times C_p$ |

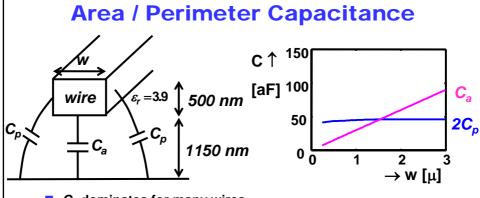

Area / Perimeter Capacitance

Model

$C = \times C_a + \times C_p$

**Question:** How to derive  $C_a, C_p$ ?

How accurate is this model?

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

20-Feb-08

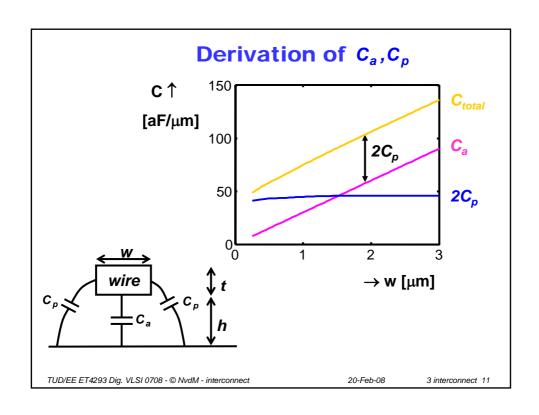

## Derivation of $C_a, C_p$

- 2D (cross-section) numerical computation (or measurement)

- $\mathbf{C}_{I}$ : total wire capacitance per unit length

- $\mathbf{C}_a = \varepsilon_0 \varepsilon_r / h$

- C<sub>p</sub> depends on t, h → determined by technology, layer

- C<sub>p</sub> would depend slightly on w (see previous graph), this dependence is often ignored in practice

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

- C<sub>p</sub> dominates for many wires

- C<sub>p</sub> may not be neglected

- **A** constant value for  $C_p$  is usually a good approximation

- lacksquare  $C_p$  is sometimes called  $C_f$  (fringe capacitance)

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

3 interconnect 13

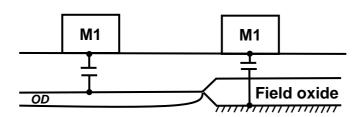

## **Interconnect Capacitance Design data**

- See Table 4.2 (or inside backside cover)

- Example: M1 over Field vs. M1 over Active (hypothetical)

| M1 over Active | M1 over Field | Unit             |

|----------------|---------------|------------------|

| $C_a = 41$     | $C_a = 30$    | aF $/\mu$ m $^2$ |

| $C_p = 47$     | $C_p = 40$    | aF $/\mu$ m      |

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

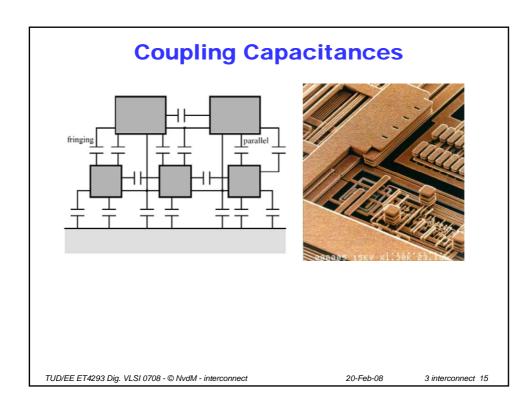

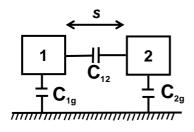

## **Coupling Capacitances (2)**

- ${f C}_{\rm T} = {f C}_{1g} + {f C}_{12} = {f C}_{2g} + {f C}_{12}$  fairly constant

- Use that as first order model

- Interconnect capacitance design data (e.g. Table 4.3)

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

#### **Resistance**

■ Sheet resistance

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

3 interconnect 17

## **Wire Resistance**

- Proportional to I

- Inversely proportional to w and t (cross-sectional area)

- Proportional to ρ: specific resistance, material property [Ωm]

- $R = \rho I/wt$

- Aluminum:  $ρ = 2.7x10^{-8} Ωm$ Copper:  $ρ = 1.7x10^{-8} Ωm$

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

#### **Sheet Resistance**

- $= R = \rho I/wt$

- t, ρ constant for layer, technology

- R = R I/w

- R : sheet resistance [Ω/]

resistance of a square piece of interconnect

other symbol: R<sub>s</sub>

- Interconnect resistance design data e.g. Table 4.5 (or inside back-cover)

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

3 interconnect 19

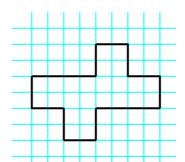

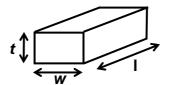

#### **Interconnect Resistance**

- Assume  $R_{\square}$  = 40  $\Omega$

- **E**stimate the resistance between A and B in the wire below.

$R_{CD} \approx 11 \times 40 = 440 \Omega$

Engineering is about making controlled approximations to something that is too complicated to compute exactly, while ensuring that the approximate answer still leads to a working (functional, safe, ...) system

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

## **Exercise**

An interconnect line is made from a material that has a resistivity of  $\rho=4~\mu\Omega$ -cm. The interconnect is 1200 Å thick, where 1 Angstrom (Å) is  $10^{\text{-}10}~\text{m}$ . The line has a width of 0.6  $\mu\text{m}$ .

- a) Calculate the sheet resistance  $R_{\square}$  of the line.

- b) Find the line resistance for a line that is 125  $\mu m$  long.

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

3 interconnect 21

#### Interconnect delay

■ Delay metrics, rc delay, Elmore delay

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

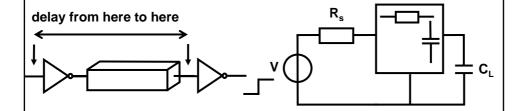

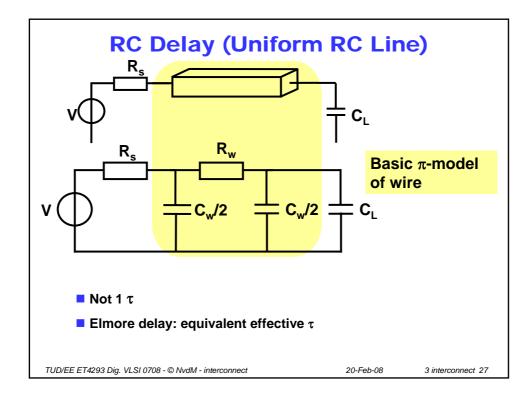

## **Delay**

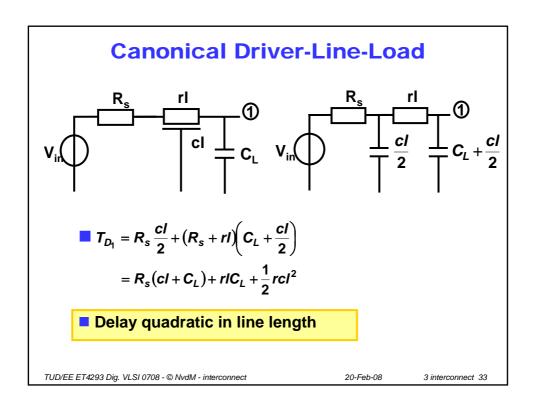

- Model driver as linearized Thevenin source V, R<sub>s</sub>, assume step input

- Model load as C<sub>L</sub>

- Wire is an RC network (two-port)

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

3 interconnect 23

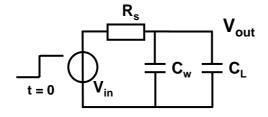

## **Wire Capacitance**

Assume wire behaves purely capacitive

$$(C_w + C_L)\frac{dV_{out}}{dt} + \frac{V_{out} - V_{in}}{R_s} = 0$$

$$V_{out} = V_{in} - \tau \frac{dV_{out}}{dt}$$

$\tau = R_s(C_w + C_L)$

$$V_{out} = \left(1 - e^{-t/\tau}\right) V_{in}$$

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

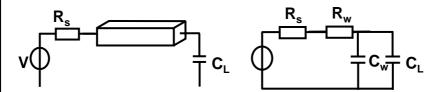

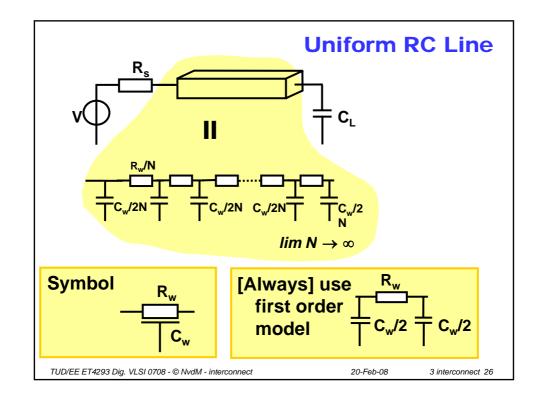

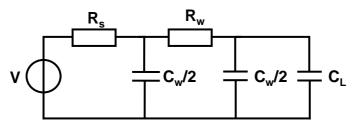

## **Wire Resistance**

Now, assume wire capacitance and resistance

- Not a a good model

- R and C are distributed along the wire

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

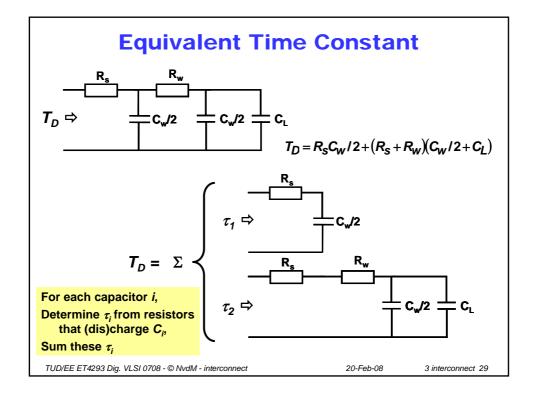

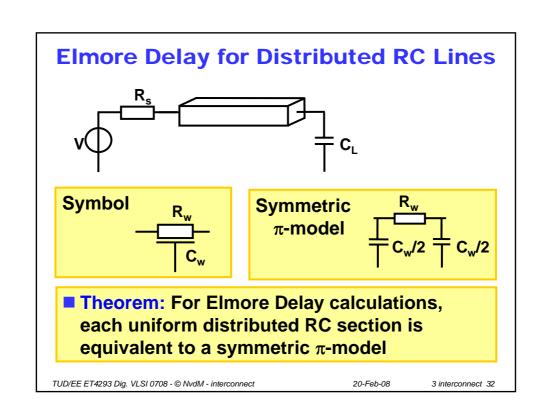

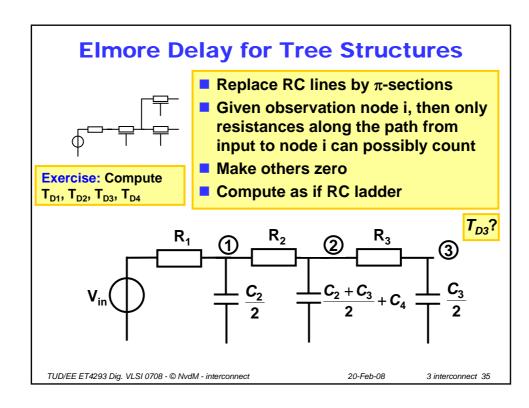

- Multiple time-constants

- Need for one "equivalent" number

- Offered by *Elmore Delay T<sub>D</sub>*

$$T_D = R_S C_W / 2 + (R_S + R_W)(C_W / 2 + C_L)$$

■ Effective "one number" model for delay

How to compute Elmore Delay?

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

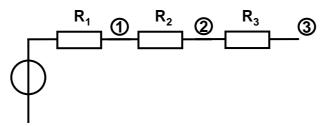

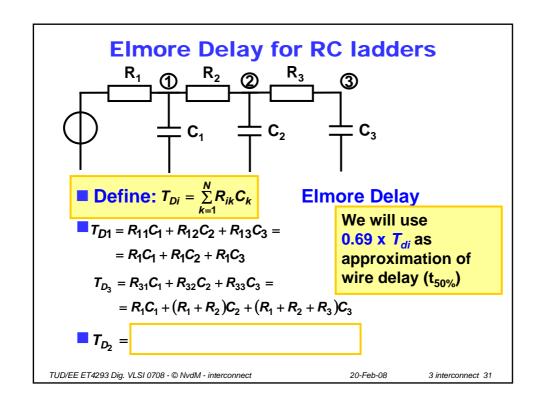

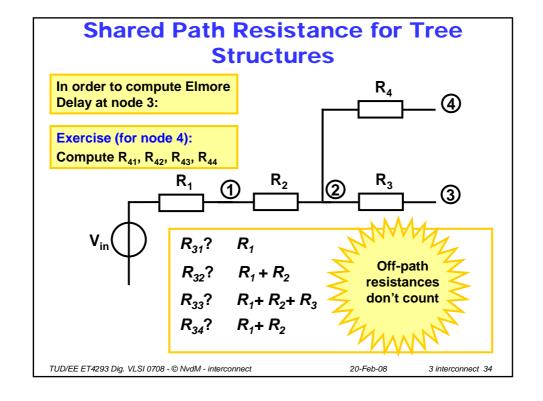

#### **Shared Path Resistance**

- Define:  $R_{ii}$  = Resistance from node i to input

- **Example:**  $R_{11} = R_1$   $R_{22} = R_1 + R_2$   $R_{33} = R_1 + R_2 + R_3$

- Define:  $R_{ik}$  = Shared path resistance to input for node i and k

- $R_{12}=R_1$   $R_{13}=R_1$   $R_{23}=$

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08

## **Summary**

- CapacitanceArea/perimeter model, coupling

- ResistanceSheet resistance

- Interconnect delayDelay metrics, rc delay, Elmore delay

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - interconnect

20-Feb-08