| Р | 10.1               | Introduction                                     | 492       |

|---|--------------------|--------------------------------------------------|-----------|

| ı | 10.2               | Timing Classification                            | 492 – 495 |

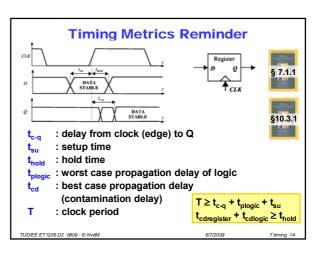

| Р | 10.3.1             | Synchronous Timing Basics                        | 495 – 500 |

| 1 |                    | Clock Jitter                                     | 500       |

| ı |                    | The combined impact of Skew and Jitter           | 501 – 502 |

| 1 | 10.3.2             | Sources of Skew and Jitter                       |           |

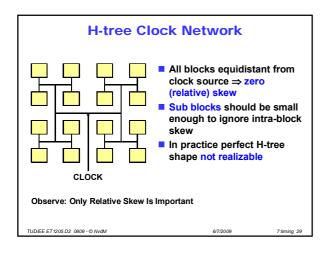

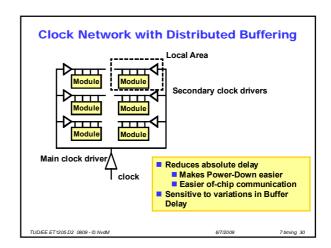

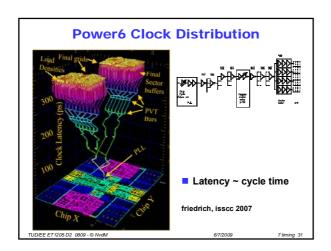

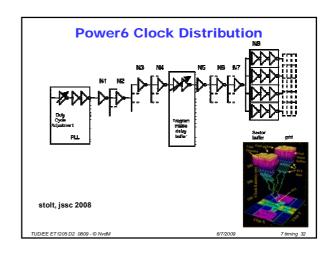

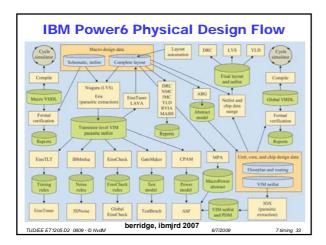

| ı | 10.3.3             | Clock Distribution Techniques                    |           |

| 0 | 10.3.4             | Latch-Based Clocking                             | 516 – 518 |

| 0 | 10.4-10.7          | Self-Timed Circuit Design – Future<br>Directions | 519 – 551 |

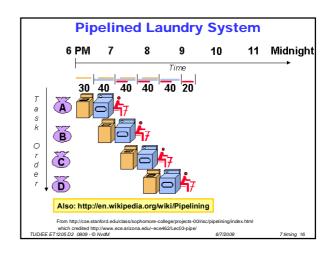

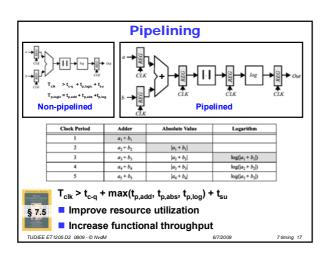

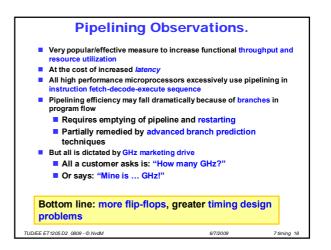

| Р | 7.5 – 7.5.1<br>(!) | Pipelining                                       | 358-361   |

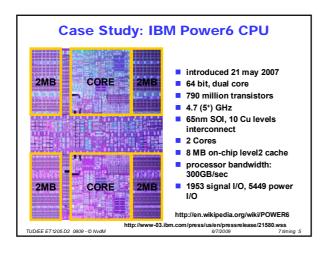

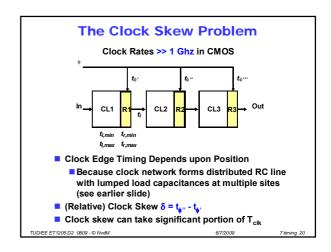

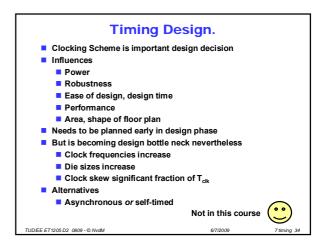

## Outline Timing Design Background and Motivation Delay variations, impact Sequential circuits, synchronous design Pipelining, metrics reminder The Clock Skew Problem Controlling Clock Skew Case Study Get basic appreciation of some system level design issues

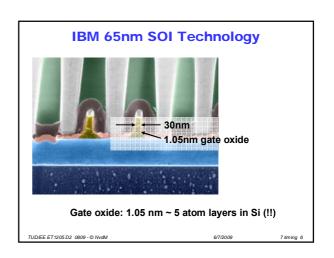

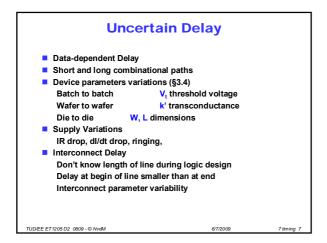

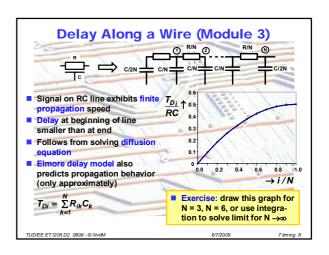

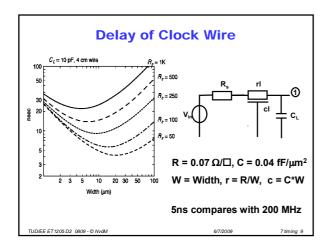

## Design of LARGE Integrated Circuits Correct signal Logic value Right level (restoring logic, ...) At right place Interconnect (R, C, L) Busses Off-chip drivers, and receivers At right time How to cope with (uncertain) delay

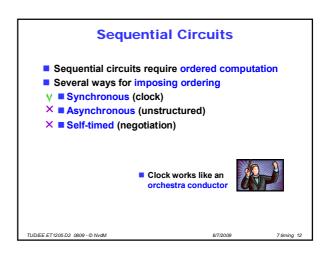

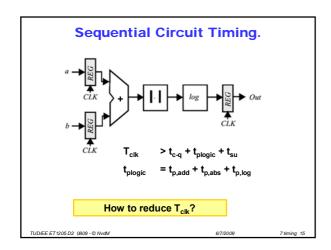

# Impact of Uncertain Delay. Combinational circuits will eventually settle at correct output values when inputs are stable Sequential circuits Have state Must guarantee storing of correct signals at correct time Require ordered computations

2

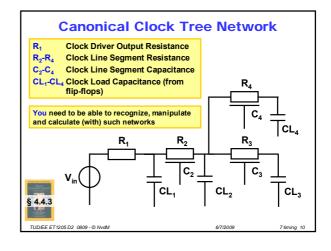

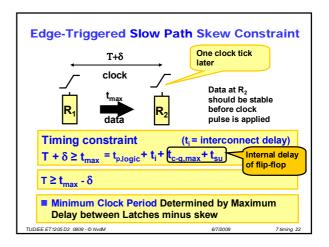

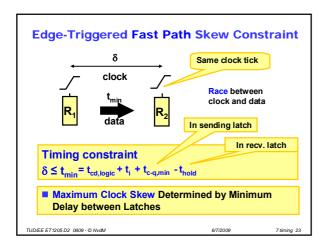

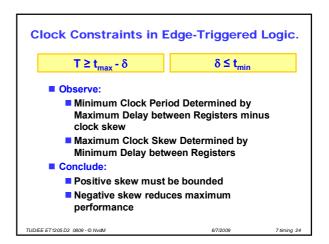

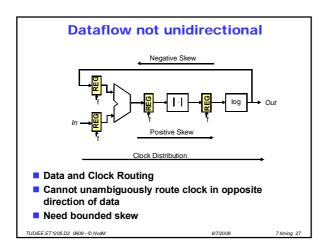

### Synchronous Design Global Clock Signal Synchronicity may be defeated by Delay uncertainty in clock signal Relative timing errors: clock skew Slow logic paths Fast logic paths fast logic paths

3

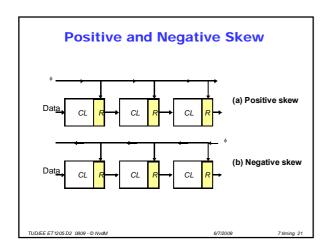

#### **Countering Clock Skew Problems**

- Routing the clock in opposite direction of data (negative skew)

- Hampers performance

- Dataflow not always uni-directional

- Maybe at sub circuit (e.g. datapath) level

- Other approaches needed at global chip-level

- Useful skew (or beneficial skew) is serious concept

- Enlarging non-overlap periods of clock [only with two-phase clocking]

- Hampers performance

- Can theoretically always be made to work

- Delay in clock network may require impractical/excessively large scheduled  $T_{\phi 12}$  to guarantee minimum  $T_{\phi 12}$  everywhere across chip

- Is becoming less popular for large high performance

#### Summary Timing Design Background and Motivation Delay variations, impact Sequential circuits, synchronous design Pipelining, metrics reminder The Clock Skew Problem Controlling Clock Skew Case Study Got basic appreciation of some system level design issues?