#### **MODULE 6**

## SEQUENTIAL ELEMENTS

| Р | 7.1   | Introduction                                                      | 326 – 327 |  |  |

|---|-------|-------------------------------------------------------------------|-----------|--|--|

| Р | 7.1.1 | Timing Metrics for Sequential Circuits                            | 327 – 328 |  |  |

| Р | 7.1.2 | Classification of Memory Elements                                 | 328 – 330 |  |  |

|   | 7.2   | Static Latches and Registers                                      | 330       |  |  |

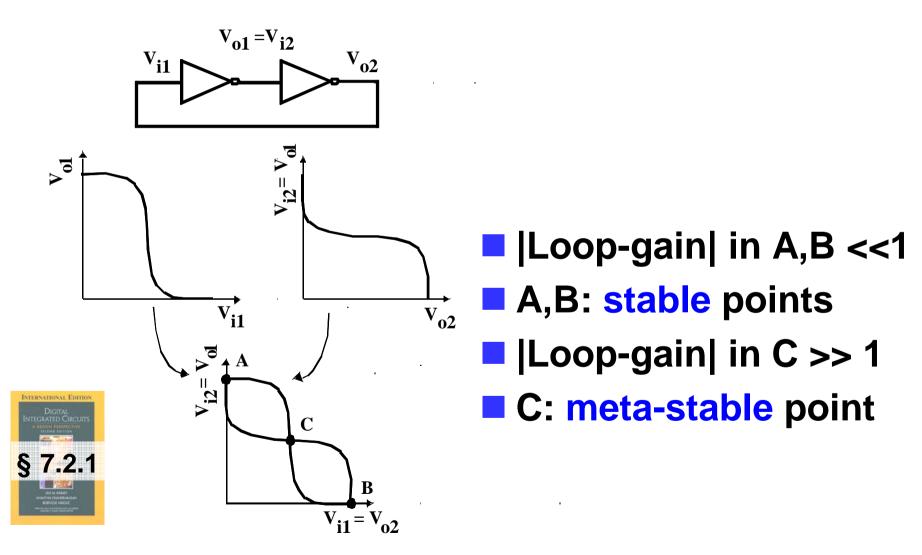

| Р | 7.2.1 | The Bistability Principle                                         | 330 – 332 |  |  |

| Р | 7.2.2 | Multiplexer-Based Latches                                         | 332 – 333 |  |  |

| Р | 7.2.3 | Master-Slave Edge-Triggered Register                              | 333 – 335 |  |  |

| I |       | Timing Properties of Multiplexer-Based Master                     | 335 – 339 |  |  |

| 0 | 7.2.4 | Low-Voltage Static Latches                                        | 339 – 341 |  |  |

| Р | 7.2.5 | Static SR Flip-Flops — Writing Data by Pure Force 341 – 3         |           |  |  |

|   | 7.3   | Dynamic Latches and Registers 344                                 |           |  |  |

|   | 7.3.1 | Dynamic Transmission-Gate Edge-Triggered Registers 344            |           |  |  |

| 0 | 7.3.2 | C2MOS — A Clock-Skew Insensitive Approach                         | 346 – 350 |  |  |

| 0 | 7.3.3 | True Single-Phase Clocked Register (TSPCR) 35                     |           |  |  |

| 0 | 7.4   | Alternative Register Styles 354 – 358                             |           |  |  |

| Р | 7.5   | Pipelining: An Approach to Optimize Sequential Circuits 358 – 360 |           |  |  |

| Р | 7.5.1 | Latch versus register based pipelines 360                         |           |  |  |

| 0 | 7.5.2 | NORA-CMOS A logic style for pipelined circuits 361 – 363          |           |  |  |

|   | 7.6   | Nonbistable Sequential Circuits                                   |           |  |  |

| P | 7.6.1 | The Schmitt Trigger                                               | 364 – 367 |  |  |

| 0 | 7.6.2 | Monostable Sequential Circuits                                    | 367 – 368 |  |  |

| I | 7.6.3 | Astable Circuits 368 – 370                                        |           |  |  |

| 0 | 7.7   | Perspective: Choosing a Clocking Strategy                         | 370 – 371 |  |  |

| Р | 7.8   | Summary                                                           | 371 – 372 |  |  |

|   | •     | ,                                                                 | •         |  |  |

#### § 7.5 Will be discussed with module 08 timing design

# **Sequential Elements - Outline**

- Background

- Timing, terminology, classification

- Static Flipflops

- Latches

- Registers

- Dynamic Flipflops

- I Latches

- I Registers

- Non-bistable elements

- Schmitt Trigger

[Sorin Cotofana]

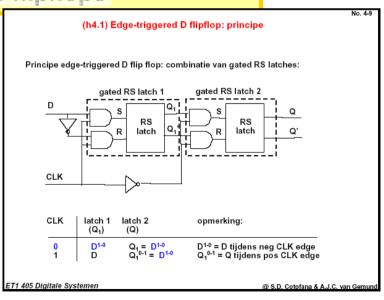

- Much of this material has already been covered in DS1 (v Genderen), Katz Section 6.1

- Here we will add transistorlevel implementation, dynamic flipflops

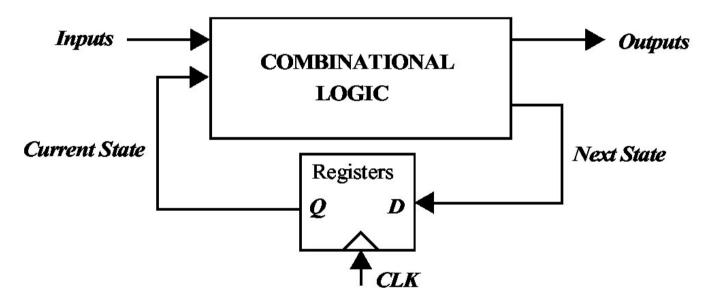

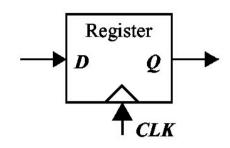

# FSM with Positive Edge Triggered Registers

- **Flip-flops provide memory/state**

- VLSI uses predominantly D-type flip-flops

### **Memory elements**

- Store a temporary value, remember a state

- Typically controlled by clock.

- May have load signal, etc.

- In CMOS, memory is created by:

- capacitance (dynamic);

- feedback (static).

Also see http://en.wikipedia.org/wiki/Flip-flop\_(electronics)

## Variations in memory elements

- Form of required clock signal.

- How behavior of data input around clock affects the stored value.

- When the stored value is presented to the output.

- Whether there is ever a combinational path from input to output.

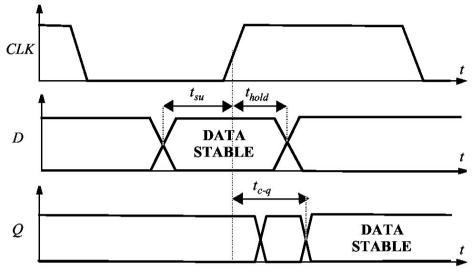

# **Timing Metrics Reminder**

t<sub>c-q</sub>: delay from clock (edge) to Q

t<sub>su</sub>: setup time

t<sub>hold</sub>: hold time

t<sub>plogic</sub>: worst case propagation delay of logic

t<sub>cd</sub>: best case propagation delay

(contamination delay)

T: clock period

$$extstyle extstyle ext$$

#### **Nomenclature**

#### **Beware for confusion**

|           | Katz (CS1)                      | Rabaey                          |  |

|-----------|---------------------------------|---------------------------------|--|

| Latch     | Level sensitive storage element | Level sensitive storage element |  |

| Register  | Group of storage elements       | Edge triggered storage element  |  |

| Flip Flop | Edge triggered storage element  | Bistable element using feedback |  |

$$CLK = CK = \phi$$

# Latches vs. Registers

#### Latch

Level-sensitive

Transparent when clock is active

Clock active high: positive latch

Clock active low: negative latch

Faster, smaller

## Register

**Edge-triggered**

Input and output isolated

Sampling on 0 → 1 clock: positive edge triggered

Sampling on 1 → 0 clock: negative edge triggered

Safer

# Static vs. Dynamic Memory Elements.

#### **Static**

Operate through positive feedback

Preserve state as long as power is on

Can work when clock is off

More robust

# **Dynamic**

**Store charge on** (parasitic) capacitor

Charge leaks away (in milliseconds)

Clock must be kept running (for periodic refresh)

Faster, smaller

Rabaey: bistable elements are called Flip Flops

# **Static Latches and Registers**

- Latches → can be gated or not

- Registers

### Positive Feedback: Bi-Stability

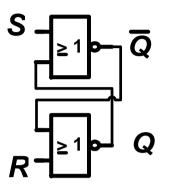

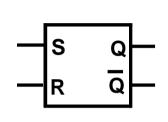

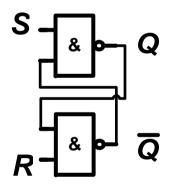

#### **SR-Latch**

| S      | R                | Q      | Q               |           |

|--------|------------------|--------|-----------------|-----------|

| 0      | 0                | Q<br>1 | Q               |           |

| 1      | 0                | 1      | 0               |           |

| 0<br>1 | 0<br>0<br>1<br>1 | 0      | 1<br>0 <b>←</b> | forbidden |

| S           | R      | Q | Q               |           |

|-------------|--------|---|-----------------|-----------|

| 1<br>0<br>1 | 1<br>1 | Q | Q               |           |

| 0           | 1      | 1 | 0               |           |

| 1<br>0      | 0      | 0 | 1<br>1 <b>←</b> | forbidden |

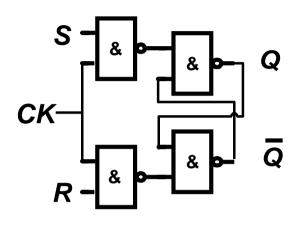

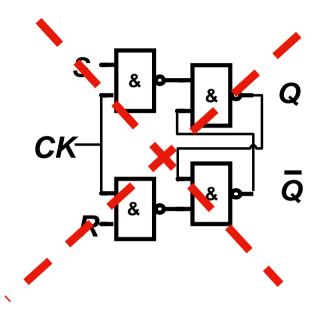

#### **Clocked SR-Latch**

- Katz: gated latch

- Positive latch (active on CK high)

- Naïve implementation

- 16 transistors

- D latch requires 9xN, 9xP

- Larger area, cost, power

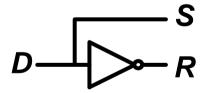

- Construction of D-latch

- D-latch, D-register most common in VLSI

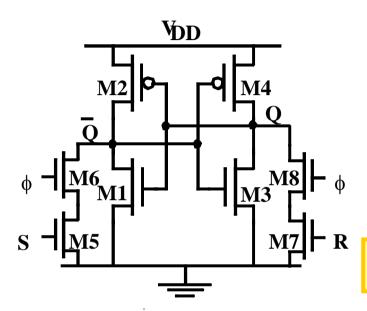

#### **CMOS Clocked SR-Latch**

$\phi = CK$

- Save 6 PMOS transistors and 2 NMOS

- D-latch requires 7 x N, 3 x P (instead of 9xN, 9xP)

- Q: Is this a ratioed design or not?

Does it consume static power?

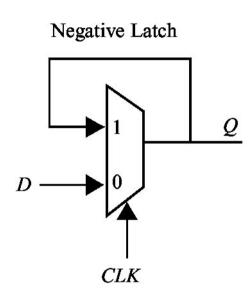

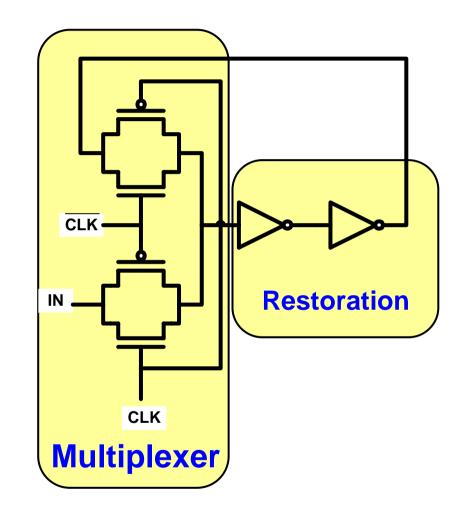

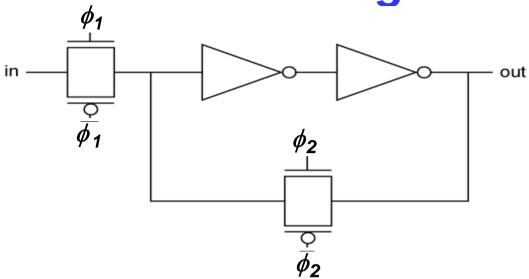

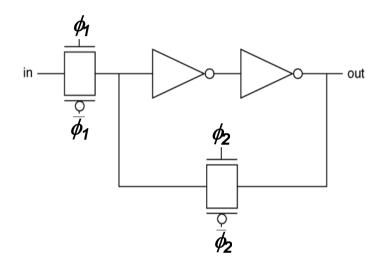

## **Multiplexer-Based Latches**

#### **Recirculating latch**

Mux-based latches much more common in modern dig. IC's

# Recirculating latch

- Quasi-static, static on one phase

- Feedback restores value

- Requires 4 x N, 4 x P, minimum size(compare 7 x N, 3 x P, non-minimum size)

- $\bullet_1$  and  $\phi_2$  inverse but should be non-overlapping

- Can suffer from charge sharing (when φ not non-overlapping)

C<sub>in</sub> and C<sub>load</sub> form communicating vessels when Output connected directly to input

# **Insensitive for Charge Sharing**

- Non ratioed

- High load to CLK

Uni-directionality of this inverter prevents coupling between Q and D

# Recirculating NMOS Latch.

- Degraded 1 at X

- Lower noise margin, higher delay, power

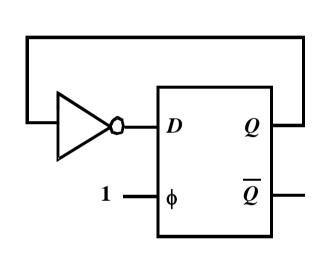

# Latch Designs can Suffer from Race Problems

# Signal can race around during $\phi = 1$

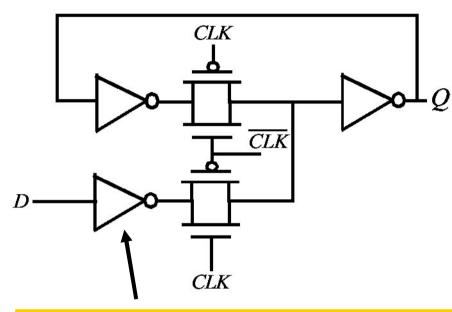

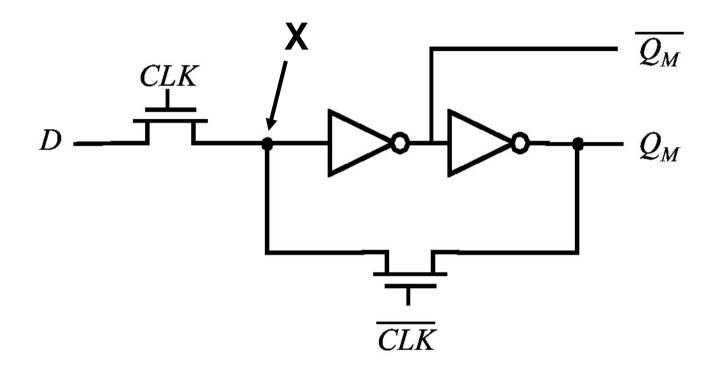

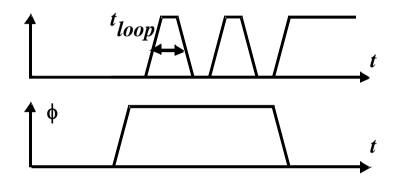

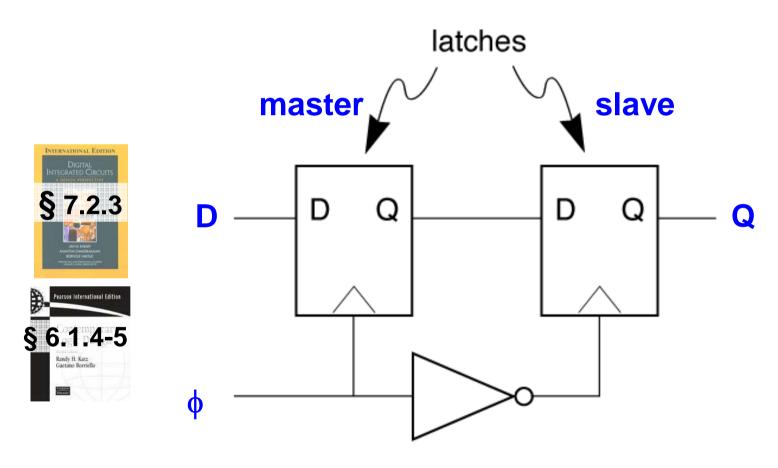

# Registers

- Not transparent—use multiple storage elements to isolate output from input.

- Master-slave, edge triggered principle

### **Master-slave operation**

$$\phi = 0$$

:

- master latch is disabled;

- slave latch is enabled,

- but master latch output is stable,

- so output does not change.

$$\phi = 1$$

:

- master latch is enabled,

- loading value from input;

- slave latch is disabled,

- maintaining old output value.

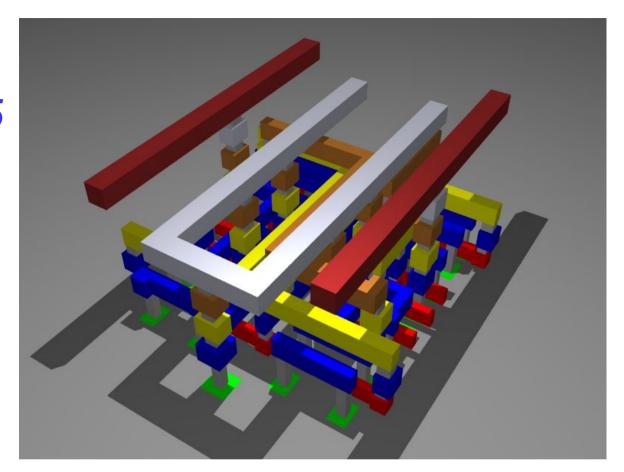

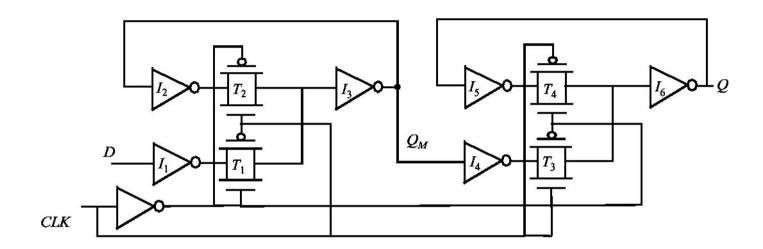

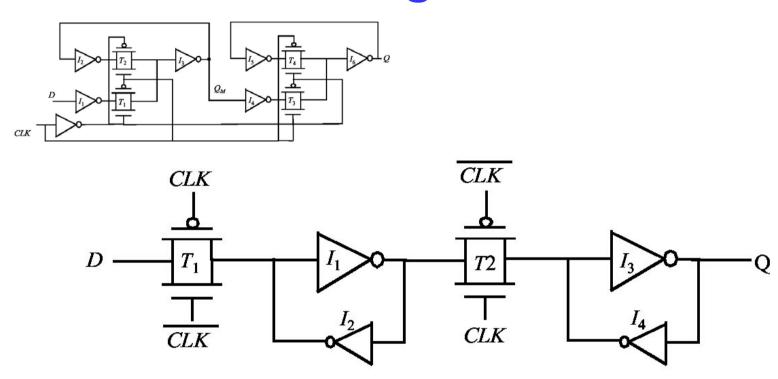

# Transistor Level Master Slave Positive Edge Triggered Register

- Robust Design

- Can eliminate I₁ and I₄, however, they make design more robust (avoid charge sharing, robust input)

- High Clock Load (8 x)

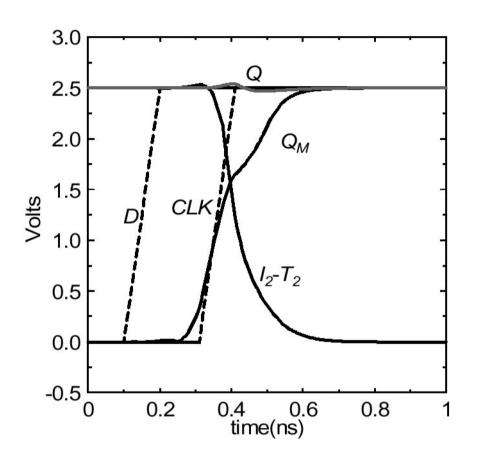

# **Set-up Time Simulation**

Slightly smaller delay between D and CLK

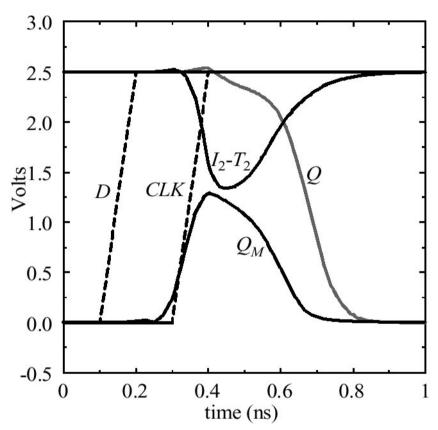

# Ratioed Reduced Clock Load Register.

- I₂ and I₄ are small, even long

- Lower clock load

- Increased design complexity

- Reduced robustness (reverse conduction)

#### **Non-bistable Elements**

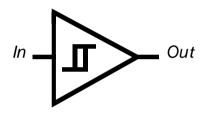

# Schmitt Trigger

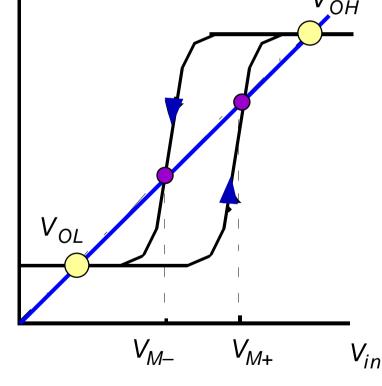

# **Schmitt Trigger**

V<sub>out</sub>

- VTC with hysteresis

- Restores signal slopes

# Noise Suppression using Schmitt Trigger

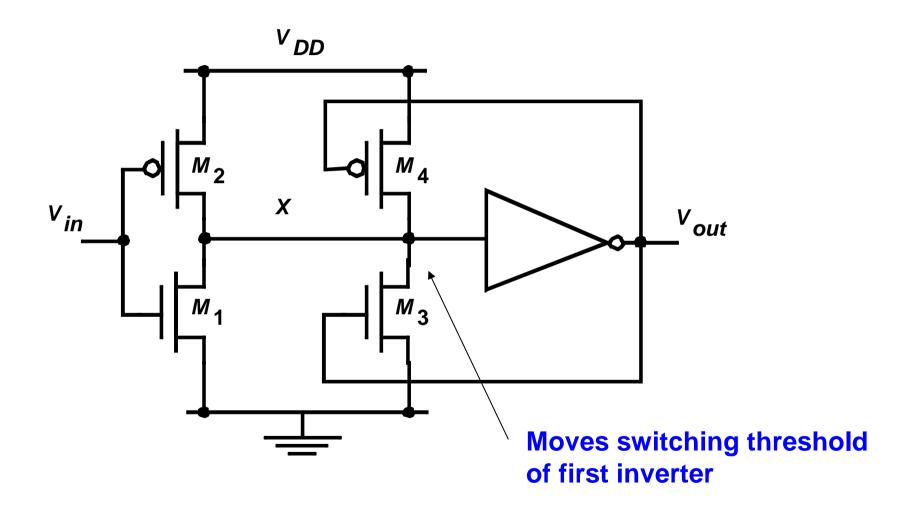

# **CMOS Schmitt Trigger**

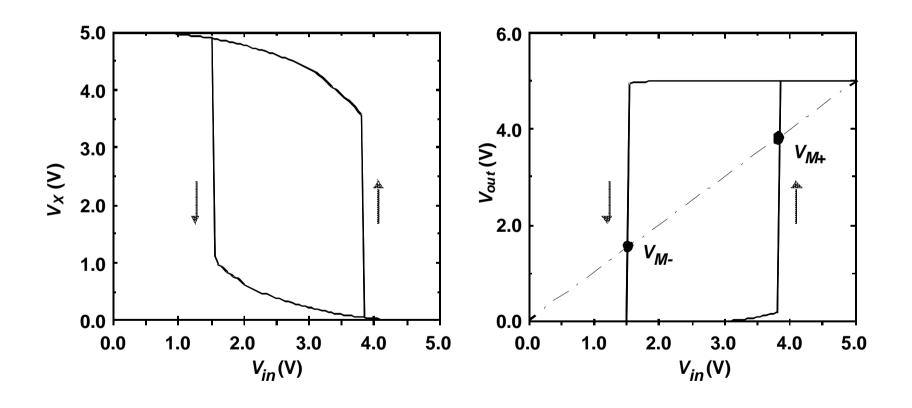

# **Schmitt Trigger Simulated VTC**

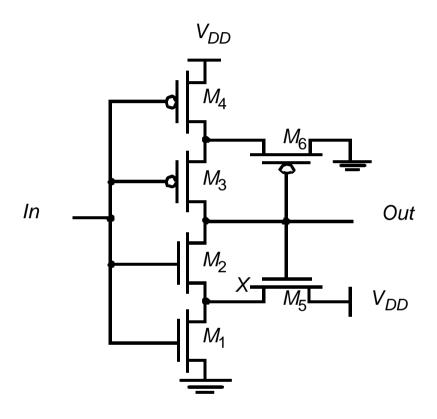

# CMOS Schmitt Trigger (2).

# **Summary**

- Background

- Timing, terminology, classification

- Static Flipflops

- Latches

- Registers

- Dynamic Flipflops

- latches

- **II** Registers

- Non-bistable elements

- Schmitt Trigger