| Course Material for Combinational |                                                                                                                            |                                                  |           |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------|--|

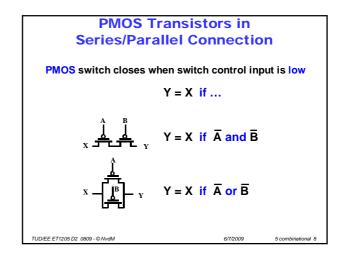

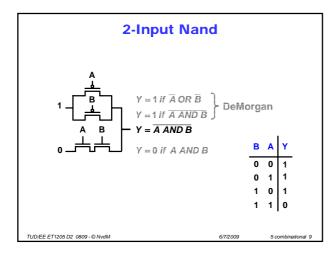

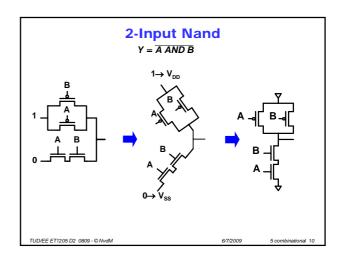

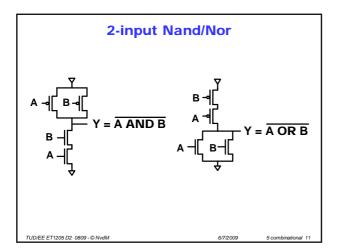

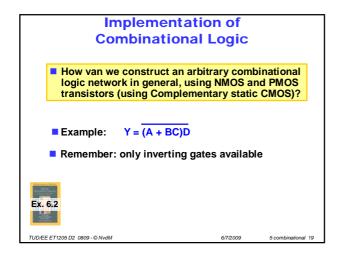

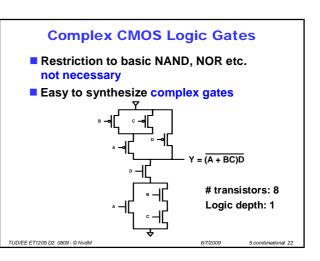

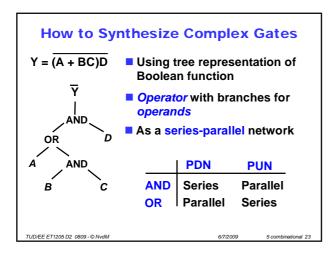

| E                                 | Extra: Slides about how to implement a static combinational gate<br>with NMOS/PMOS transistors, given the Boolean function |                                                  |           |  |

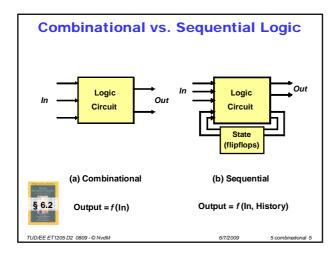

| Р                                 | 6.1                                                                                                                        | Introduction                                     | 236       |  |

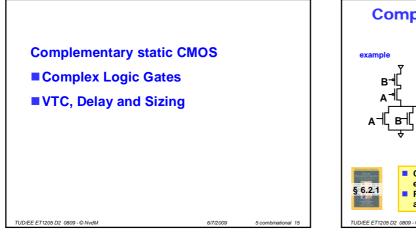

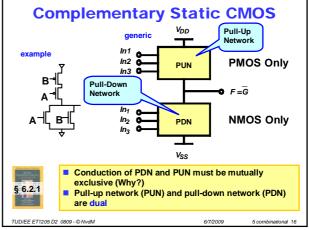

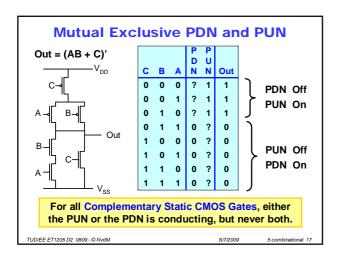

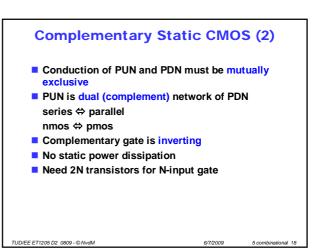

| Ρ                                 | 6.2                                                                                                                        | Static CMOS Design                               | 236 - 237 |  |

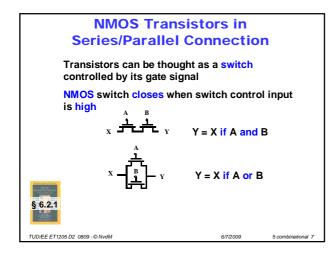

| Ρ                                 | 6.2.1                                                                                                                      | Complementary CMOS                               | 237 – 242 |  |

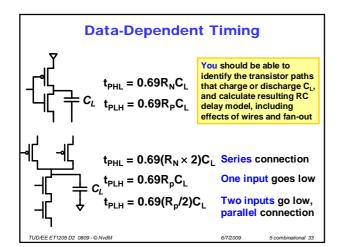

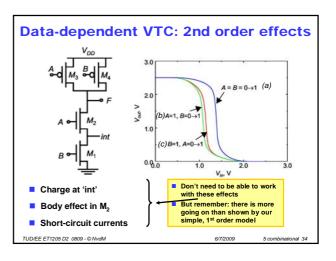

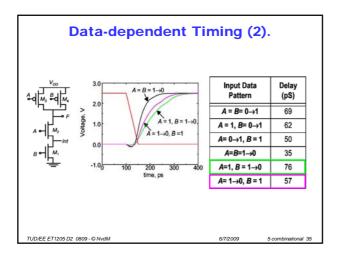

| I                                 |                                                                                                                            | Propagation Delay of Complementary CMOS gates    | 242 - 249 |  |

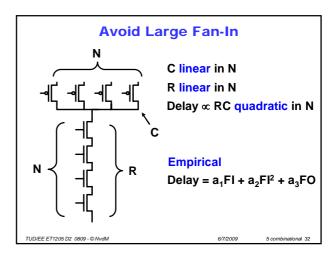

| I                                 |                                                                                                                            | Design Techniques for large fan-in               | 249 – 251 |  |

| 0                                 |                                                                                                                            | Optimizing performance in combinational networks | 251 – 257 |  |

| 0                                 |                                                                                                                            | Power consumption in CMOS logic gates            | 257 - 263 |  |

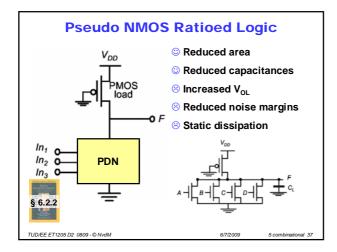

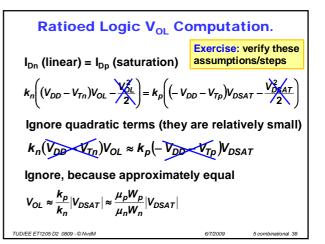

| Р                                 | 6.2.2                                                                                                                      | Ratioed Logic                                    | 263 - 267 |  |

| I                                 |                                                                                                                            | How to build even better loads                   | 267 - 268 |  |

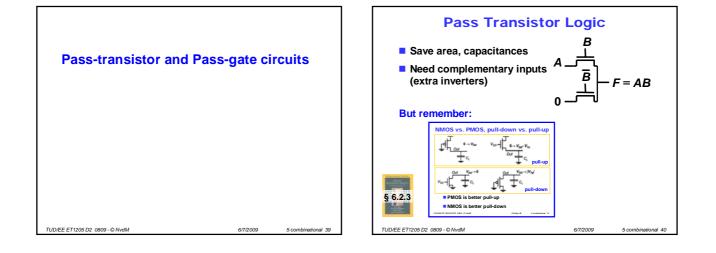

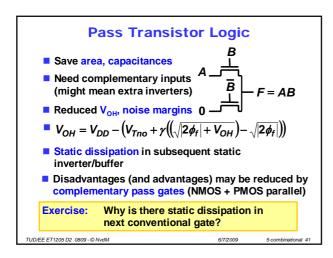

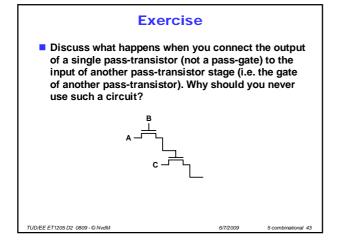

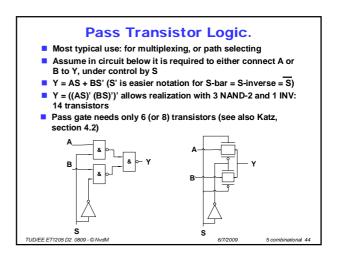

| Ρ                                 | 6.2.3                                                                                                                      | Pass-transistor basics                           | 269 - 270 |  |

| I.                                |                                                                                                                            | Example 6.10                                     | 271 – 272 |  |

| 0                                 |                                                                                                                            | Diversen                                         | 272 – 277 |  |

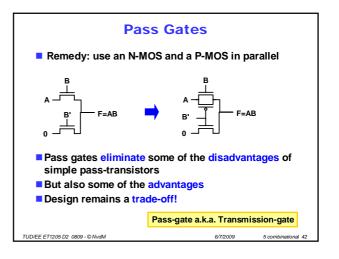

| Р                                 |                                                                                                                            | Solution 3: Transmission gate logic              | 277 – 280 |  |

| I                                 |                                                                                                                            | Rest of § 6.2.3                                  | 280 - 284 |  |

| I                                 | 6.3                                                                                                                        | Dynamic CMOS Design                              |           |  |

| I.                                | 6.3.1                                                                                                                      | Dynamic Logic: Basic Principles                  | 284 - 286 |  |

| 1                                 | 6.3.2                                                                                                                      | Speed and Power Dissipation of Dynamic Logic     | 287 – 290 |  |

| I                                 | 6.3.3                                                                                                                      | Signal Integrity Issues in Dynamic Design        | 290 – 295 |  |

| 0                                 | 6.3.4                                                                                                                      | Cascading Dynamic Gates                          | 295 - 303 |  |

| 0                                 | 6.4                                                                                                                        | Perspectives                                     | 303 - 306 |  |

| Ρ                                 | 6.5                                                                                                                        | Summary                                          | 306 - 307 |  |

| UD/EE                             | ID/EE ET1205 D2 0809 - © NvdM 6/7/2009 5 combinational                                                                     |                                                  |           |  |