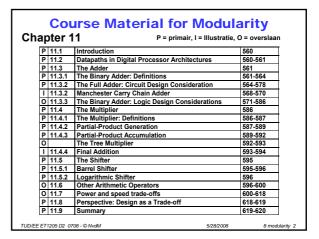

## MODULE 8 MODULARITY 5.D2 0708-© NveIM 528,2008 8 modularity 1

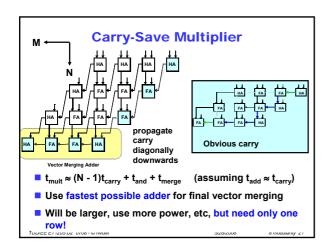

## Multipliers — Summary. Optimization Goals Different Vs Binary Adder Once Again: Identify Critical Path Other possible techniques Logarithmic versus Linear (Wallace Tree Mult) Data encoding (Booth) Pipelining GLIMPSE AT SYSTEM LEVEL OPTIMIZATION

## **VLSI** Design

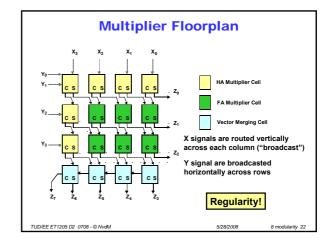

- Select right structure

- Determine and optimize critical timing path for speed

- Optimize rest for area (cost) and/or power and/or design time

- Consider layout aspects

Regularity and modularity are a VLSI designer's best friends

TUD/EE ET1205 D2 0708 - © NvdM

/28/2008

3 modularity 3

## **Summary**

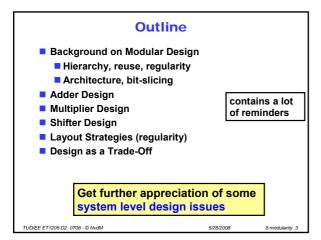

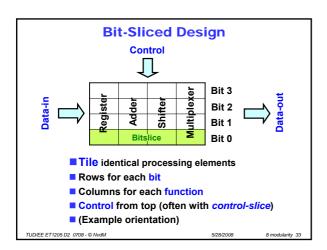

- Background on Modular Design

- Hierarchy, reuse, regularity

- Architecture, bit-slicing

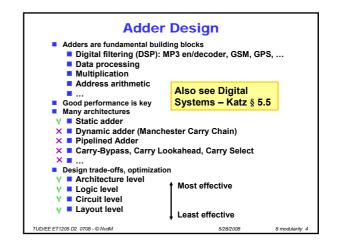

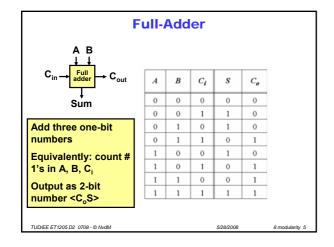

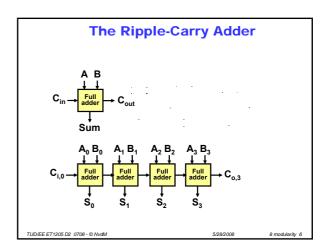

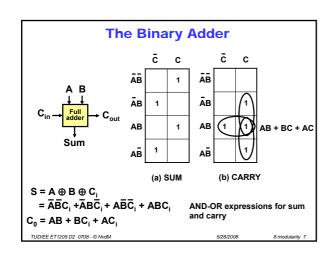

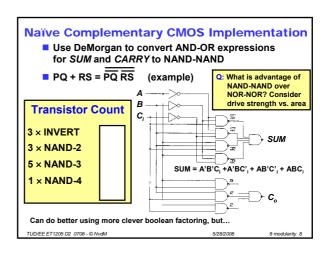

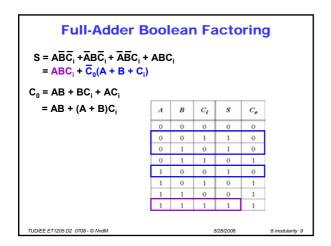

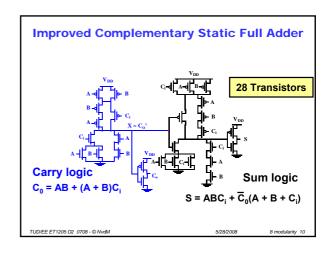

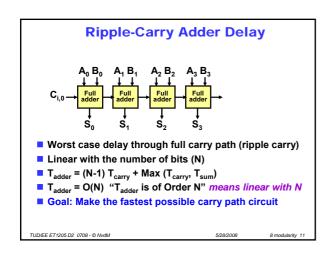

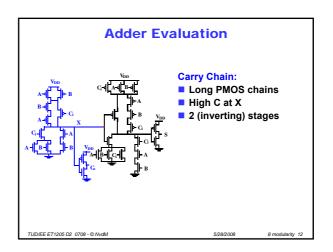

- Adder Design

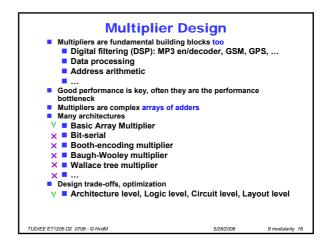

- Multiplier Design

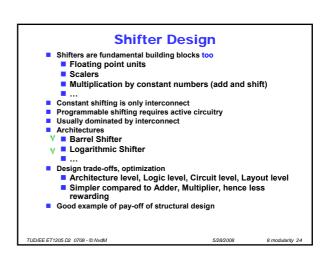

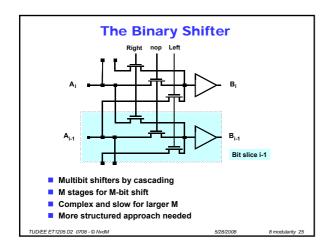

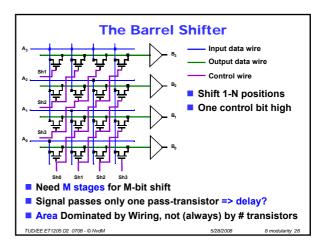

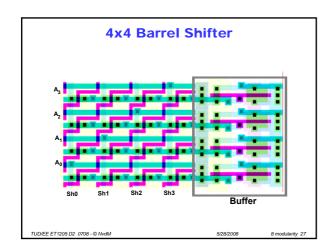

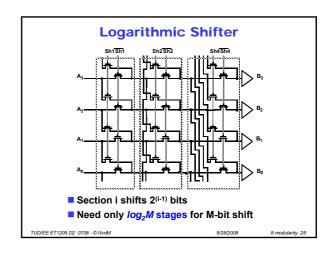

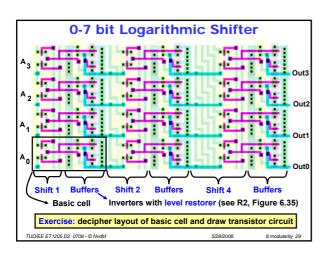

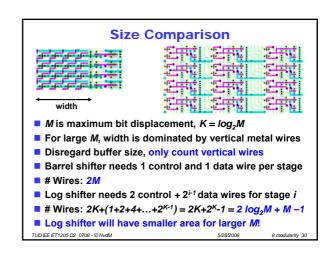

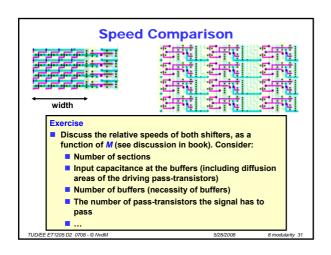

- Shifter Design

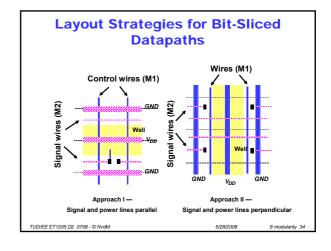

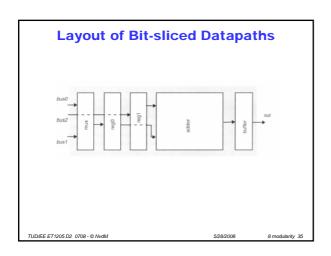

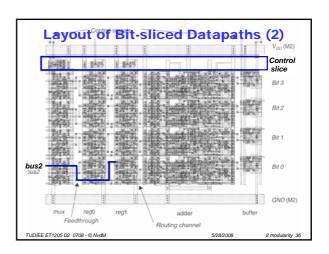

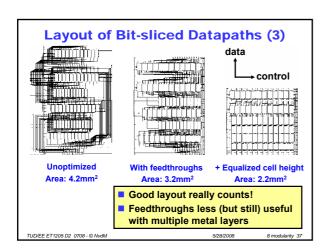

- Layout Strategies (regularity)

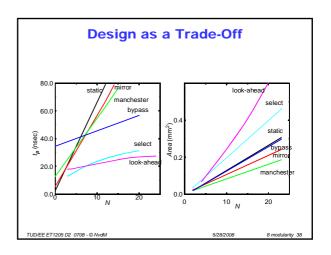

- Design as a Trade-Off

Got further appreciation of some system level design issues?

TUD/EE ET1205 D2 0708 - © NvdM

8/2008 8 r