| Р | 10.1               | Introduction                                     | 492       |

|---|--------------------|--------------------------------------------------|-----------|

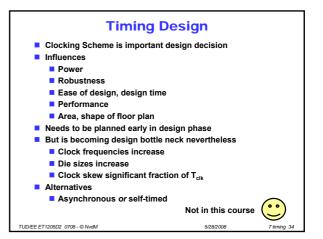

| I | 10.2               | Timing Classification                            | 492 – 495 |

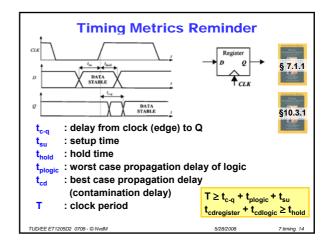

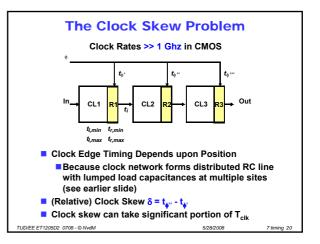

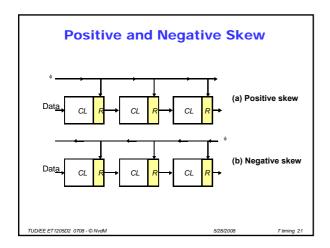

| Р | 10.3.1             | Synchronous Timing Basics                        | 495 – 500 |

| I |                    | Clock Jitter                                     | 500       |

| I |                    | The combined impact of Skew and Jitter           | 501 – 502 |

| I | 10.3.2             | Sources of Skew and Jitter                       |           |

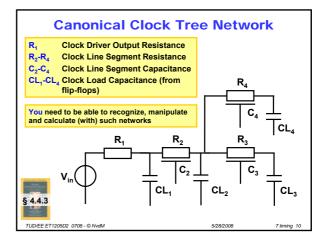

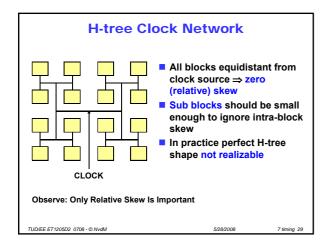

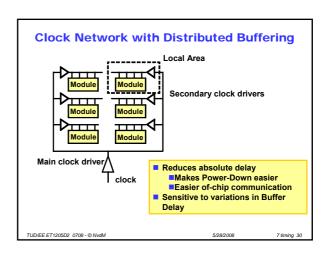

| I | 10.3.3             | Clock Distribution Techniques                    |           |

| 0 | 10.3.4             | Latch-Based Clocking                             | 516 - 518 |

| 0 | 10.4-10.7          | Self-Timed Circuit Design – Future<br>Directions | 519 – 551 |

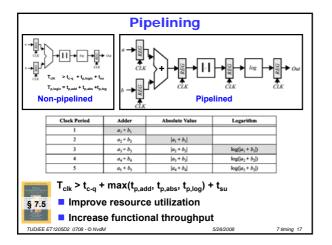

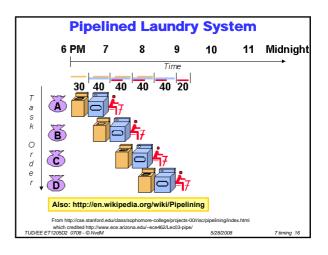

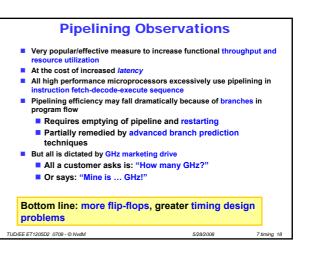

| Р | 7.5 – 7.5.1<br>(!) | Pipelining                                       | 358-361   |

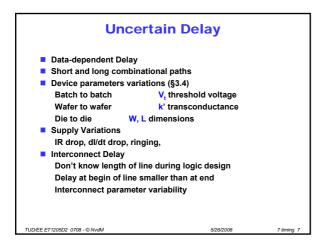

- Delay variations, impact

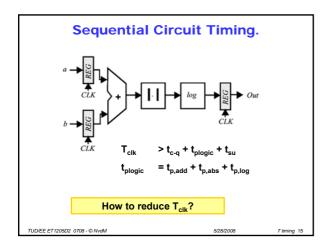

- Sequential circuits, synchronous design

- Pipelining, metrics reminder

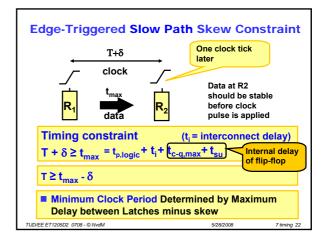

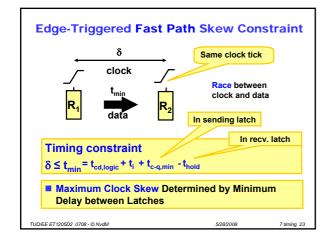

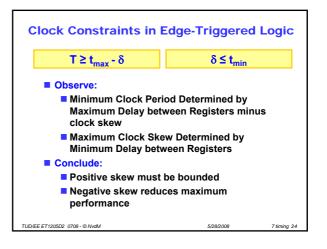

- The Clock Skew Problem

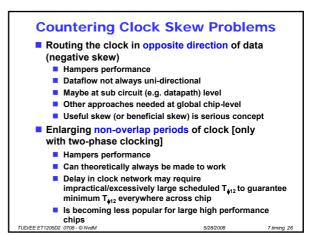

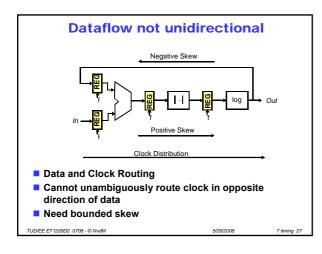

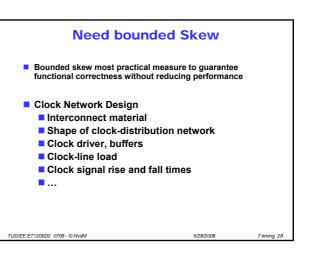

- Controlling Clock Skew

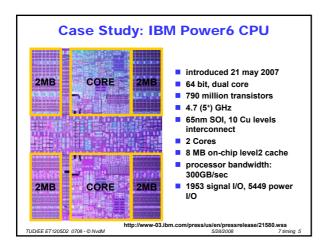

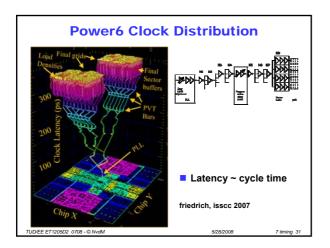

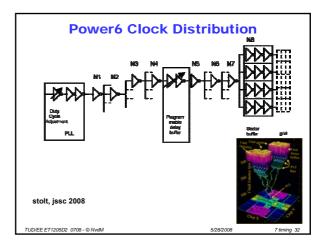

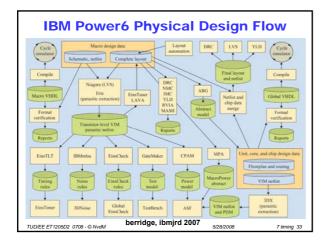

- Case Study

Got basic appreciation of some system level design issues?

TUD/EE ET1205D2 0708 - © NvdN

7 timing 3