| Р | 7.1   | Introduction                                            | 326 – 327 |

|---|-------|---------------------------------------------------------|-----------|

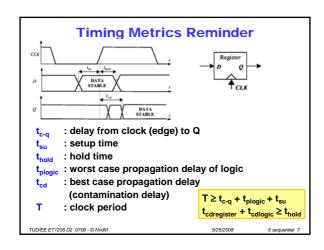

| Р | 7.1.1 | Timing Metrics for Sequential Circuits                  | 327 – 328 |

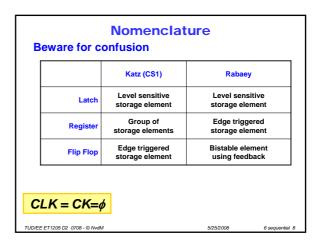

| Р | 7.1.2 | Classification of Memory Elements                       | 328 - 330 |

|   | 7.2   | Static Latches and Registers                            | 330       |

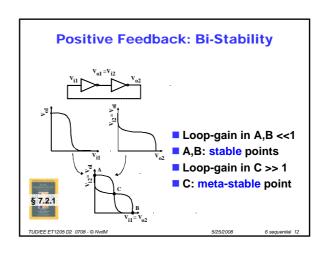

| Р | 7.2.1 | The Bistability Principle                               | 330 - 332 |

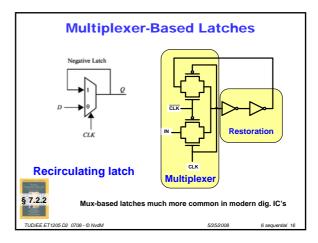

| Р | 7.2.2 | Multiplexer-Based Latches                               | 332 - 333 |

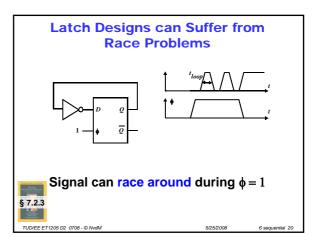

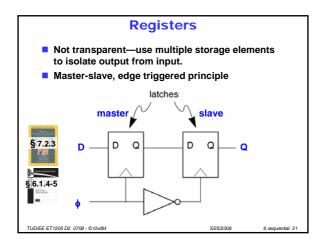

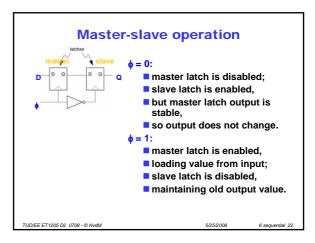

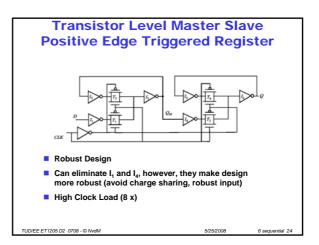

| Р | 7.2.3 | Master-Slave Edge-Triggered Register                    | 333 - 335 |

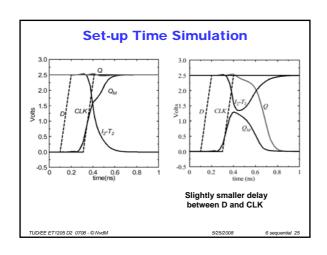

| 1 |       | Timing Properties of Multiplexer-Based Master           | 335 - 339 |

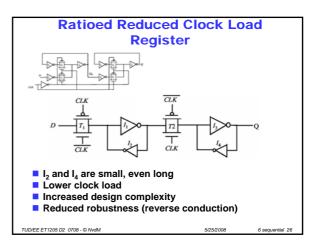

| 0 | 7.2.4 | Low-Voltage Static Latches                              | 339 - 341 |

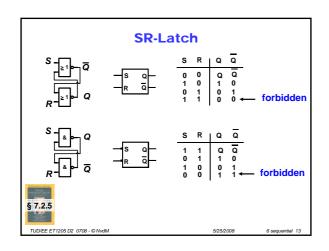

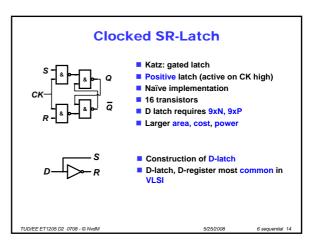

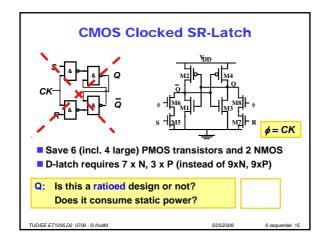

| Р | 7.2.5 | Static SR Flip-Flops — Writing Data by Pure Force       | 341 – 344 |

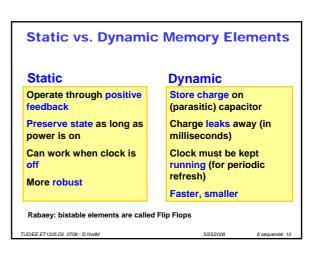

| Т | 7.3   | Dynamic Latches and Registers                           | 344       |

| Т | 7.3.1 | Dynamic Transmission-Gate Edge-Triggered Registers      | 344 - 346 |

| 0 | 7.3.2 | C2MOS — A Clock-Skew Insensitive Approach               | 346 - 350 |

| 0 | 7.3.3 | True Single-Phase Clocked Register (TSPCR)              | 350 - 354 |

| 0 | 7.4   | Alternative Register Styles                             | 354 - 358 |

| Р | 7.5   | Pipelining: An Approach to Optimize Sequential Circuits | 358 - 360 |

| Р | 7.5.1 | Latch versus register based pipelines                   | 360       |

| 0 | 7.5.2 | NORA-CMOS A logic style for pipelined circuits          | 361 - 363 |

|   | 7.6   | Nonbistable Sequential Circuits                         |           |

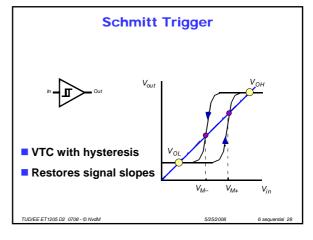

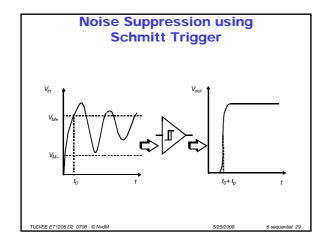

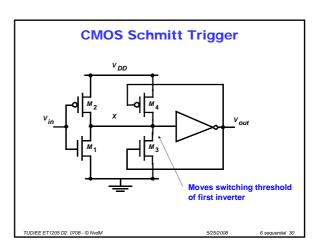

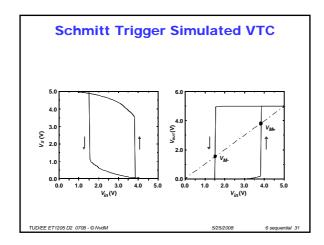

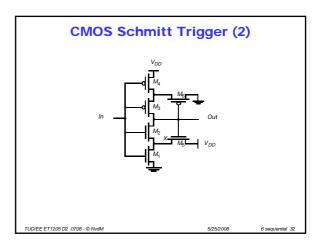

| P | 7.6.1 | The Schmitt Trigger                                     | 364 - 367 |

| 0 | 7.6.2 | Monostable Sequential Circuits                          | 367 - 368 |

| 1 | 7.6.3 | Astable Circuits                                        | 368 - 370 |

| 0 | 7.7   | Perspective: Choosing a Clocking Strategy               | 370 - 371 |

| Р | 7.8   | Summary                                                 | 371 – 372 |

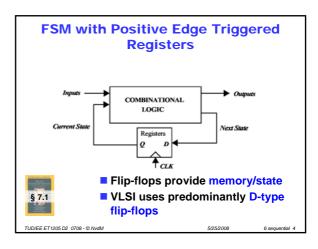

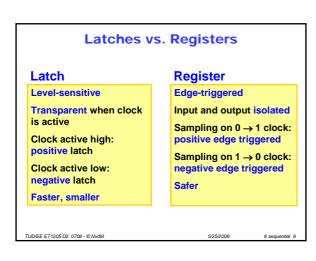

## Memory elements Store a temporary value, remember a state Typically controlled by clock. May have load signal, etc. In CMOS, memory is created by: capacitance (dynamic); feedback (static). Also see http://en.wikipedia.org/wiki/Flip-flop\_(electronics)

## Variations in memory elements Form of required clock signal. How behavior of data input around clock affects the stored value. When the stored value is presented to the output. Whether there is ever a combinational path from input to output.

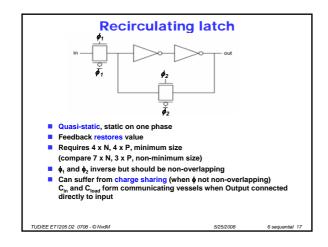

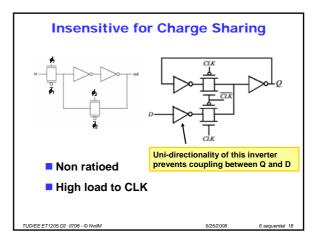

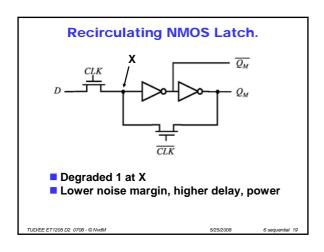

Static Latches and Registers

■ Latches → can be gated or not

■ Registers

TUDEE ET1205 D2 0708 • NiveM 5252008 6 sequential 11

## Summary Background Timing, terminology, classification Static Flipflops Latches Registers Dynamic Flipflops Latches Registers Non-bistable elements Schmitt Trigger