| E |       | des about how to implement a static combinational gate |           |

|---|-------|--------------------------------------------------------|-----------|

| Р | 6.1   | Introduction                                           | 236       |

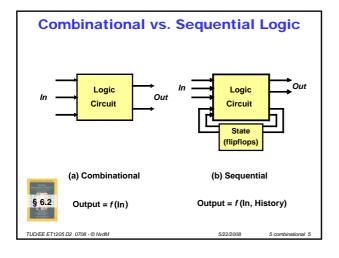

| Р | 6.2   | Static CMOS Design                                     | 236 - 237 |

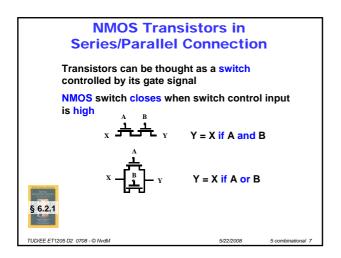

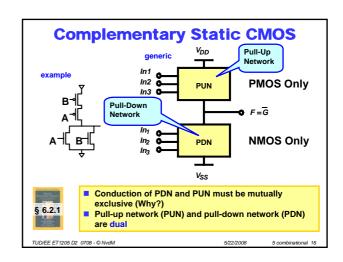

| Р | 6.2.1 | Complementary CMOS                                     | 237 – 242 |

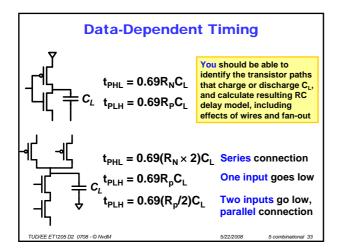

| ı |       | Propagation Delay of Complementary CMOS gates          | 242 - 249 |

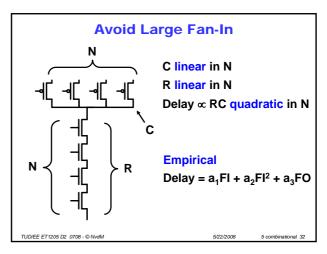

| ı |       | Design Techniques for large fan-in                     | 249 – 251 |

| 0 |       | Optimizing performance in combinational networks       | 251 – 257 |

| 0 |       | Power consumption in CMOS logic gates                  | 257 – 263 |

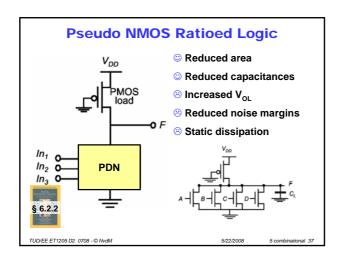

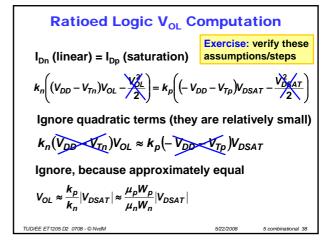

| Р | 6.2.2 | Ratioed Logic                                          | 263 - 267 |

| ı |       | How to build even better loads                         | 267 – 268 |

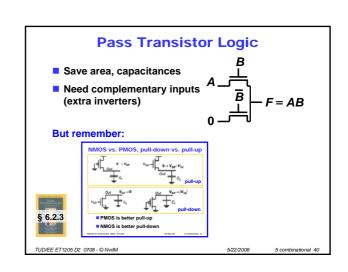

| Р | 6.2.3 | Pass-transistor basics                                 | 269 – 270 |

| ı |       | Example 6.10                                           | 271 – 272 |

| 0 |       | Diversen                                               | 272 – 277 |

| Р |       | Solution 3: Transmission gate logic                    | 277 – 280 |

| ı |       | Rest of § 6.2.3                                        | 280 – 284 |

| ı | 6.3   | Dynamic CMOS Design                                    |           |

| 1 | 6.3.1 | Dynamic Logic: Basic Principles                        | 284 – 286 |

| ı | 6.3.2 | Speed and Power Dissipation of Dynamic Logic           | 287 – 290 |

| ı | 6.3.3 | Signal Integrity Issues in Dynamic Design              | 290 – 295 |

| 0 | 6.3.4 | Cascading Dynamic Gates                                | 295 - 303 |

| 0 | 6.4   | Perspectives                                           | 303 – 306 |

| Р | 6.5   | Summary                                                | 306 - 307 |

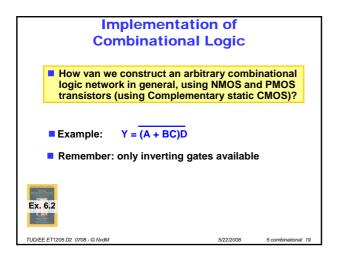

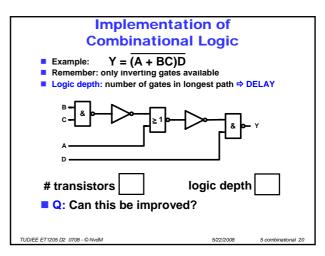

## Combinational Logic - Outline Conventional Static CMOS basic principles Complementary static CMOS Complex Logic Gates VTC, Delay and Sizing Ratioed logic Pass transistor logic Dynamic CMOS gates →only illustration

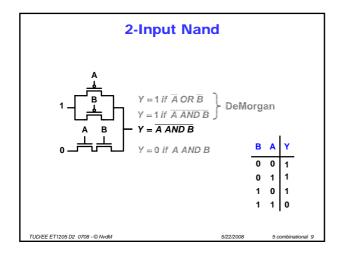

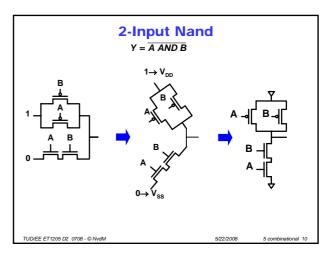

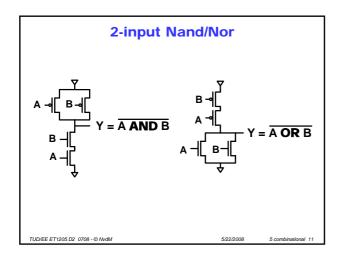

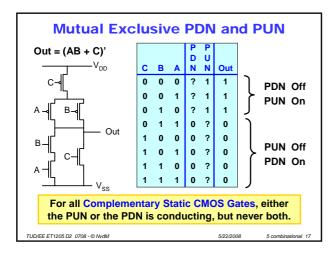

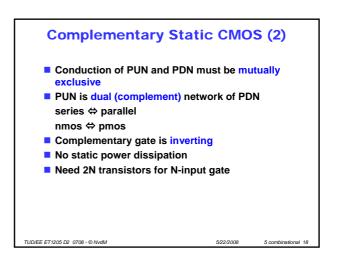

Complementary Static CMOS

Basic Principles

Complementary static CMOS

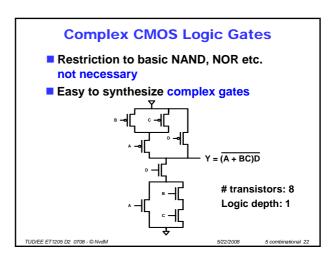

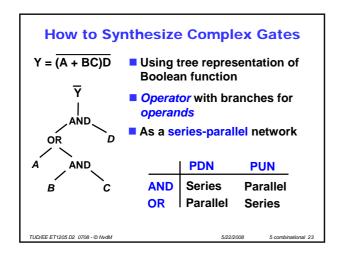

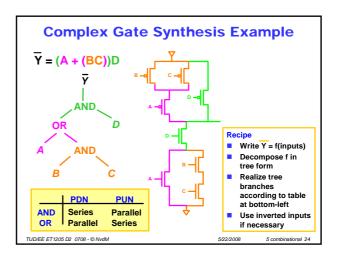

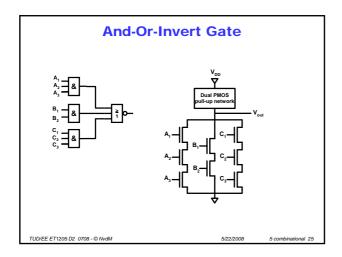

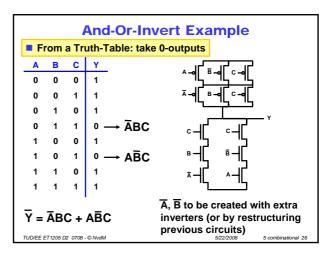

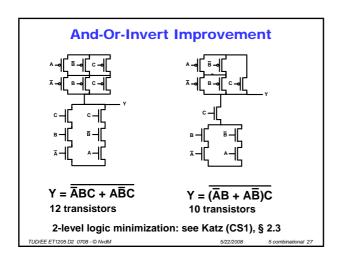

■ Complex Logic Gates

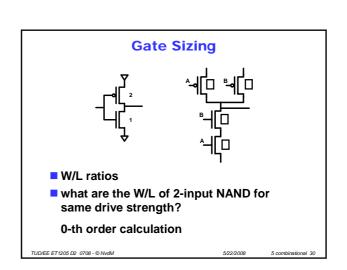

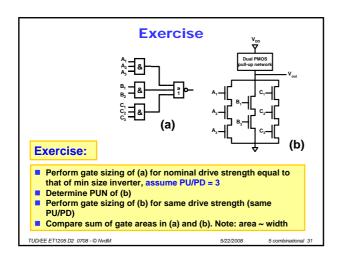

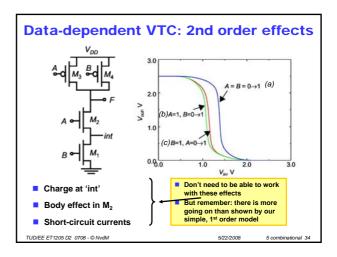

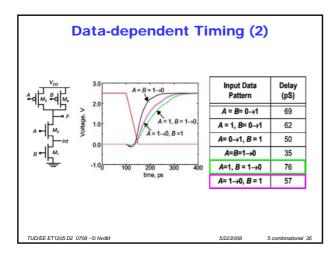

■ VTC, Delay and Sizing

TUD/EE ET1205 D2 0708 - © NvdM 5222008 5 combinational 15

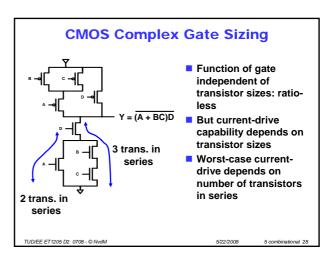

# CMOS Complex Gate Sizing Assume all transistors will have mininum length L Determine W<sub>n</sub> for PDN transistor of inverter that would give the desired 'drive strength' For each transistor in PDN of complex gate do the following: Determine the length I of the longest PDN chain in which it participates Set W = I W<sub>n</sub> Repeat this procedure for PUN, using W<sub>p</sub> for PUN transistor of inverter.

Pass-transistor and Pass-gate circuits

TUDIEE ET1205 D2 0708 -© North

Pass Transistor Logic

Save area, capacitances

Need complementary inputs (might mean extra inverters)

Reduced  $V_{OH}$ , noise margins 0  $V_{OH} = V_{DD} - (V_{Tno} + \gamma((\sqrt{|2\phi_f|} + V_{OH}) - \sqrt{|2\phi_f|}))$ Static dissipation in subsequent static inverter/buffer

Disadvantages (and advantages) may be reduced by complementary pass gates (NMOS + PMOS parallel)

Exercise: Why is there static dissipation in next conventional gate?

### **Exercise**

Discuss what happens when you connect the output of a single pass-transistor (not a pass-gate) to the input of another pass-transistor stage (i.e. the gate of another pass-transistor). Why should you never use such a circuit?

TUD/EE ET1205 D2 0708 - © NvdM 5/22/2008 5 combinational 43

## **Pass Transistor Logic**

- Most typical use: for multiplexing, or path selecting

- Assume in circuit below it is required to either connect A or B to Y, under control by S

- Y = AS + BS' (S' is easier notation for S-bar = S-inverse =  $\overline{S}$ )

- Y = ((AS)' (BS)')' allows realization with 3 NAND-2 and 1 INV:

- Pass gate needs only 6 (or 8) transistors (see also Katz, costion 4.2)

### **Summary**

- Conventional Static CMOS basic principles

- Complementary static CMOS

- Complex Logic Gates

- VTC, Delay and Sizing

- Ratioed logic

- Pass transistor logic

TUD/EE ET1205 D2 0708 - © NvdM

22/2008

8