#### **MODULE 5**

#### **COMBINATIONAL LOGIC**

#### **Course Material for Combinational**

Extra: Slides about how to implement a static combinational gate with NMOS/PMOS transistors, given the Boolean function

| Р | 6.1   | Introduction                                     | 236       |

|---|-------|--------------------------------------------------|-----------|

| Р | 6.2   | Static CMOS Design                               | 236 – 237 |

| Р | 6.2.1 | Complementary CMOS                               | 237 – 242 |

| I |       | Propagation Delay of Complementary CMOS gates    | 242 – 249 |

| I |       | Design Techniques for large fan-in               | 249 – 251 |

| 0 |       | Optimizing performance in combinational networks | 251 – 257 |

| 0 |       | Power consumption in CMOS logic gates            | 257 – 263 |

| Р | 6.2.2 | Ratioed Logic                                    | 263 – 267 |

| I |       | How to build even better loads                   | 267 – 268 |

| Р | 6.2.3 | Pass-transistor basics                           | 269 – 270 |

| I |       | Example 6.10                                     | 271 – 272 |

| 0 |       | Diversen                                         | 272 – 277 |

| Р |       | Solution 3: Transmission gate logic              | 277 – 280 |

| I |       | Rest of § 6.2.3                                  | 280 – 284 |

| I | 6.3   | Dynamic CMOS Design                              |           |

| I | 6.3.1 | Dynamic Logic: Basic Principles                  | 284 – 286 |

| I | 6.3.2 | Speed and Power Dissipation of Dynamic Logic     | 287 – 290 |

| I | 6.3.3 | Signal Integrity Issues in Dynamic Design        | 290 – 295 |

| 0 | 6.3.4 | Cascading Dynamic Gates                          | 295 – 303 |

| 0 | 6.4   | Perspectives                                     | 303 – 306 |

| Р | 6.5   | Summary                                          | 306 – 307 |

|   |       |                                                  |           |

# **Combinational Logic - Outline**

- Conventional Static CMOS basic principles

- Complementary static CMOS

- Complex Logic Gates

- VTC, Delay and Sizing

- Ratioed logic

- Pass transistor logic

- Dynamic CMOS gates ->only illustration

# **Complementary Static CMOS Basic Principles**

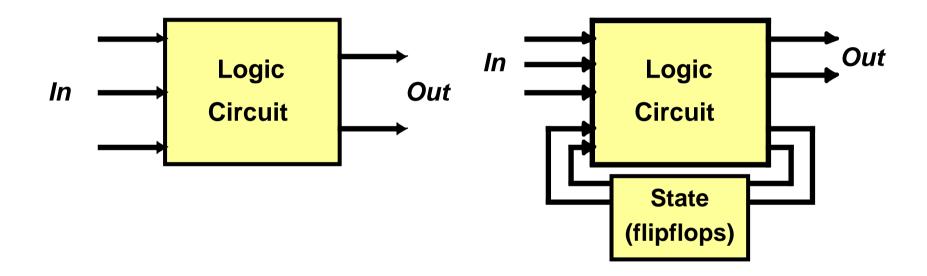

#### Combinational vs. Sequential Logic

(a) Combinational

Output =

$$f(\ln)$$

(b) Sequential

Output =

$$f$$

(In, History)

#### Reminder

#### **DeMorgan Transformations**

$$\overline{A+B}=\overline{A}.\overline{B}$$

$$\overline{A.B} = \overline{A} + \overline{B}$$

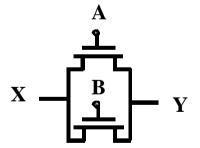

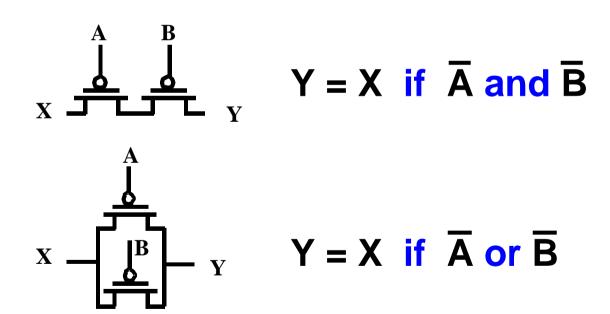

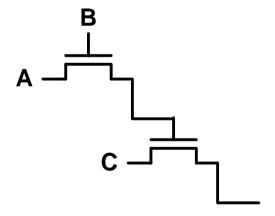

#### NMOS Transistors in Series/Parallel Connection

Transistors can be thought as a switch controlled by its gate signal

NMOS switch closes when switch control input

is high

$$Y = X \text{ if } A \text{ and } B$$

$$Y = X \text{ if } A \text{ or } B$$

## PMOS Transistors in Series/Parallel Connection

**PMOS** switch closes when switch control input is low

$$Y = X$$

if ...

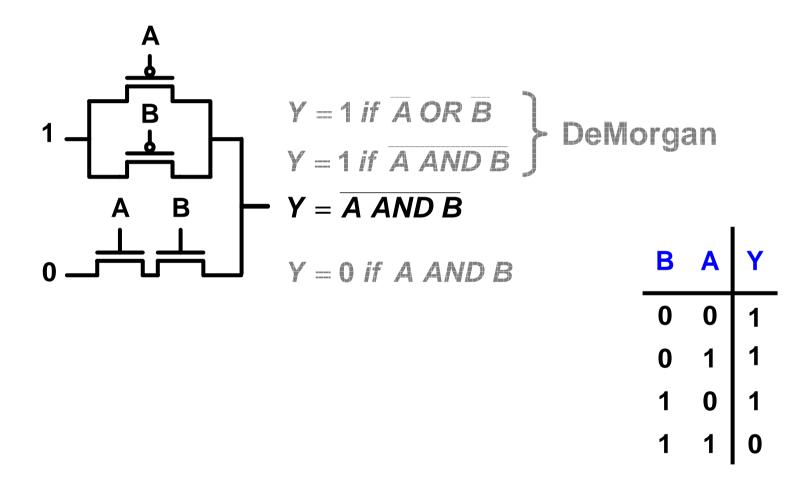

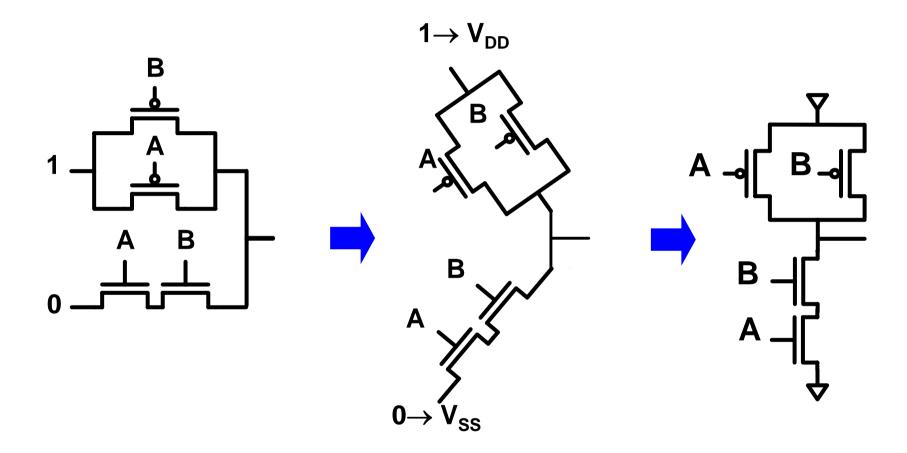

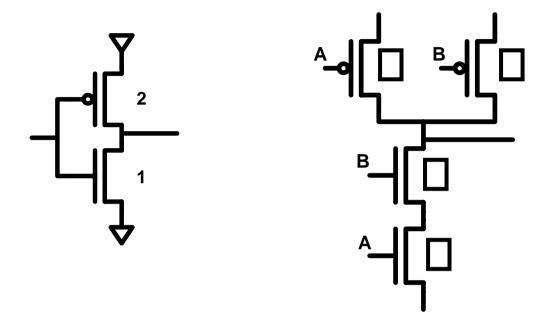

#### 2-Input Nand

# **2-Input Nand**

$$Y = \overline{A \ AND \ B}$$

# 2-input Nand/Nor

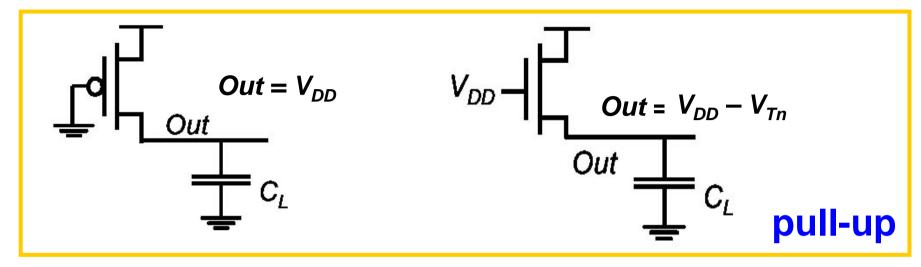

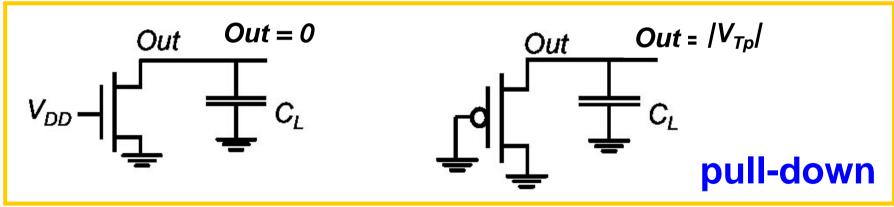

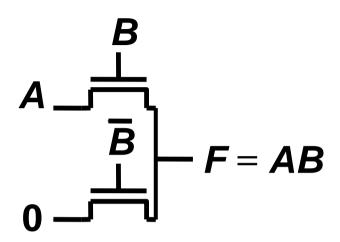

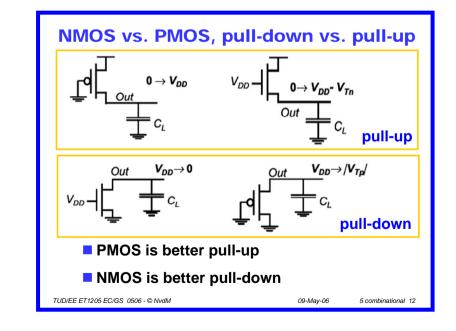

## NMOS vs. PMOS, pull-down vs. pull-up

- PMOS is better pull-up

- NMOS is better pull-down

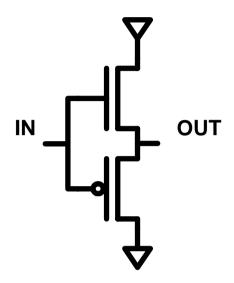

#### **Bad Idea**

**Exercise:** Determine logic function

Determine  $V_{out}$ for  $V_{in} = V_{DD}$  and  $V_{in} = V_{SS}$

Why is this a bad circuit?

## **CMOS Gate is Inverting**

Assume full-swing inputs (high =  $V_{DD}$ , low =  $V_{SS}$ )

Highest output voltage of NMOS is

$$V_{GS} - V_{Tn} = V_{DD} - V_{Tn}$$

- An 1 on NMOS gate can produce a strong 0 at the drain, but not a strong 1

- Lowest output voltage of PMOS is

$$V_{DD} + V_{GS} - V_{Tp} = |V_{Tp}|$$

(with  $V_{GS}$ ,  $V_{Tp} < 0$  for PMOS)

- An 0 on PMOS gate can produce a strong 1 at the drain, but not a strong 0

- Need NMOS for pull-down, PMOS for pull-up

A 1 at input can pull-down, 0 at input can pull-up

A 1 can produce a 0, a 0 can produce a 1

**Inverting behavior**

For a non-inverting Complementary CMOS Gate, you can only use 2 inverting gates

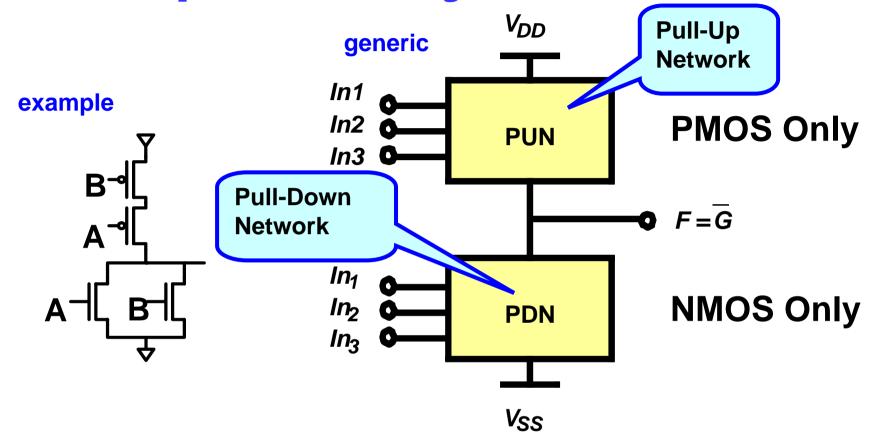

# **Complementary static CMOS**

- **Complex Logic Gates**

- VTC, Delay and Sizing

# **Complementary Static CMOS**

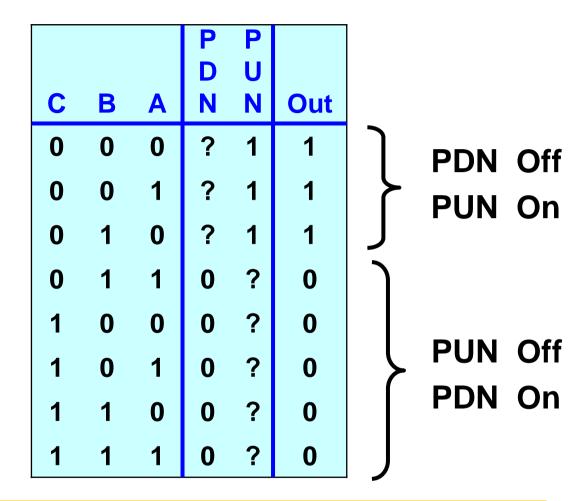

- Conduction of PDN and PUN must be mutually exclusive (Why?)

- Pull-up network (PUN) and pull-down network (PDN) are dual

#### **Mutual Exclusive PDN and PUN**

For all Complementary Static CMOS Gates, either the PUN or the PDN is conducting, but never both.

#### **Complementary Static CMOS (2)**

- Conduction of PUN and PDN must be mutually exclusive

- PUN is dual (complement) network of PDN series ⇔ parallel nmos ⇔ pmos

- Complementary gate is inverting

- No static power dissipation

- Need 2N transistors for N-input gate

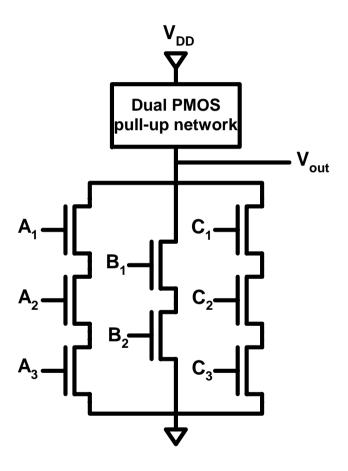

# Implementation of Combinational Logic

How van we construct an arbitrary combinational logic network in general, using NMOS and PMOS transistors (using Complementary static CMOS)?

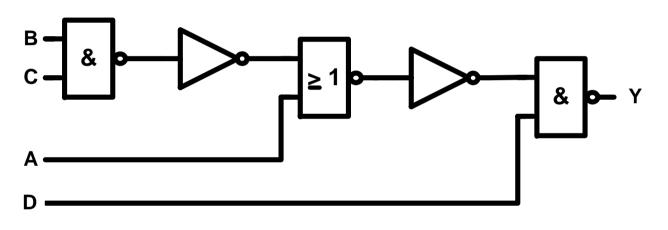

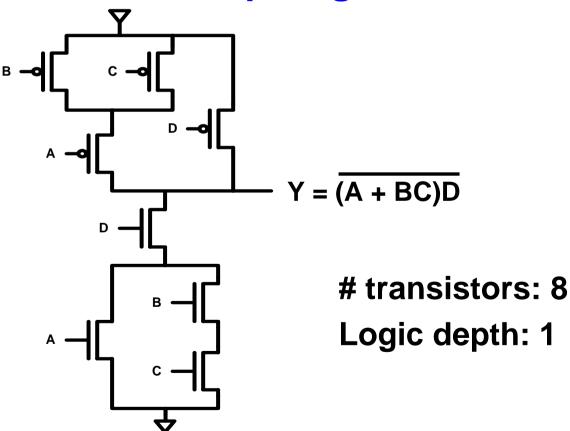

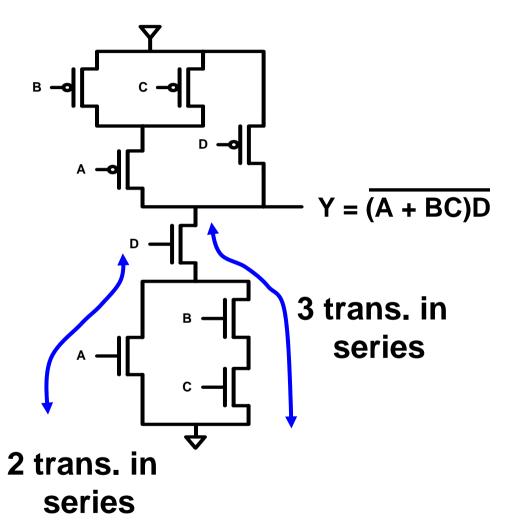

**Example:**

$$Y = (A + BC)D$$

Remember: only inverting gates available

# Implementation of Combinational Logic

- Example: Y = (A + BC)D

- Remember: only inverting gates available

- Logic depth: number of gates in longest path ⇒ DELAY

# transistors logic depth

Q: Can this be improved?

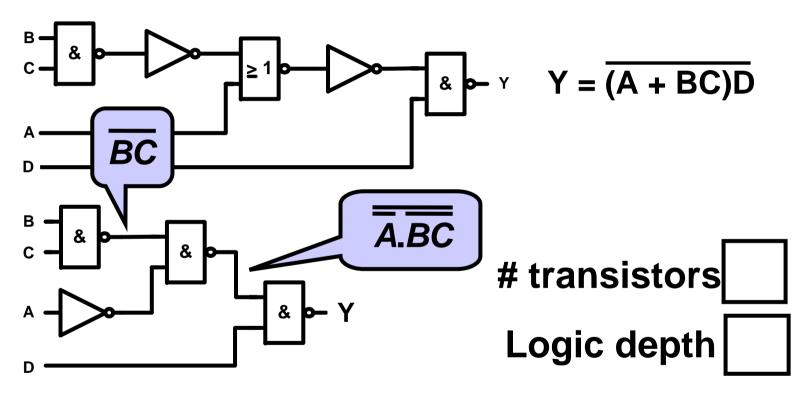

#### **Improved Gate Level Implementation**

Using DeMorgan  $A + BC = \overline{A.BC}$

Q: Can this be further improved?

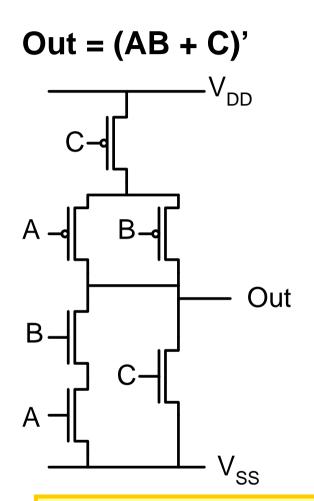

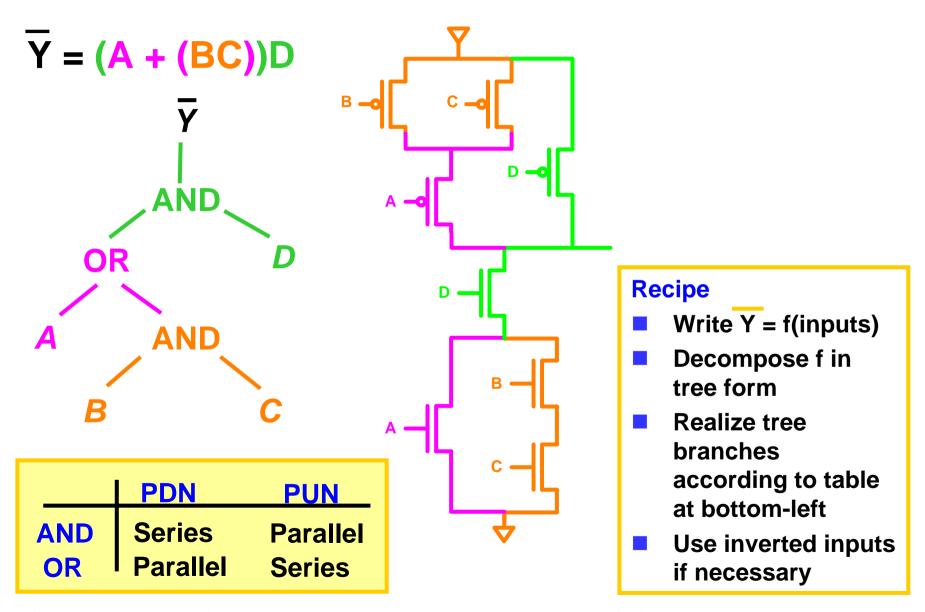

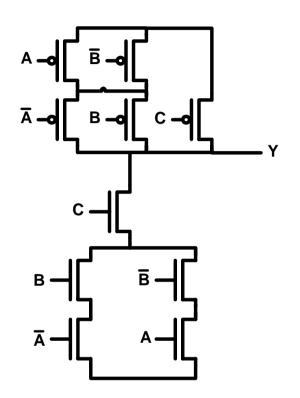

#### **Complex CMOS Logic Gates**

- Restriction to basic NAND, NOR etc. not necessary

- Easy to synthesize complex gates

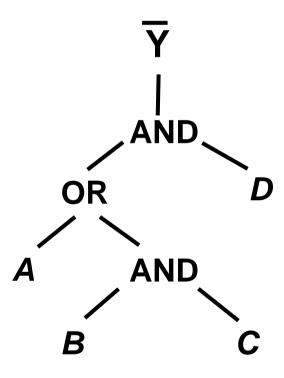

#### **How to Synthesize Complex Gates**

$$Y = \overline{(A + BC)D}$$

- Using tree representation of Boolean function

- Operator with branches for operands

- As a series-parallel network

|     | PDN      | PUN      |

|-----|----------|----------|

| AND | Series   | Parallel |

| OR  | Parallel | Series   |

## **Complex Gate Synthesis Example**

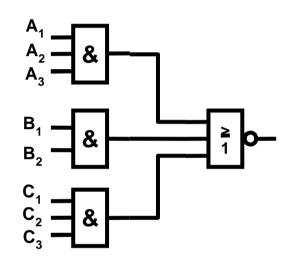

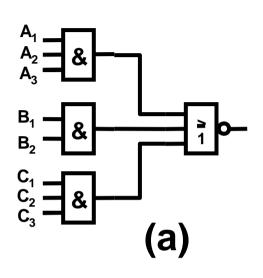

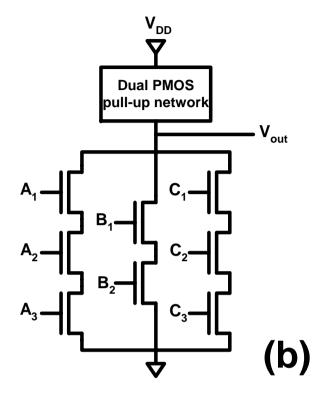

#### **And-Or-Invert Gate**

# **And-Or-Invert Example**

#### From a Truth-Table: take 0-outputs

| Α | В | С | Υ                                  |

|---|---|---|------------------------------------|

| 0 | 0 | 0 | 1                                  |

| 0 | 0 | 1 | 1                                  |

| 0 | 1 | 0 | 1                                  |

| 0 | 1 | 1 | $0 \longrightarrow \overline{A}BC$ |

| 1 | 0 | 0 | 1                                  |

| 1 | 0 | 1 | $0 \longrightarrow A\overline{B}C$ |

| 1 | 1 | 0 | 1                                  |

| 1 | 1 | 1 | 1                                  |

|   |   |   |                                    |

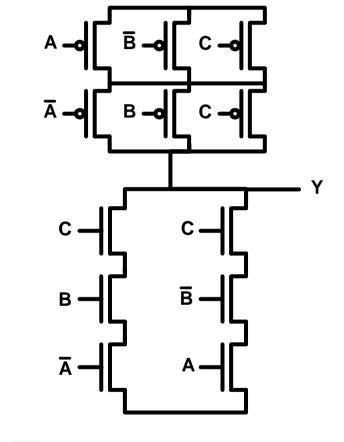

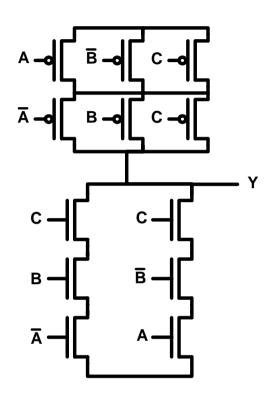

$$\overline{Y} = \overline{A}BC + A\overline{B}C$$

A, B to be created with extra inverters (or by restructuring previous circuits)

#### **And-Or-Invert Improvement**

$$Y = \overline{ABC} + A\overline{BC}$$

12 transistors

$$Y = (\overline{A}B + A\overline{B})C$$

10 transistors

2-level logic minimization: see Katz (CS1), § 2.3

# **CMOS Complex Gate Sizing**

- Function of gate independent of transistor sizes: ratioless

- But current-drive capability depends on transistor sizes

- Worst-case currentdrive depends on number of transistors in series

## **CMOS Complex Gate Sizing**

- $\blacksquare$  Assume all transistors will have mininum length L

- Determine  $W_n$  for PDN transistor of inverter that would give the desired 'drive strength'

- For each transistor in PDN of complex gate do the following:

- Determine the length l of the longest PDN chain in which it participates

- $\blacksquare$  Set  $W = l W_n$

- Repeat this procedure for PUN, using  $W_p$  for PUN transistor of inverter.

#### **Gate Sizing**

- W/L ratios

- what are the W/L of 2-input NAND for same drive strength?

0-th order calculation

#### **Exercise**

#### **Exercise:**

- Perform gate sizing of (a) for nominal drive strength equal to that of min size inverter, assume PU/PD = 3

- Determine PUN of (b)

- Perform gate sizing of (b) for same drive strength (same PU/PD)

- Compare sum of gate areas in (a) and (b). Note: area ~ width

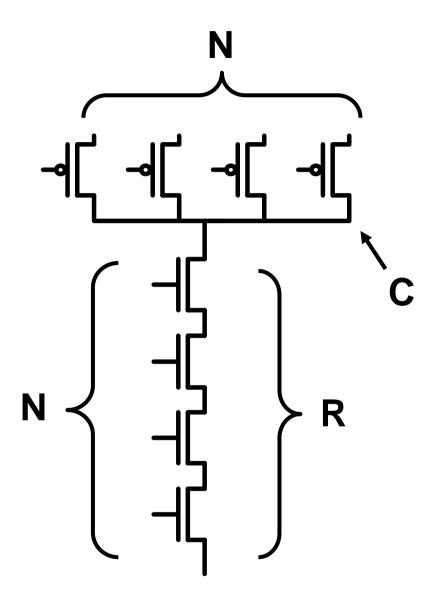

#### **Avoid Large Fan-In**

C linear in N

R linear in N

**Delay** ∞ **RC** quadratic in N

**Empirical**

$Delay = a_1FI + a_2FI^2 + a_3FO$

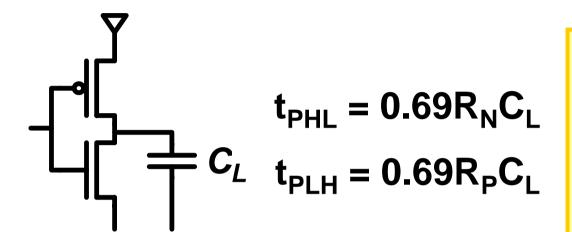

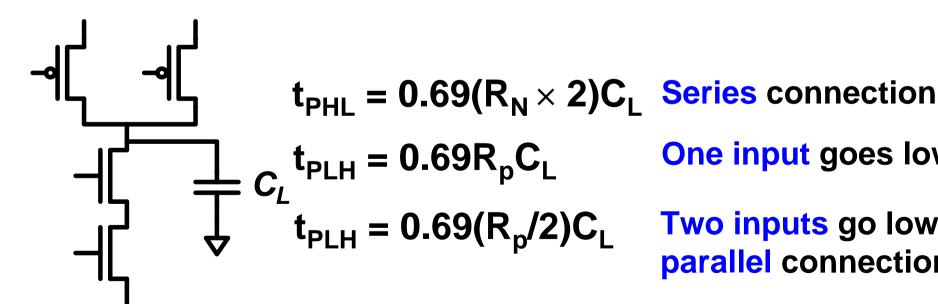

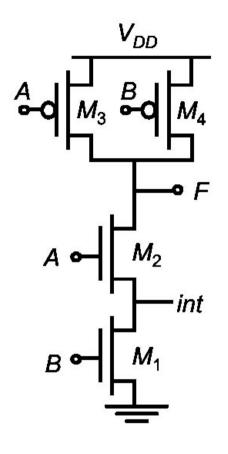

## **Data-Dependent Timing**

You should be able to identify the transistor paths that charge or discharge C<sub>1</sub>, and calculate resulting RC delay model, including effects of wires and fan-out

One input goes low

Two inputs go low, parallel connection

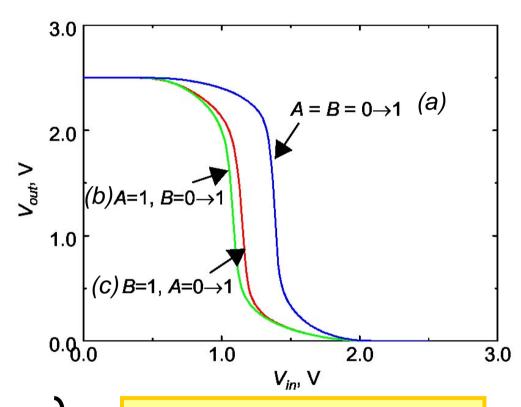

#### Data-dependent VTC: 2nd order effects

- Charge at 'int'

- Body effect in M<sub>2</sub>

- Short-circuit currents

# **Data-dependent Timing (2)**

| Input Data<br>Pattern        | Delay<br>(pS) |

|------------------------------|---------------|

| A = B= 0→1                   | 69            |

| A = 1, B= 0→1                | 62            |

| A= 0→1, B = 1                | 50            |

| <i>A=B</i> =1→0              | 35            |

| <i>A</i> =1, <i>B</i> = 1→0  | 76            |

| <i>A</i> = 1→0, <i>B</i> = 1 | 57            |

# Ratioed logic Pass transistor logic

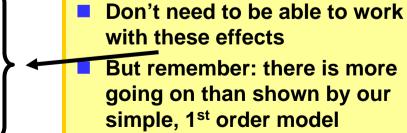

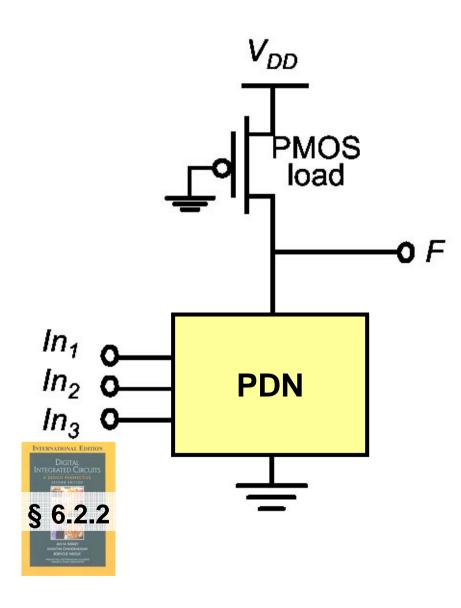

#### **Pseudo NMOS Ratioed Logic**

- © Reduced area

- **©** Reduced capacitances

- ⊗ Increased V<sub>oL</sub>

- **®** Reduced noise margins

- **Static dissipation**

# Ratioed Logic Vol Computation

$I_{Dn}$  (linear) =  $I_{Dp}$  (saturation) assumptions/steps

**Exercise:** verify these assumptions/steps

$$k_n \left( (V_{DD} - V_{Tn}) V_{OL} - \frac{V_{OL}^2}{2} \right) = k_p \left( (-V_{DD} - V_{Tp}) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right)$$

Ignore quadratic terms (they are relatively small)

$$k_n(V_{DD} V_{Tn})V_{OL} \approx k_p(-V_{DD} V_{Tp})V_{DSAT}$$

Ignore, because approximately equal

$$V_{OL} \approx \frac{k_p}{k_n} |V_{DSAT}| \approx \frac{\mu_p W_p}{\mu_n W_n} |V_{DSAT}|$$

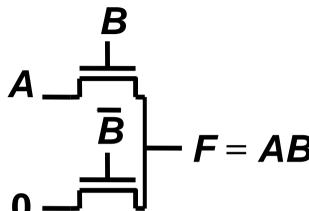

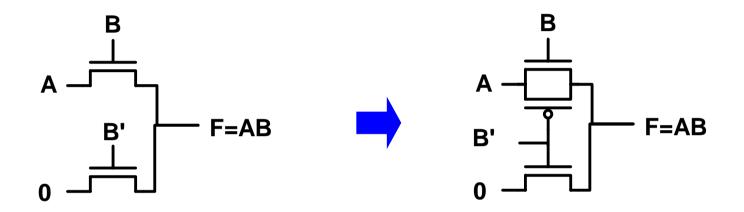

# Pass-transistor and Pass-gate circuits

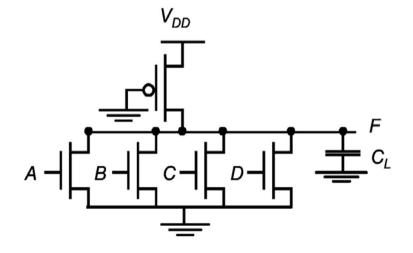

#### **Pass Transistor Logic**

- Save area, capacitances

- Need complementary inputs (extra inverters)

#### **But remember:**

## **Pass Transistor Logic**

- Save area, capacitances

- Need complementary inputs (might mean extra inverters)

- Reduced V<sub>OH</sub>, noise margins 0

- $V_{OH} = V_{DD} \left(V_{Tno} + \gamma \left( \left( \sqrt{|2\phi_f| + V_{OH}} \right) \sqrt{|2\phi_f|} \right) \right)$

- Static dissipation in subsequent static inverter/buffer

- Disadvantages (and advantages) may be reduced by complementary pass gates (NMOS + PMOS parallel)

**Exercise:** Why is there static dissipation in

next conventional gate?

#### **Pass Gates**

Remedy: use an N-MOS and a P-MOS in parallel

- Pass gates eliminate some of the disadvantages of simple pass-transistors

- But also some of the advantages

- Design remains a trade-off!

Pass-gate a.k.a. Transmission-gate

#### **Exercise**

Discuss what happens when you connect the output of a single pass-transistor (not a pass-gate) to the input of another pass-transistor stage (i.e. the gate of another pass-transistor). Why should you never use such a circuit?

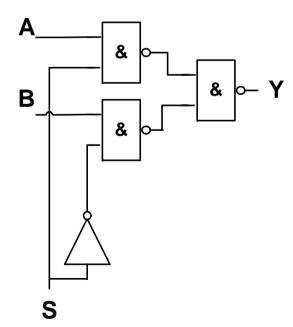

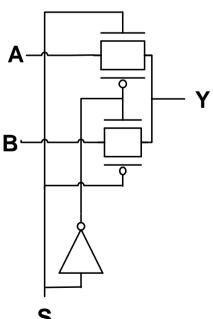

#### **Pass Transistor Logic**

- Most typical use: for multiplexing, or path selecting

- Assume in circuit below it is required to either connect A or B to Y, under control by S

- Y = AS + BS' (S' is easier notation for S-bar = S-inverse =  $\overline{S}$ )

- Y = ((AS)' (BS)')' allows realization with 3 NAND-2 and 1 INV: 14 transistors

- Pass gate needs only 6 (or 8) transistors (see also Katz, section 4.2)

#### **Summary**

- Conventional Static CMOS basic principles

- Complementary static CMOS

- Complex Logic Gates

- VTC, Delay and Sizing

- Ratioed logic

- Pass transistor logic