##

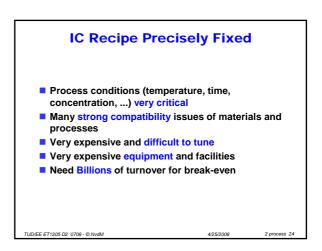

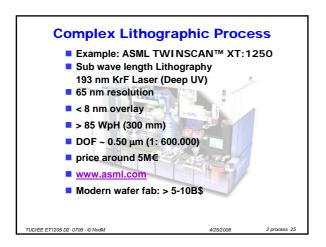

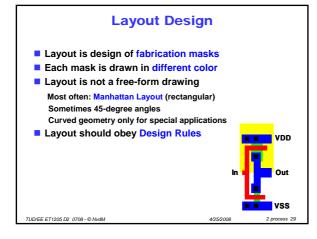

## Design Rules The fabrication process will suffer from tolerances Chip features will have a practical minimum size to allow them to be fabricated reliably enough (with high enough yield) This is captured into a set of precise Design Rules Modern processes have terribly complex set of design rules as a compromise between flexibility and manufacturability We will ignore this subject But you will have to understand it during OP next year.

## **Summary**

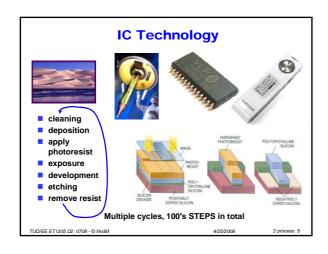

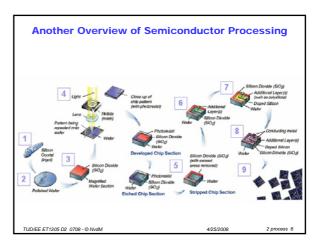

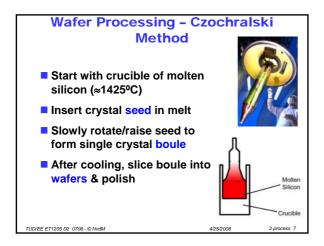

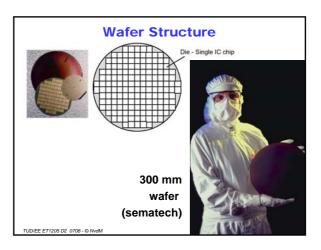

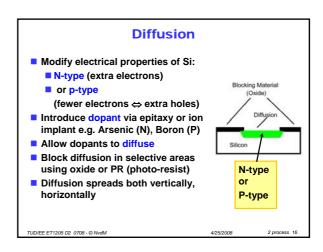

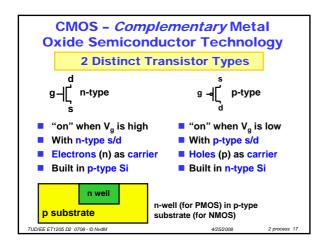

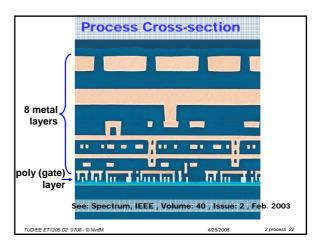

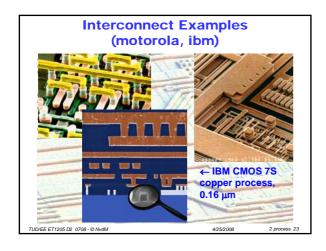

- CMOS Processing

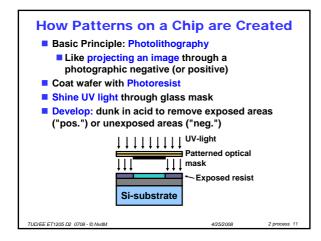

Photolithography

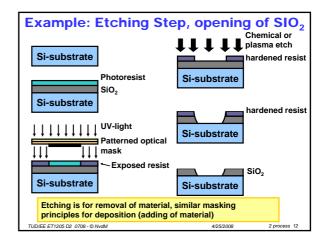

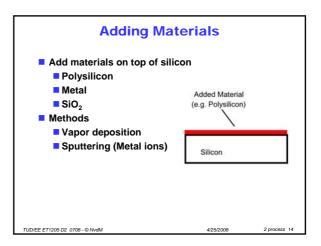

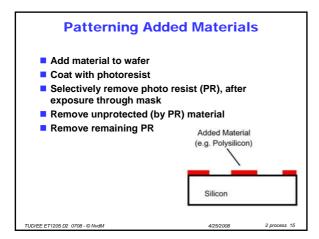

Material Deposition & Removal

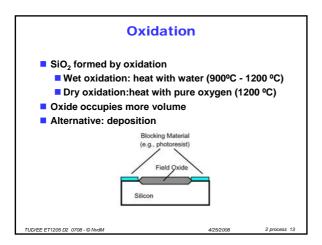

Oxide Growth & Removal

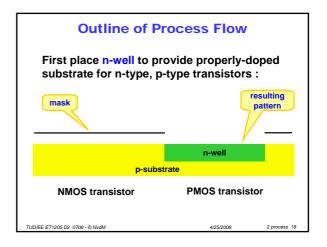

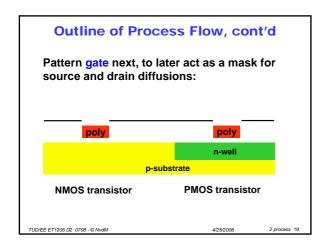

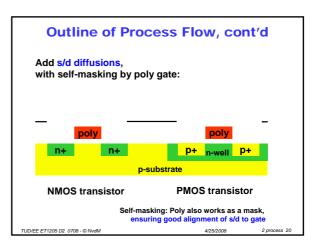

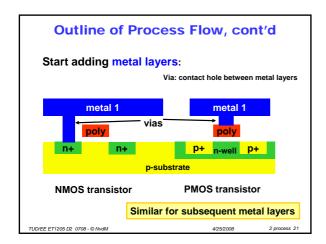

CMOS Process Outline

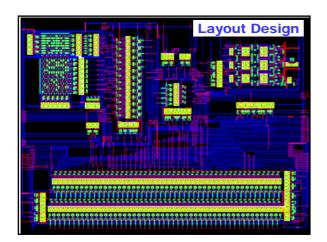

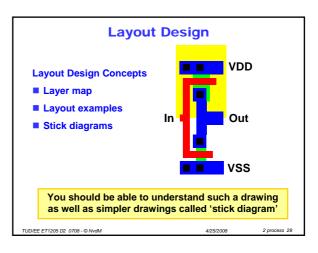

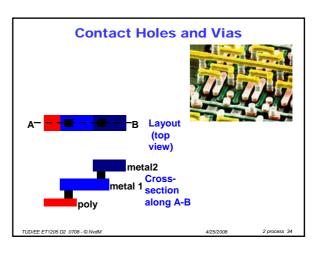

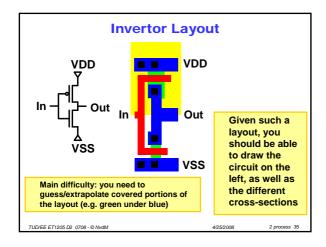

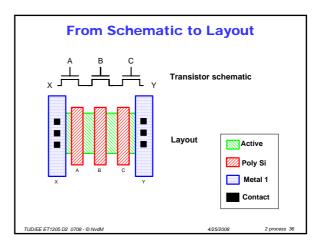

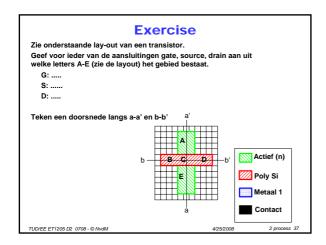

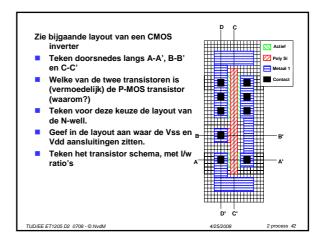

Layout Design

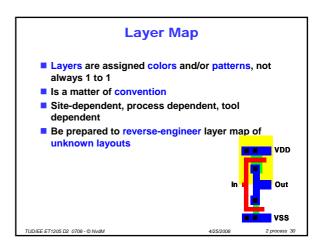

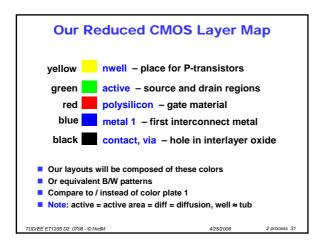

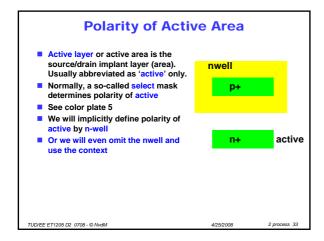

Layer map

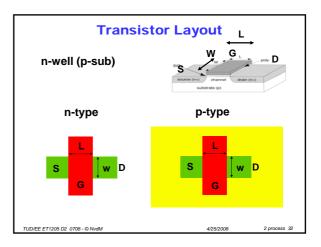

- - Layout examples

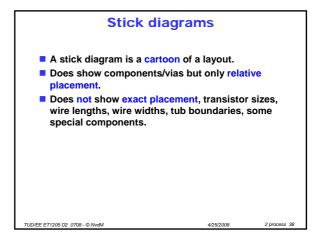

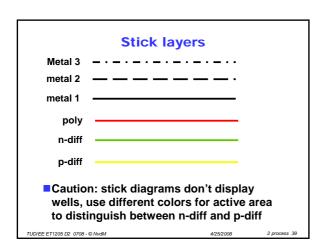

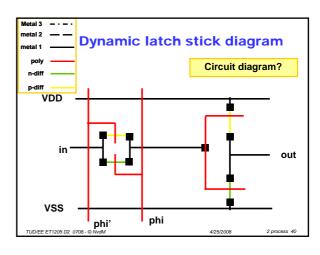

- Stick diagramsDesign RulesWhy we need design rules

TUD/EE ET1205 D2 0708 - © NvdM