# Goal of this chapter

- Present intuitive understanding of device operation

- Introduction of basic device equations

- Introduction of models for manual analysis

- Introduction of models for SPICE simulation

- Analysis of secondary and deep-sub-micron effects

- Future trends

## **Outline**

- Semiconductor Physics

- The diode

- Depletion, I-V relations, capacitance,

- The MOS transistor

- First glance, threshold, I-V relations, models

- Dynamic behavior (capacitances), resistances,

- Process variations

## **Course Material for Devices**

## **Chapter 3**

## P = primair, I = Illustratie, O = overslaan

| С | 3.1         | Introduction                       | 74            |

|---|-------------|------------------------------------|---------------|

| Р | 3.2-3.2.1   | A first glance at the diode        | 74 – 77       |

| Р | 3.2.2       | Static Behavior                    | 77 – 80       |

| 0 | 3.2.3       | Dynamic, or Transient, Behavior    | 80 – 83 (1)   |

| 0 | 3.2.4       | Secondary Effects                  | 84 – 85       |

| 0 | 3.2.5       | Spice Diode Model                  | 85 – 87       |

| P | 3.3 – 3.3.2 | The MOS(FET) Transistor            | 87 – 99       |

| 0 |             | Subthreshold Conduction            | 99 – 101      |

| P |             | Models for Manual Analysis         | 101 – 106     |

| 0 | 3.3.2       | Dynamic Behavior, etc.             | 106 – 113 (1) |

| P |             | Junction Capacitances              | 110 – 111     |

| 0 | 3.3.3       | Some Secondary Effects             | 114 – 117     |

| 0 | 3.3.4       | Spice Model for the MOS Transistor | 117 – 120     |

| 0 | 3.4         | A word on process variations       | 120 – 122     |

|   | 3.5         | Perspective: Technology Scaling    | 122 – 128     |

| Р | 3.6         | Summary                            | 128 – 129     |

#### (1) Vervangend studiemateriaal voor dynamisch gedrag in syllabus

# Modeling

- An abstraction of (the properties) of something to help understanding and predicting its behavior

- **Domain Specific:** weather, climate, economy, stock market, ...

- Different models for something to answer different questions

- Black-Box modeling vs. Physically Based

After Einstein: a model should be as simple as possible, but not simpler

- All electrical behavior is determined by underlying physics

- This course is not about the physics

- But some small amount of background information helps built intuition

- Intuition is what an engineer/designer needs most

- Also see S&G Chapter 2.

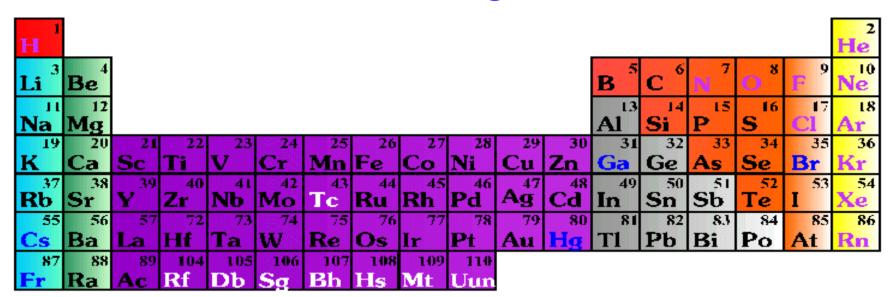

# **Periodic System**

| 58 | 59 | 60 | 61 | 62 | 63 | 64 | 65                     | 66 | 67 | 68            | 69  | 70  | 71  |

|----|----|----|----|----|----|----|------------------------|----|----|---------------|-----|-----|-----|

| Ce | Pr | Nd | Pm | Sm | Eu | Gd | Tb                     | Dy | Ho | Er            | Tm  | Yb  | Lu  |

| 90 | 91 | 92 | 93 | 94 | 95 | 96 | 97                     | 98 | 99 | 100           | 101 | 102 | 103 |

| Th | Pa | U  | Np | Pu | Am | Cm | $\mathbf{B}\mathbf{k}$ | Cf | Es | $\mathbf{Fm}$ | Md  | No  | Lr  |

#### Legend

http://www.chemicool.com/

# **Periodic System**

|    | B 5   | C 6 | N 7  | 0 |

|----|-------|-----|------|---|

|    | Al 13 | Si  | P 15 | S |

| 30 | 31    | 32  | 33   |   |

| n  | Ga    | Ge  | As   | S |

| 48 | 49    | 50  | 51   |   |

| d  | In    | Sn  | Sb   | Ť |

| 80 | 81    | 82  | 83   |   |

| g  | TI    | Pb  | Bi   | P |

| Name      | <b>Symbol</b> | #         | Valence |

|-----------|---------------|-----------|---------|

| Silicon   | Si            | 14        | 4       |

| Boron     | В             | 5         | 3       |

| Phosphor  | Р             | 15        | 5       |

| Arsenic   | As            | 33        | 5       |

| Germanium | Ge            | <b>32</b> | 4       |

See also Tipler (BKV) 38.5

- Intrinsic Si

- Ideal crystal structure

- Valence 4

- almost no free carriers

- almost no conduction

$$[n] = [p] = n_i = 1.5.10^{10}/cm^3$$

at 300 K for silicon

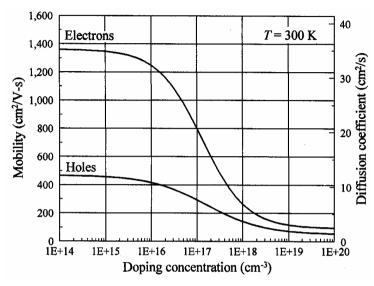

- doping with valence 5 atoms (Phosphor, Arsenic) introduces "loose electrons"

- electron donor

- conductivity depends on doping level

$$n.p = n_i^2$$

(in equilibrium)

- doping with valence 5 atoms (Phosphor, Arsenic) introduces "loose electrons"

- electron donor

- conductivity depends on doping level

- doping with valence 3 atoms (Boron) introduces "loose holes"

- electron acceptors

- hole conductivity lower than electron conductivity

Si in equilibrium :  $n.p = n_i^2 = 2.25 \times 10^{20}$  at 300K Intrinsic Si :  $n = p = n_i$

$$N_D >> N_A$$

Electron donors: As, P n-type Si

$$n \approx N_D, p = n_i^2/n$$

**Electrons: majority carriers**

**Holes: minority carriers**

Resistive material Conductivity depends on  $N_D$

$$N_A >> N_D$$

Electron acceptors: B p-type Si

$$p \approx N_A$$

,  $n = n_i^2/p$

**Holes: majority carriers**

**Electrons: minority carriers**

Hole conductivity lower

than electron conductivity

### The diode

**■** Depletion, I-V relations, capacitance,

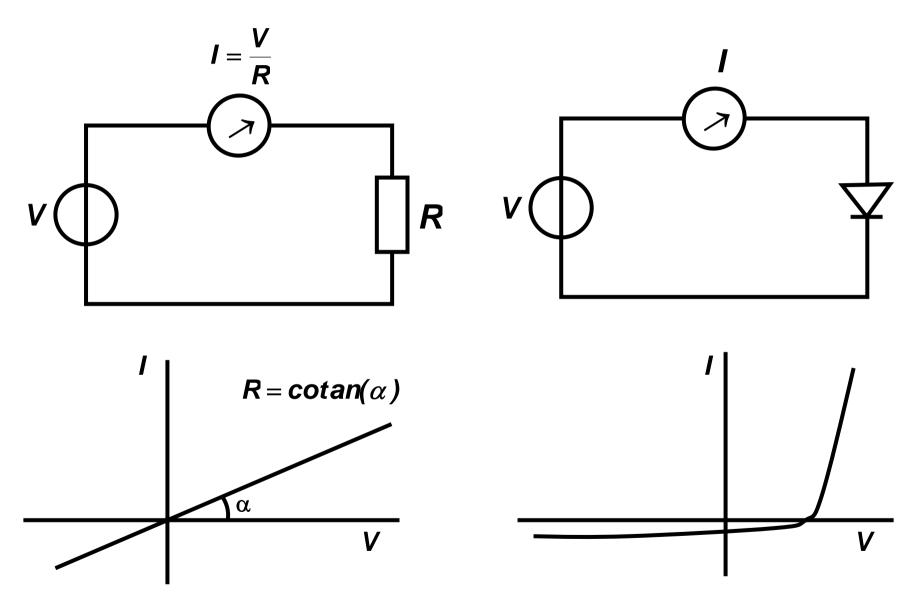

## The diode: non-linear resistance

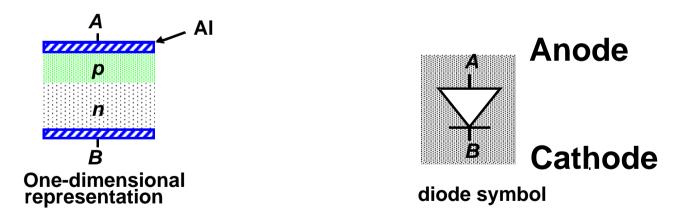

## The Diode

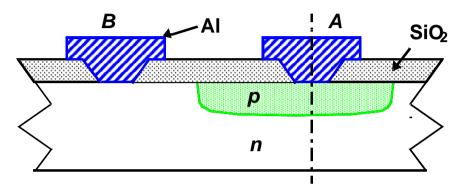

See also Tipler (BKV) 38.6

Cross-section of *pn*-junction in an IC process

Diode is abundant as MOS source/drain

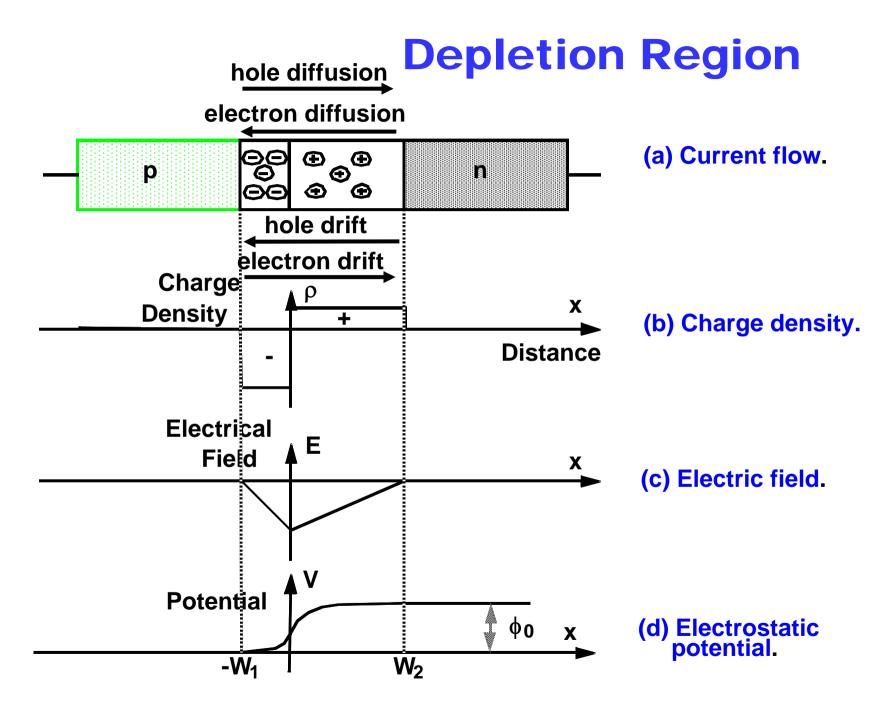

# Ideal Diode, Abrupt pn junction Intuitive Description

p-Si n-Si

Electron diffusion

p - + n

Hole drift

Electron drift

Join n-Si with p-Si **Concentration gradient of** free carriers **Diffusion current** Space charge (depletion) region **Electric field Drift current opposite to** diffusion equilibrium

## Conduction

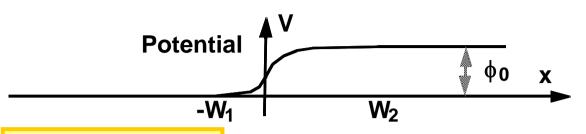

Typical  $N_A$ ,  $N_D$ :  $10^{15} \dots 10^{17}/\text{cm}^3$ ,  $\phi_{\theta}$  around 0.6 V

**Built-in Potential**

$$\phi_0 = \phi_T \ln \left[ \frac{N_A N_D}{n_i^2} \right]$$

Thermal voltage

$$\phi_T = \frac{kT}{q} = 26mV$$

at  $300K$

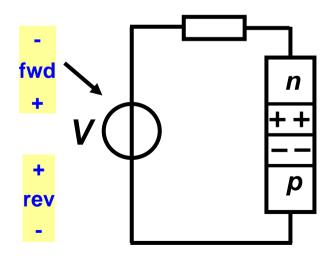

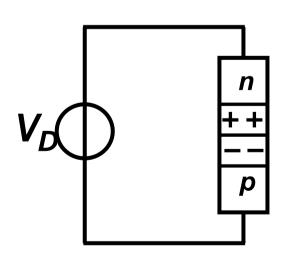

- By applying an external voltage, width of depletion region can be changed

- Forward: becomes smaller and smaller, finally conduction

- Reverse: becomes wider and widerno conduction

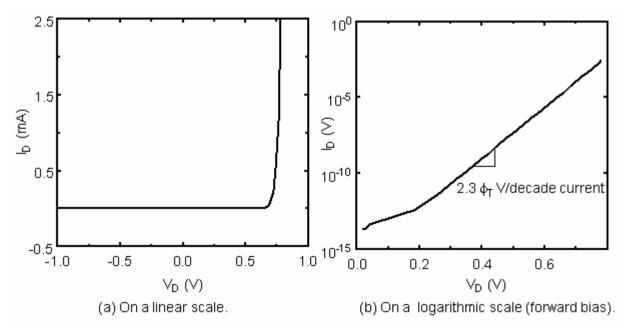

## **Diode Current**

$$I_D = I_S \Big( \mathbf{e}^{V_D/\phi_T} - \mathbf{1} \Big)$$

- $\blacksquare$   $I_S$ : Saturation current

- Proportional to diode area

- Depends on doping levels, and widths of neutral regions

- Usually determined empirically

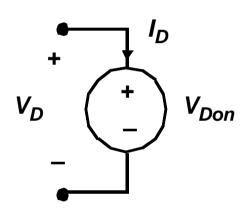

# **Models for Manual Analysis**

$$I_D = I_S \left( e^{V_D/\phi_T} - 1 \right)$$

$$V_D = V_S \left( e^{V_D/\phi_T} - 1 \right)$$

(a) Ideal diode model

(b) First-order diode model

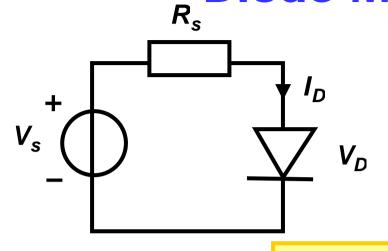

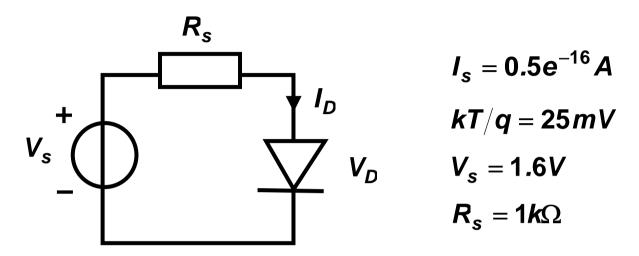

# **Diode Model Example**

#### Determine $I_D$

$$I_D = I_s(e^{V_D/\phi_T} - 1)$$

(diode model)

$$V_s - R_s I_D = V_D$$

(Kirchof)

$$V_S - R_S I_S (e^{V_D I \phi_T} - 1) = V_D$$

#### **Picard Iteration**

$$I_s = 0.5e^{-16}A$$

$kT/q = 25mV$

$V_s = 1.6V$

$R_s = 1k\Omega$

Start:

$$V_D = 1.0 V$$

$\Rightarrow I_D = (V_S - V_D)/R_S = 0.600 \text{ mA}$

$\Rightarrow V_D = \phi_T (1 + In(I_D/I_S)) = 0.663 V$

$\Rightarrow I_D = = 0.937 \text{ mA}$

$\Rightarrow V_D = = 0.674 V$

$\Rightarrow I_D = = 0.926 \text{ mA}$

$\Rightarrow V_D = = 0.674 V$

# **Diode Model Example**

#### First order solution

$$V_D = 0.6V \Rightarrow I_D = 1 \, mA \quad \text{error} = 8 \%$$

Now, take  $V_s = 10.6V$   $R_s = 10K\Omega$

The error will be

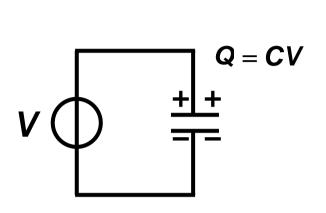

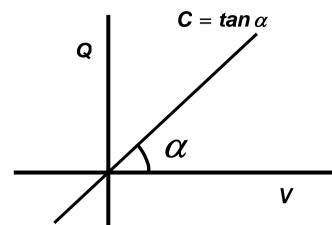

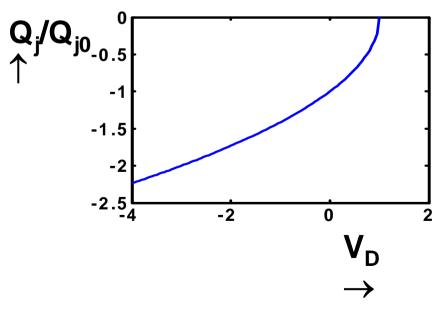

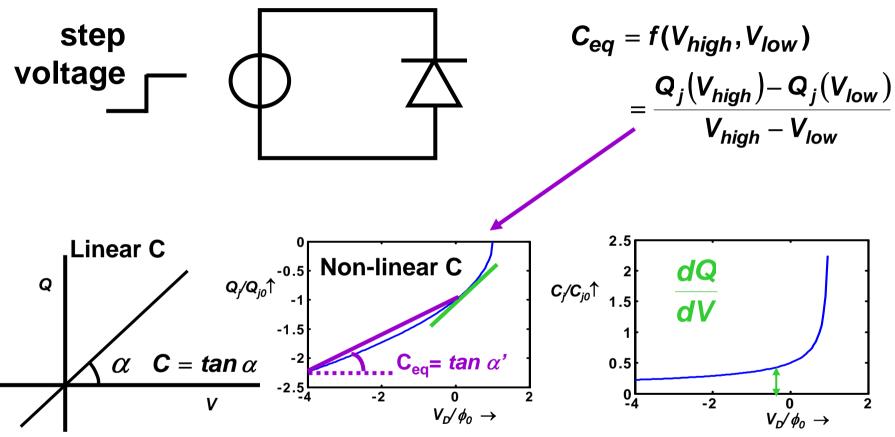

# **Capacitance**

# Linearized Large-Signal Diode Capacitances

### **Summary:**

- Diode capacitances highly nec

- Difficult with manual calculation

- We are ultimately interested in amount of ge being stored on (or removed from) capacitor

- Since it takes time for this to happen, this determines the final switching speed of the circuit: more charge means more time!

- Linear capacitance:  $\triangle Q = C \triangle V$ : easy to work with

- Small-signal capacitance: dQ = CdV: for analog appl.

- Non-linear capacitance:  $\Delta Q = f(V_{low}, V_{high})$

Work with C<sub>eq</sub> for standardized voltage swings

See the

syllabus!

# Large Signal Equivalent Diode Capacitance

Linearized, large signal, depends on swing

Linearized, small signal, depends on bias

For analog applications

#### The MOS Transistor

- First glance, threshold, I-V relations, models

- Dynamic behavior (capacitances), resistances, more Second-Order effects, models

#### The MOS Transistor – compared to Storey

- no J-Fet

- Also other operating regions compared to saturation region (linear, velocity saturation)

- Include more effects (channel length modulation)

- Short-channel devices (bad for some analog circuits, good for (most) digital circuits)

- We will develop understanding of basic device equations

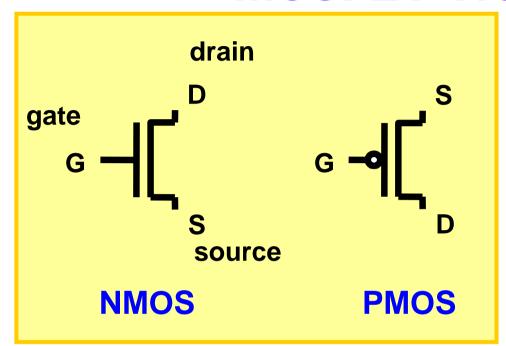

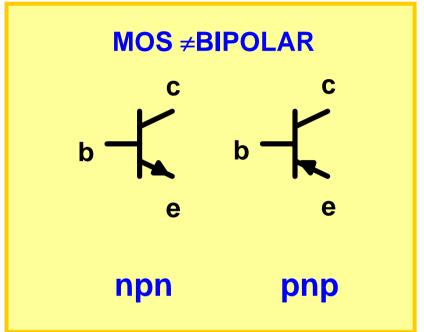

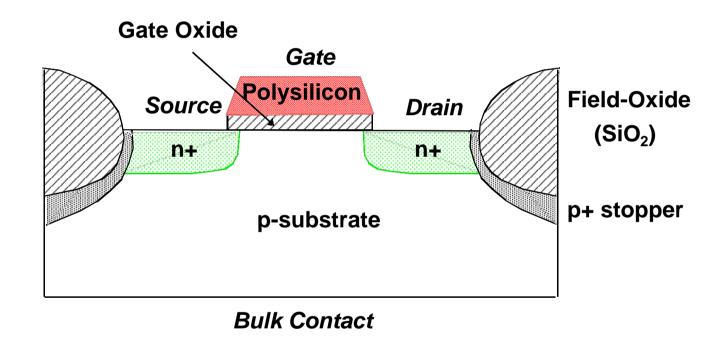

## **MOSFET Transistors**

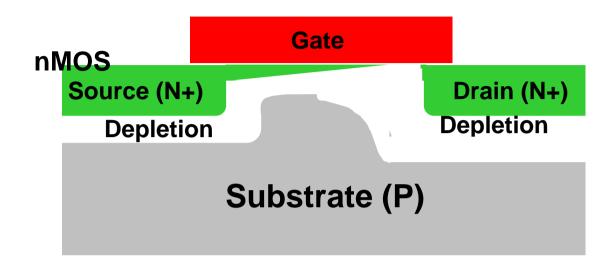

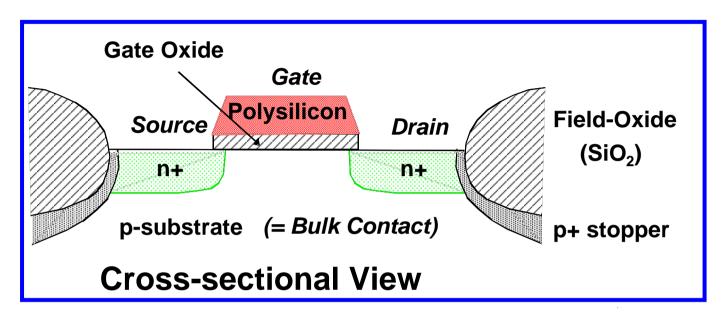

**MOSFET = "Metal"-Oxide-Semiconductor Field-Effect Transistor**

**Cross-sectional view of MOSFET**

Gate (terminal of MOSFET)

≠

Logic gate

## **The MOS Transistor**

**CROSS-SECTION of NMOS Transistor**

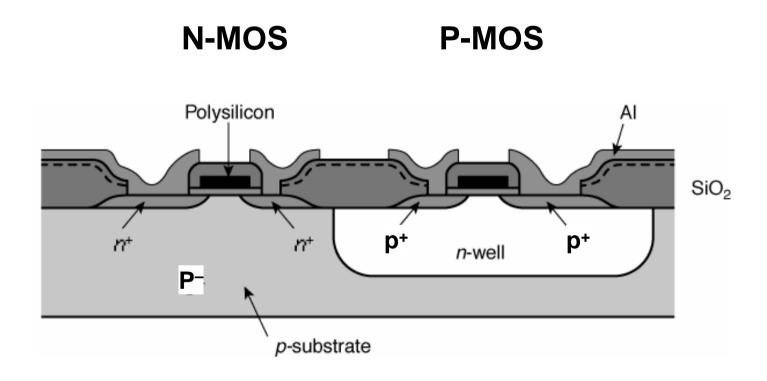

# **Cross-Section of CMOS Technology**

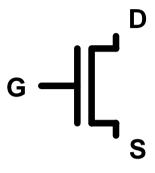

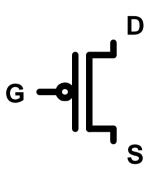

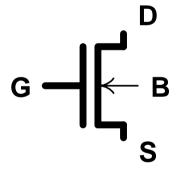

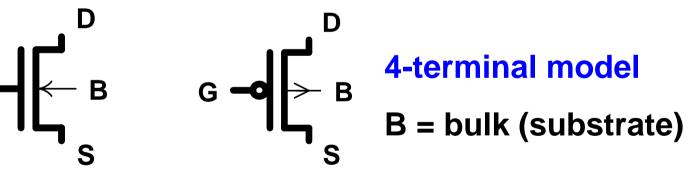

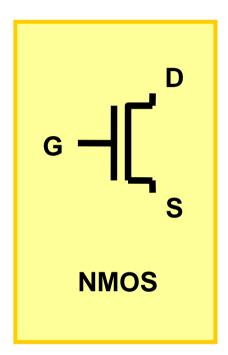

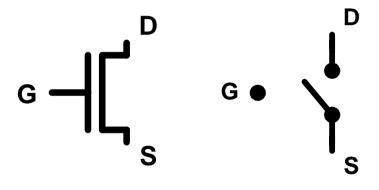

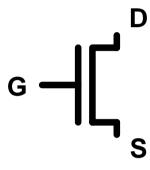

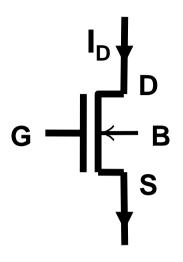

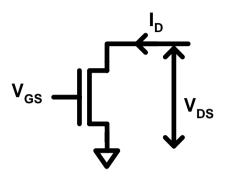

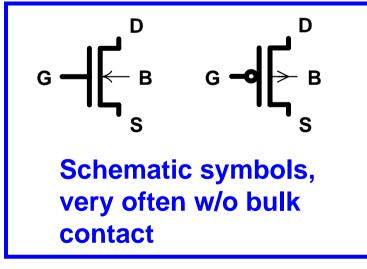

## **MOS Transistors**

3-terminal model

bulk assumed to be connected to appropriate supply

**NMOS**

**PMOS**

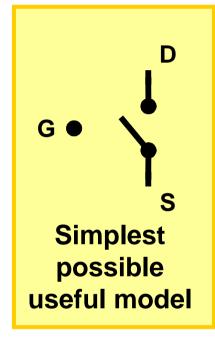

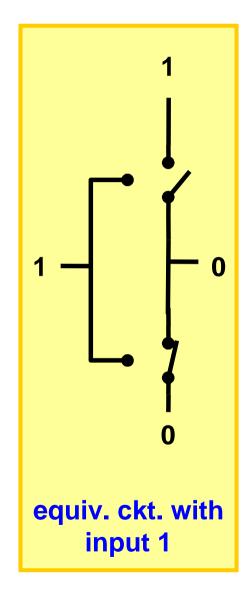

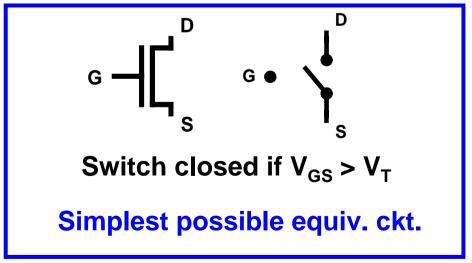

# MOS Transistor Switch Level Models

| Position of switch depends on gate voltage |        |        |  |  |  |

|--------------------------------------------|--------|--------|--|--|--|

| V <sub>G</sub>                             | NMOS   | PMOS   |  |  |  |

| hi                                         | closed | open   |  |  |  |

| lo                                         | open   | closed |  |  |  |

- Connection between source and drain depends on gate voltage, current can flow from source to drain and vice versa if closed

- No static current flows into gate terminal

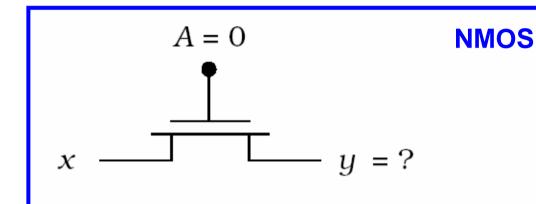

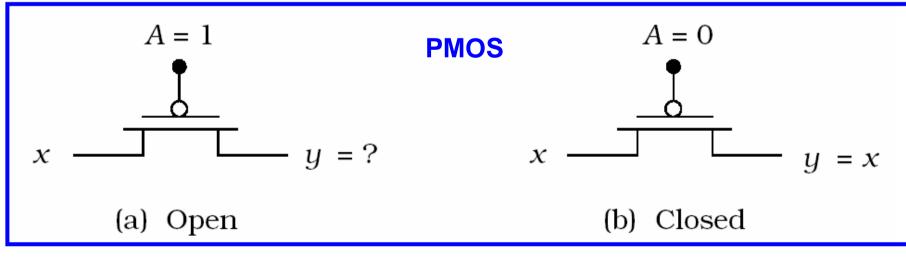

# Mos Switch Model (2)

Position of switch depends on gate voltage

V<sub>G</sub> NMOS PMOS

hi closed open

lo open closed

A = 1 y = x

(a) Open

(b) Closed

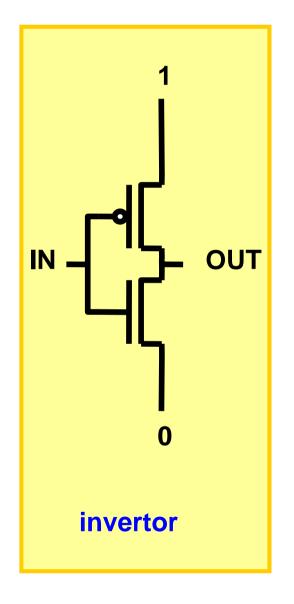

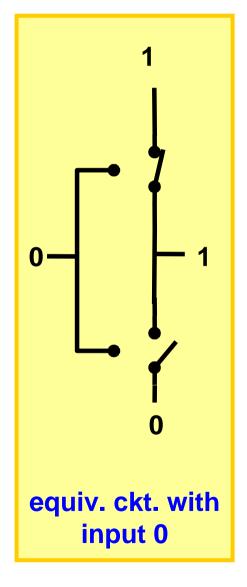

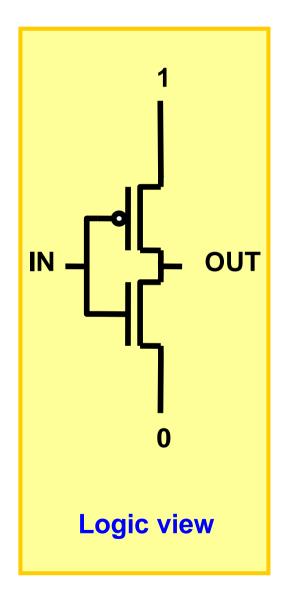

## **CMOS Inverter Operation Principle**

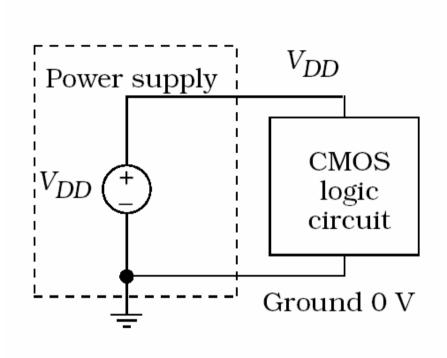

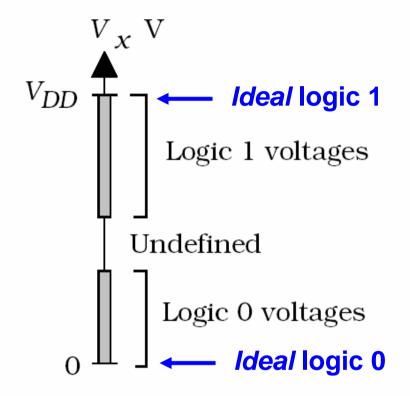

# From Logic to Voltages

(a) Power supply connection

(b) Logic definitions

*Ideal* logic 0 corresponds to  $V_x = 0V$  *Ideal* logic 1 corresponds to  $V_x = V_{DD}$

Not all actual voltages in circuit necessarily correspond to ideal logic levels, see figure (b) above

# From Logic to Voltages

#### Note:

- GND = GROUND = 0V

- Sometimes also called V<sub>ss</sub>

- V<sub>DD</sub> is highest voltage level in circuit

- V<sub>DD</sub> value depends on technology, has been reduced from 5V to 1V and lower over the years

- All voltages  $V_x$  in ckt:  $0 \le V_x \le V_{DD}$

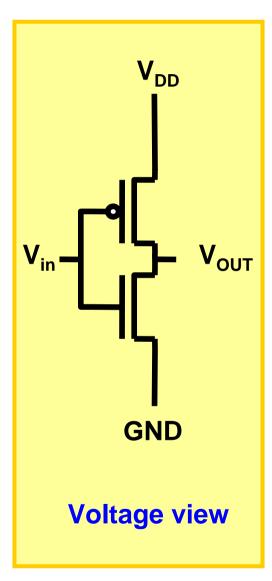

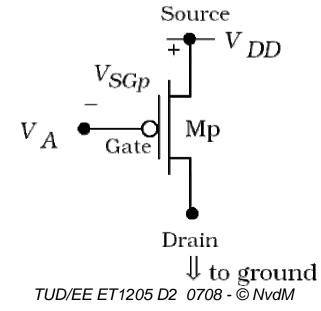

## **Source and Drain Terminals**

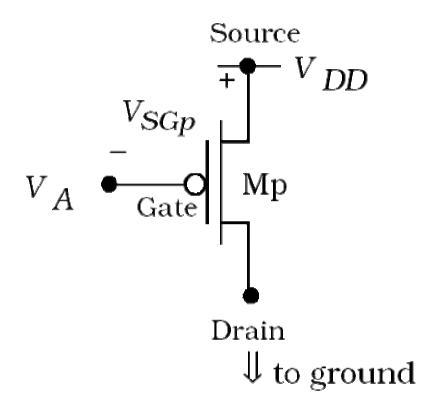

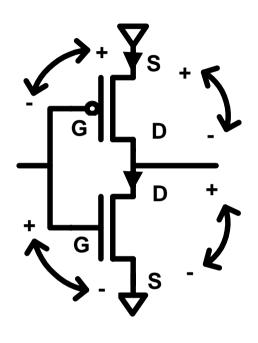

Note 1: Polarities of PMOS voltage reversed when compared to NMOS

Note 2: MOS transistor is completely symmetrical! Can interchange source and drain, without any effect. Source/drain is only a naming convention.

**VSS**

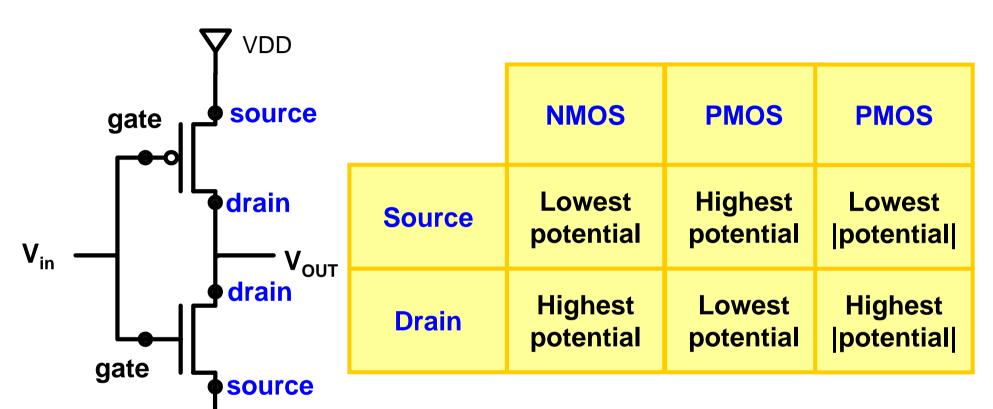

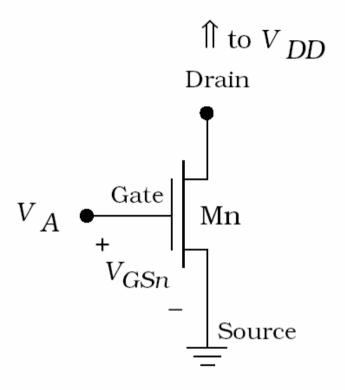

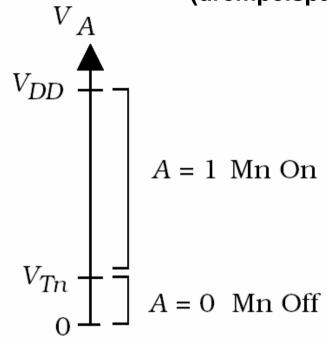

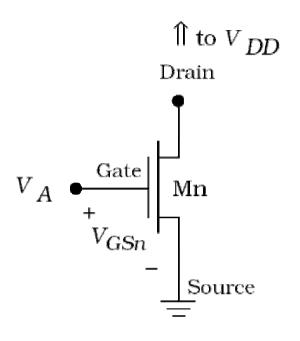

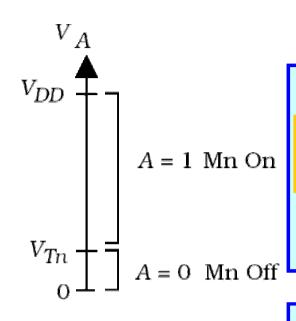

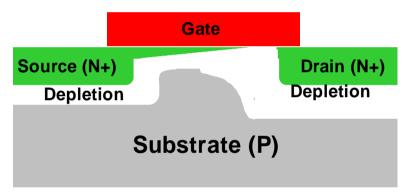

#### nFET Threshold Voltage

(drempelspanning)

(a) Gate-source voltage

$\begin{array}{l} \textbf{nFET} \ \textbf{is off when} \ \textbf{V}_{\textbf{GSn}} \leq \textbf{V}_{\textbf{Tn}} \\ \textbf{nFET is on when} \ \textbf{V}_{\textbf{GSn}} > \textbf{V}_{\textbf{Tn}} \\ \end{array}$

(b) Logic translation

$$V_{Tn} \sim 0.5 \dots 0.7V$$

### pFET Threshold Voltage

$$V_{Tp} \sim -0.5 ... -0.7V$$

(negative!)

Often most useful

nFET is off when  $V_{GSn} \le V_{Tn}$  nFET is on when  $V_{GSn} > V_{Tn}$

pFET and nFET behave complementary

#### **Equivalent conditions**

**pFET** is off when  $V_{GSp} \ge V_{Tp}$ **pFET** is on when  $V_{GSp} < V_{Tp}$

**pFET** is off when  $-V_{GSp} \le -V_{Tp}$ **pFET** is on when  $-V_{GSp} > -V_{Tp}$

**pFET** is off when  $|V_{GSp}| \le |V_{Tp}|$ **pFET** is on when  $|V_{GSp}| > |V_{Tp}|$

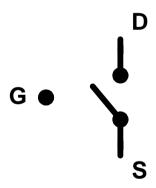

#### **Excercise**

transistor on the left using

nFET is off when  $V_{GSn} \le V_{Tn}$  nFET is on when  $V_{GSn} > V_{Tn}$

corresponds to diagram on right

### Draw same diagram for PMOS using

**pFET** is off when  $-V_{GSp} \le -V_{Tp}$ **pFET** is on when  $-V_{GSp} > -V_{Tp}$

#### **MOS Transistor Treshold Voltage**

Treshold voltage V<sub>T</sub>: point at which transistor turns on

Position of switch depends on gate voltage (relative to source)

V<sub>GS</sub> NMOS PMOS

V<sub>GS</sub>>V<sub>T</sub> closed open

V<sub>GS</sub><V<sub>T</sub> open closed

#### Is this all there is?

- You don't believe that (CMOS) life can be so simple, do you?

- Discuss some of the things that you would expect to be non-idealities of CMOS as a switch

- Since we want to design CMOS circuits, we need a deeper understanding of CMOS circuits

- Next slide shows where we are going

### **MOS Models for Manual Analysis**

determined by circuit

$V_{DS}, V_{GS}, V_{SB}$

determined by technology

k,  $\lambda$ ,  $V_{DSAT}$ ,  $V_{TO}$ ,  $\gamma$ ,  $\phi_F$

#### MOS model for manual analysis

$$I_D = k \left( V_{GT} V_{MIN} - 0.5 V_{MIN}^2 \right) \left( 1 + \lambda V_{DS} \right) \qquad \text{for } V_{GT} \ge 0$$

$$= 0 \qquad \qquad \text{for } V_{GT} \le 0$$

$$V_{MIN} = MIN(V_{DS}, V_{GT}, V_{DSAT})$$

$$V_{GT} = V_{GS} - V_{T}, \qquad V_{T} = V_{T0} + \gamma \left( \sqrt{|-2\phi_{F} + V_{SB}|} - \sqrt{|-2\phi_{F}|} \right)$$

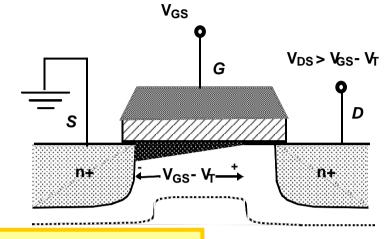

#### **nMOS Transistor Operation**

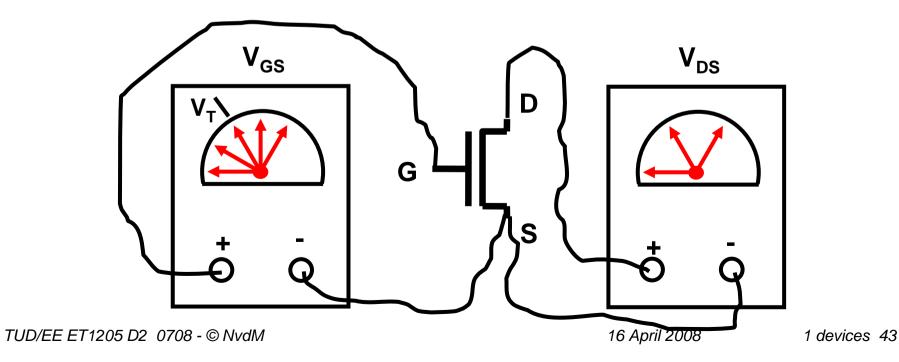

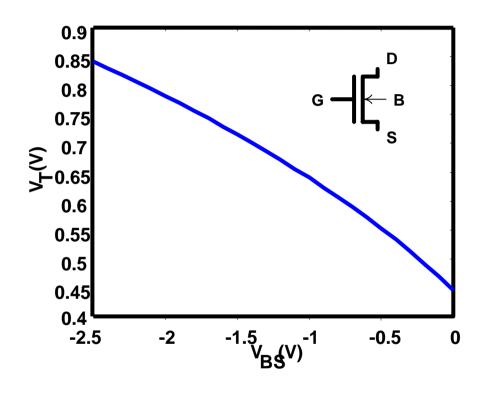

### **Body Effect**

- V<sub>T</sub> is not constant

- Depends on V<sub>S</sub> vs V<sub>B</sub>

- Our wish is to understand & predict behavior of CMOS devices

- We will start with V<sub>T</sub>

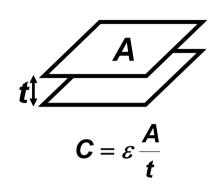

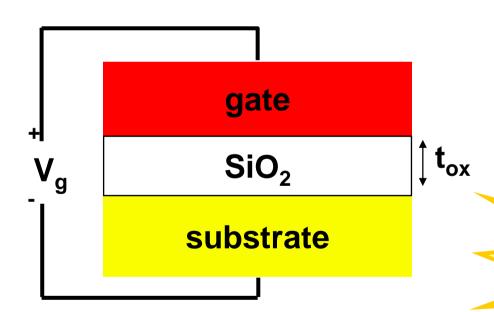

### **MOSFET** gate as capacitor

- Gate capacitance helps determine charge in channel which forms inversion region.

- Basic structure of gate is parallel-plate capacitor:

$$C_{ox} = \varepsilon_{ox} / t_{ox}$$

$$\varepsilon_{ox} = \varepsilon_{0} \varepsilon_{r}$$

$$\epsilon_0 = 8.85 \times 10^{-12} \text{ F/m}$$

$$\varepsilon_r = 3.9 \text{ (SiO}_2)$$

Note: [F] vs. [F/m<sup>2</sup>]

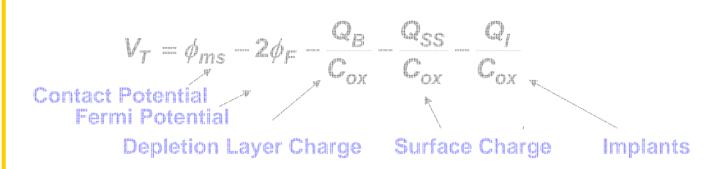

### The Threshold Voltage

With

**Body Effect Coefficient**

#### Forget all this

$$V_T = V_{T0} + \gamma (\sqrt{|-2\phi_F + V_{SB}|} - \sqrt{|-2\phi_F|})$$

But be able to use this

$$V_{10} = \phi_{rrs} - 2\phi_{r} - \frac{Q_{20}}{C_{ox}} \cdot \frac{Q_{55}}{C_{ox}} \cdot \frac{Q_{1}}{C_{ox}}$$

#### and this

### $I_D(V_{GS}, V_{DS}, V_{BS})$

#### MOS model for manual analysis

$$I_D = k \left(V_{GT}V_{MIN} - 0.5V_{MIN}^2\right) \left(1 + \lambda V_{DS}\right)$$

for  $V_{GT} \ge 0$

$= 0$  for  $V_{GT} \le 0$

$V_{MIN} = MIN(V_{DS}, V_{GT}, V_{DSAT})$

- Different operation regions

- Different behavior for each region:

- off

- resistive

- saturation

- velocity saturation

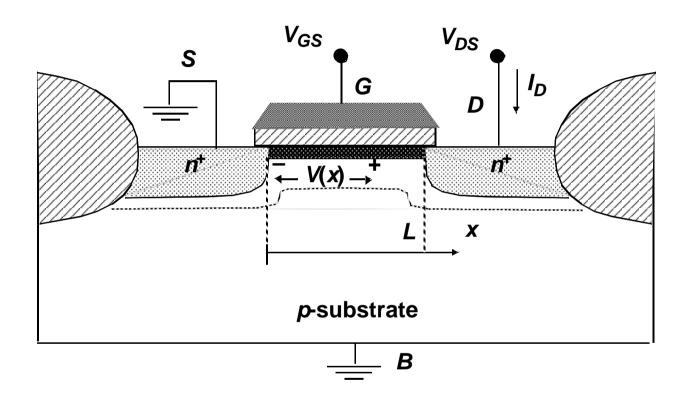

### **Current-Voltage Relations**

MOS transistor and its bias conditions

$$C_{\text{ox}} = \frac{\varepsilon_{\text{ox}}}{t_{\text{ox}}}$$

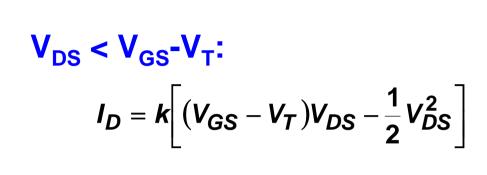

### In Resistive Region

$$Q_i(x) = -C_{ox}[V_{GS} - V(x) - V_T]$$

Inversion Charge

**ID** Drain Current  $\mu_n$  mobility (n-Si)

V dV

$$I_D L = \mu_n C_{ox} W \left[ (V_{GS} - V_T) V - \frac{1}{2} V^2 \right]_0^{V_{DS}}$$

$$\begin{array}{c|c}

S & & V_{DS} \\

\hline

G & & D \\

\hline

- V(X) \rightarrow^{+} & & IT

\end{array}$$

$$I_D = \mu_n C_{ox} \frac{W}{L} \left[ (V_{GS} - V_T) V_{DS} - \frac{1}{2} V_{DS}^2 \right]$$

#### **Process Gain and Device Gain**

$$I_D = \mu_n C_{ox} \frac{W}{L} \left[ (V_{GS} - V_T) V_{DS} - \frac{1}{2} V_{DS}^2 \right]$$

$$\mathbf{k}_{n}' = \mu_{n} \mathbf{C}_{ox} = \mu_{n} \frac{\mathcal{E}_{ox}}{\mathbf{t}_{ox}}$$

$$k = k'_n \frac{W}{L}$$

Process transconductance parameter

**Gain factor of device**

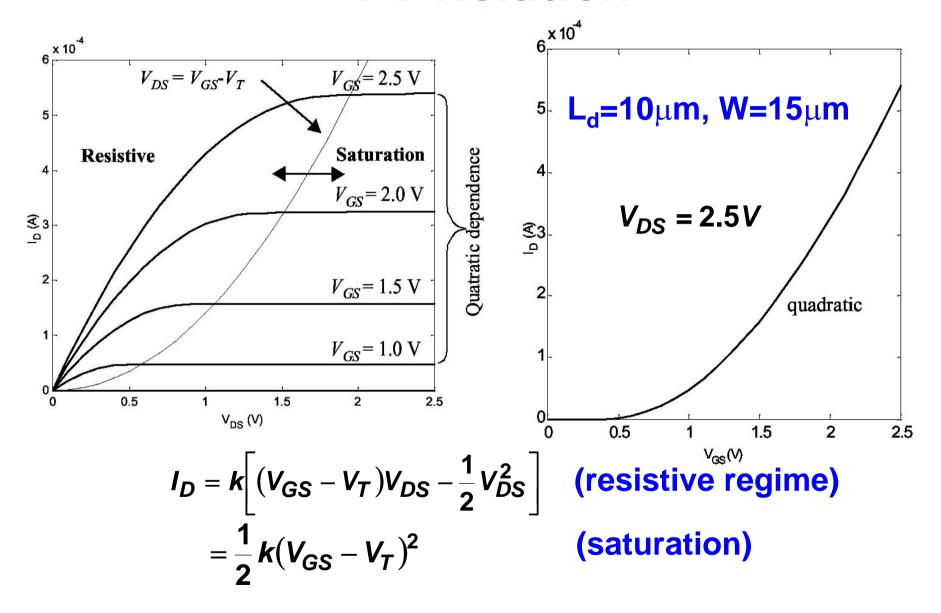

$$I_D = k \left[ (V_{GS} - V_T)V_{DS} - \frac{1}{2}V_{DS}^2 \right]$$

(resistive/linear/ohmic regime)

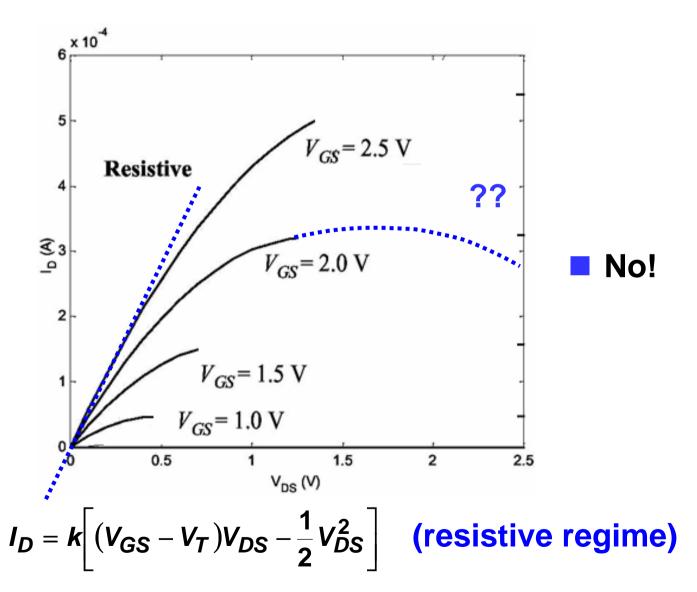

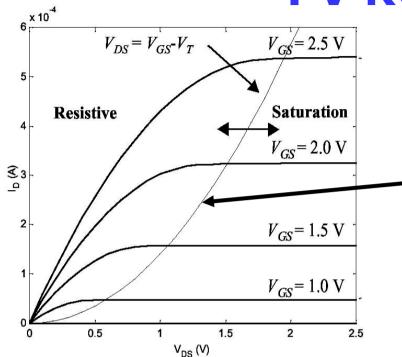

#### **I-V Relation**

#### **I-V Relation**

This curve is where  $I_D$  curves begin to run flat:  $I_D$  does not anymore depend on  $V_{DS}$

$$I_D = k \left[ \left( V_{GS} - V_T \right) V_{DS} - \frac{1}{2} V_{DS}^2 \right]$$

The curve is given by

$$\frac{dI_D}{dV_{DS}} = k \left[ (V_{GS} - V_T) - V_{DS} \right] = 0 \Rightarrow V_{DS} = V_{GS} - V_T$$

The value  $V_{DS} = V_{GS}-V_{T}$  is special: it is the boundary between resistive regime and saturation regime (pinch-off)

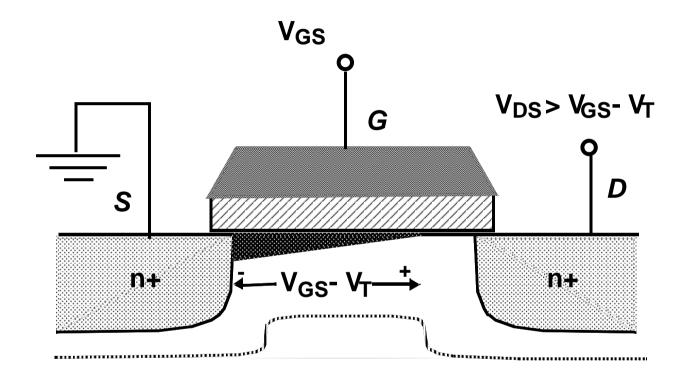

#### **Transistor in Saturation**

#### **I-V** in saturation

**Saturation:**  $V_{DS} > V_{GS} - V_{T}$

#### Current does not increase when $V_{DS} > V_{GS} - V_{T}$

$$I_{DSAT} = I_{D} \Big|_{V_{DS} = V_{GS} - V_{T}}$$

Saturation current

$$I_{DSAT} = k \Big[ (V_{GS} - V_{T})(V_{GS} - V_{T}) - \frac{1}{2}(V_{GS} - V_{T})^{2} \Big]$$

$$= \frac{1}{2} k (V_{GS} - V_{T})^{2}$$

#### **I-V Relation**

### **Output Impedance**

Definition:

$$Z_{out} = \frac{dV_{ds}}{dI_{d}}$$

$$I_D = \frac{1}{2} k (V_{GS} - V_T)^2$$

What is the output impedance?

Is this plausible?

What is happening?

### **Channel Length Modulation**

# **Empirical Model for Effective Channel Length**

$$L_{eff} = \frac{L}{1 + \lambda V_{DS}}$$

$$I_{DSAT} = \frac{1}{2} k'_{n} \frac{W}{L_{eff}} (V_{GS} - V_{T})^{2}$$

$$= \frac{1}{2} k'_{n} \frac{W}{L} (V_{GS} - V_{T})^{2} (1 + \lambda V_{DS})$$

$$= \frac{1}{2} k (V_{GS} - V_{T})^{2} (1 + \lambda V_{DS})$$

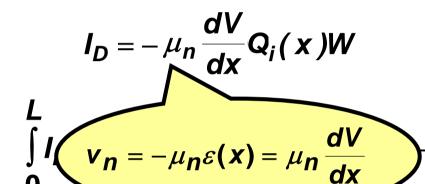

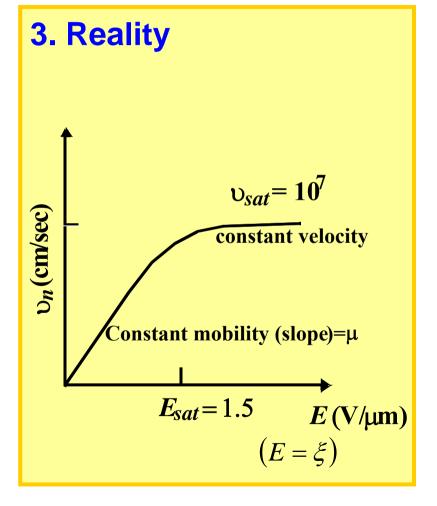

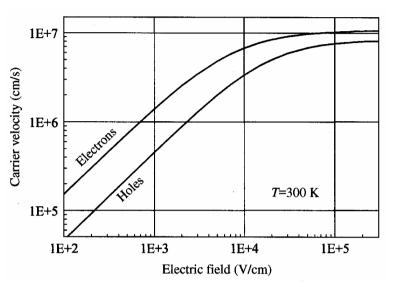

### **Velocity Saturation (1)**

## 1. Still model not complete: need to include effects of limited carrier velocity

## 2. Carrier velocity (ideal model): Linear with field

$$\mathbf{v}_{n} = -\mu_{n}\xi(\mathbf{x}) = \mu_{n}\frac{dV}{d\mathbf{x}}$$

#### 4. Simple v<sub>sat</sub> Model:

$$\mathbf{v_n} = \mu_n \boldsymbol{\xi}$$

for  $\boldsymbol{\xi} \leq \boldsymbol{\xi_c}$

$$= \mu_n \boldsymbol{\xi_c} = v_{sat} \quad \text{for } \boldsymbol{\xi} \geq \boldsymbol{\xi_c}$$

$\xi_c$  Critical Field

**V**<sub>sat</sub> Saturation Velocity

### **Velocity Saturation (2)**

Onset of velocity saturation can be translated into a critical voltage  $V_{DS}$ :  $V_{DSAT}$ . This value depends on L.

#### Velocity saturation parameters

$$V_{DSAT} = L\xi_{c} = \frac{Lv_{sat}}{\mu_{n}}$$

voltage velocity

| L    | V <sub>DSAT</sub> |

|------|-------------------|

| 2    | 3                 |

| 1    | 1.5               |

| 0.25 | 0.375             |

| 0.18 | 0.27              |

|      | •••               |

#### First order, empirical model

$$I_{DSAT} = I_D(V_{DS} = V_{DSAT})$$

$$= k \left[ (V_{GS} - V_T)V_{DSAT} - \frac{1}{2}V_{DSAT}^2 \right] \qquad \text{Velocity Saturation}$$

#### **Overview**

$$I_D = k \left[ (V_{GS} - V_T)V_{DS} - \frac{1}{2}V_{DS}^2 \right]$$

resistive regime base equation

$$=\frac{1}{2}k(V_{GS}-V_{T})^{2}$$

saturation:

$$V_{DS} \rightarrow V_{GS}-V_{T}$$

$$= k \left[ (V_{GS} - V_T) V_{DSAT} - \frac{1}{2} V_{DSAT}^2 \right] \quad \text{velocity sat: } V_{DS} \rightarrow V_{DSAT}$$

$$I_D = I_D' (1 + \lambda V_{DS})$$

**Channel Length Modulation**

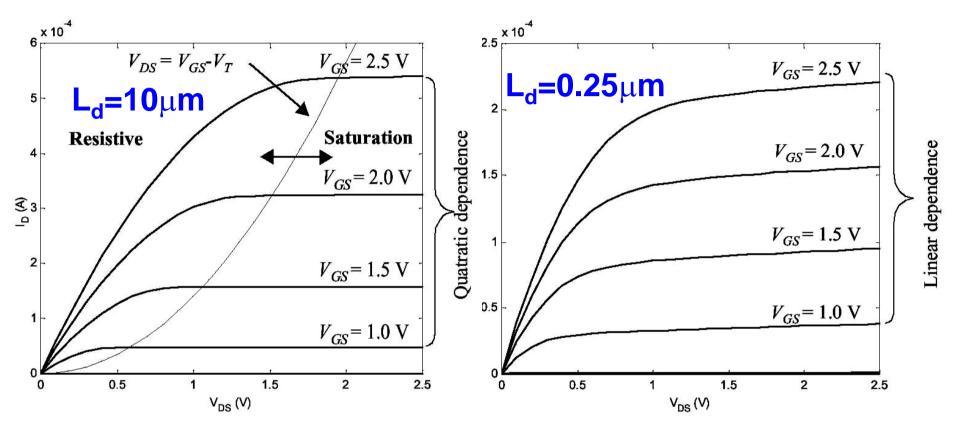

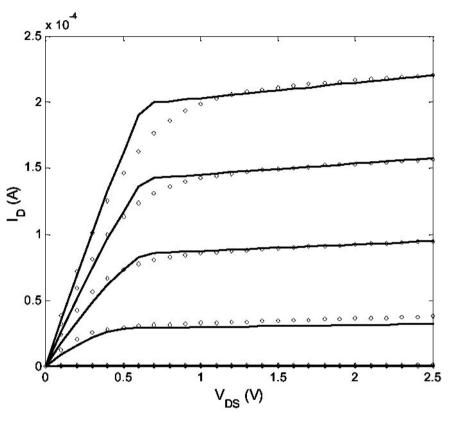

### $I_D$ as a function of $V_{DS}$

Long channel device w/o velocity saturation

Short channel device with velocity saturation

$$W = 1.5L$$

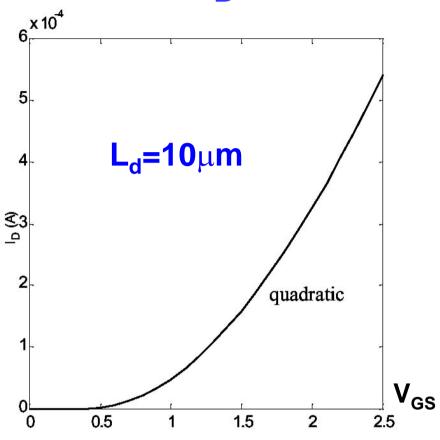

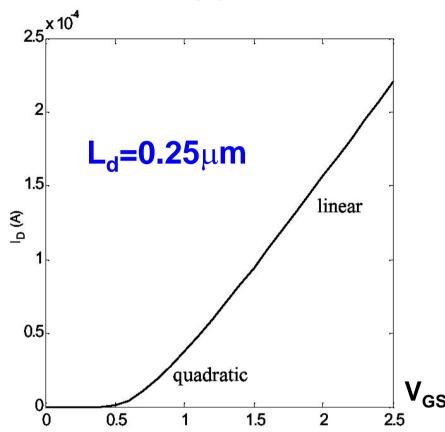

### $I_D$ as a function of $V_{GS}$

Long channel device w/o velocity saturation

$$I_D = \frac{1}{2} k (V_{GS} - V_T)^2$$

Short channel device with velocity saturation

$$I_D = k \left[ (V_{GS} - V_T) V_{DSAT} - 0.5 V_{DSAT}^2 \right]$$

### **MOS Models for Manual Analysis**

#### **Region Specific Models**

$$I_D^{'}=kig(V_{GT}V_{DS}-0.5V_{DS}^2ig)$$

$$oldsymbol{I_D} = oldsymbol{k} ig(oldsymbol{V_{GT}}oldsymbol{V_{GT}} - oldsymbol{0.5}oldsymbol{V_{GT}^2}ig)$$

$$\dot{I_D} = k \left( V_{GT} V_{DSAT} - 0.5 V_{DSAT}^2 \right)$$

$$I_D = I_D' (1 + \lambda V_{DS})$$

Channel length modulation added to resitive region, in order to enforce continuity

**Resistive region**

**Saturation**

**Velocity Saturation**

**Channel Length Modulation**

#### **Comprehensive model**

$$I_D = k \left( V_{GT} V_{MIN} - 0.5 V_{MIN}^2 \right) \left( 1 + \lambda V_{DS} \right) \qquad \text{for } V_{GT} \ge 0$$

$$= 0 \qquad \qquad \text{for } V_{GT} \le 0$$

$$egin{aligned} V_{MIN} &= MIN(V_{DS}, V_{GT}, V_{DSAT}) \ V_{GT} &= V_{GS} - V_{T}, \qquad V_{T} &= V_{T0} + \gamma \left( \sqrt{\left|-2\phi_F + V_{SB}\right|} - \sqrt{\left|-2\phi_F\right|}

ight) \end{aligned}$$

### **MOS Model Comparison**

- Many more far more advanced models do exist (BSIM4 ~ 20k lines of C)

- Are only suited for computer simulation

- The SPICE simulator is the 'good old' workhorse of the industry

- Reliable, but low speed

Solid line: simple model

**Dotted line: SPICE simulation**

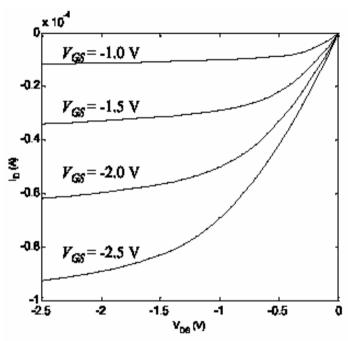

#### **NMOS vs. PMOS**

- $\blacksquare$  PMOS ( $V_{DS}$ ,  $V_{GS}$ ,  $I_{D}$ ,  $V_{T}$ ) < 0

- Can calculate as if NMOS using absolute values

- PMOS device not as strong as NMOS

#### NMOS vs. PMOS (2)

**Zero-field mobility (bulk!)**

Velocity vs. Field

$$\mu_{p} < \mu_{n}$$

$\Rightarrow$   $k'_{p} < k'_{n}$

$v_{sat_{p}} \approx v_{sat_{n}}$   $\Rightarrow$   $|V_{DSAT_{p}}| > |V_{DSAT_{n}}|$

|      | $V_{T0}$ (V) | γ (V <sup>0.5</sup> ) | V <sub>DSAT</sub> (V) | k' (A/V <sup>2</sup> ) | λ (V <sup>-1</sup> ) |

|------|--------------|-----------------------|-----------------------|------------------------|----------------------|

| NMOS | 0.43         | 0.4                   | 0.63                  | 115×10 <sup>-6</sup>   | 0.06                 |

| PMOS | -0.4         | -0.4                  | -1                    | $-30 \times 10^{-6}$   | -0.1                 |

### **Alternative Saturation Expression**

**Saturation** if

$$V_{DS} > V_{GS} - V_T$$

Show that

$$V_{DS} > V_{GS} - V_T \Leftrightarrow V_{GD} < V_T$$

Proof:

$$V_{DS} > V_{GS} - V_T$$

$$\Leftrightarrow V_D - V_S > V_G - V_S - V_T$$

$$\Leftrightarrow V_D > V_G - V_T$$

$$\Leftrightarrow$$

$V_G - V_T < V_D$

$$\Leftrightarrow V_G - V_D < V_T$$

$$\Leftrightarrow V_{GD} < V_T$$

Physically this relates to 'amount of inversion' at drain side

If inversion at drain side disappears: pinch-off

- This is an alternative expression for the saturation region

- Can be handy

### **MOS Device Symmetry**

- MOS transistors are symmetrical

- Strong inversion at source if V<sub>GS</sub> > V<sub>T</sub>

Strong inversion at drain if V<sub>GD</sub> > V<sub>T</sub>

- You should check the I-V relations when interchanging drain and source

- Identification of source drain only by convention

- **Determined by circuit-environment**

|        | NMOS                  | PMOS                  | General             |

|--------|-----------------------|-----------------------|---------------------|

| Source | V <sub>ss</sub> -side | V <sub>DD</sub> -side | Strongest inversion |

| Drain  | V <sub>DD</sub> -side | V <sub>ss</sub> -side | Weakest inversion   |

$V_{SS}$ : low supply voltage,  $V_{DD}$  = high supply voltage

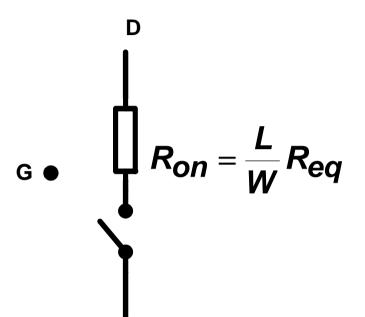

### Improved MOS Transistor Switch Level Model

Position of switch depends on gate to source voltage

| V <sub>GS</sub> | NMOS   | PMOS   |

|-----------------|--------|--------|

| hi              | closed | open   |

| lo              | open   | closed |

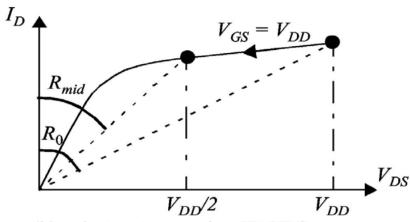

More detailed model may include

- R<sub>on</sub> is highly non-linear

- Make linear approximation R<sub>eq</sub>

- Model with (linear) R<sub>eq</sub> less detailed then previous equation based model, but often useful for first estimates of behavior

### Switch Model Ron

$$V_{DS}: (V_{DD} \rightarrow V_{DD}/2)$$

$$V_{DD} \downarrow I_{D}$$

(a) Schematic

(b) trajectory traversed on ID-VDS curve.

$$R_{eq} = \frac{1}{2} \left[ \frac{V_{DD}}{I_{DSAT} \left( 1 + \lambda V_{DD} \right)} + \frac{V_{DD}/2}{I_{DSAT} \left( 1 + \lambda V_{DD}/2 \right)} \right]$$

$$\frac{1}{1 + \lambda V_{DD}} \approx 1 - \lambda V_{DD} + O(\lambda^2 V_{dd}^2)$$

2.3% error with

$$\lambda = 0.06 \text{ V}^{-1}, V_{DD} = 2.5 \text{ V}$$

$$R_{eq} \approx \frac{1}{2} \frac{V_{DD}}{I_{DSAT}} \left( 1 - \lambda V_{DD} + \frac{1}{2} (1 - \lambda V_{DD} / 2) \right)$$

$$= \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \left[ 1 - \frac{5}{6} \lambda V_{DD} \right]$$

### **Theory!**

### MOS Transistor Switch Level Model (Empirical).

Position of switch depends on gate to source voltage

| V <sub>GS</sub> | NMOS   | PMOS   |

|-----------------|--------|--------|

| hi              | closed | open   |

| lo              | open   | closed |

R<sub>eq</sub>: Practice!

| R <sub>eq</sub> \ V <sub>dd</sub> (V) | 1   | 1.5 | 2  | 2.5 |

|---------------------------------------|-----|-----|----|-----|

| NMOS ( $k\Omega$ )                    | 35  | 19  | 15 | 13  |

| PMOS (kΩ)                             | 115 | 55  | 38 | 31  |

#### **The MOS Transistor Summary**

### The MOS Transistor Summary ctd.

- Need to analyze speed, power, noise etc of MOS circuits

- Simple switch-level model not sufficient

- Study exact operation to derive more precise IV relations

$$I_D = k \left(V_{GT}V_{MIN} - 0.5V_{MIN}^2\right)\left(1 + \lambda V_{DS}\right)$$

for  $V_{GT} \ge 0$

= 0 for  $V_{GT} \le 0$

$$egin{aligned} V_{MIN} &= MIN(V_{DS}, V_{GT}, V_{DSAT}) \ V_{GT} &= V_{GS} - V_{T}, \qquad V_{T} &= V_{T0} + \gamma \Big( \sqrt{\left|-2\phi_F + V_{SB}

ight|} - \sqrt{\left|-2\phi_F

ight|} \Big) \end{aligned}$$

### **Summary**

- Semiconductor Physics

- The diode

- Depletion, I-V relations, capacitance, secondary effects, models

- The MOS transistor

- First glance, threshold, I-V relations, models

- Dynamic behavior (capacitances), resistances, more Second-Order effects, models