# **MODULE 7**

# TIMING DESIGN

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

7 timing 1

# **Outline**

- Timing Design Background and Motivation

- Delay variations, impact

- Sequential circuits, synchronous design

- Pipelining, metrics reminder

- The Clock Skew Problem

- Controlling Clock Skew

- Case Study

Get basic appreciation of some system level design issues

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

# **Design of LARGE Integrated Circuits**

- Correct signal

- Logic value

- Right level (restoring logic, ...)

- At right place

- Interconnect (R, C, L)

- Busses

- Off-chip drivers, and receivers

- At right time

- How to cope with (uncertain) delay

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

7 timing 3

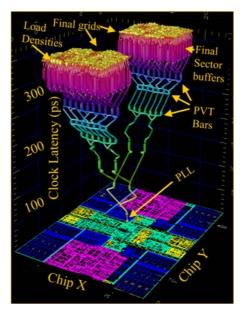

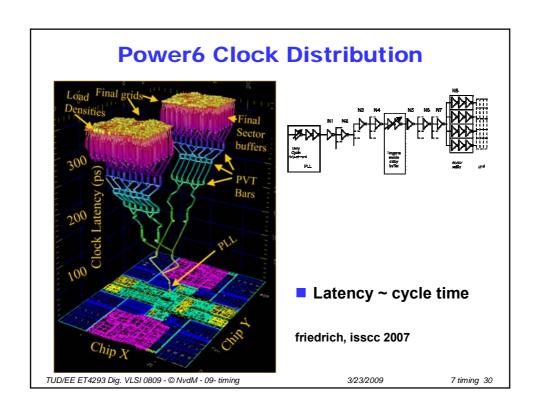

# Case Study: IBM Power6 CPU introduced 21 may 2007 CORE 64 bit, dual core 790 million transistors 4.7 (5+) GHz 65nm SOI, 10 Cu levels interconnect 2 Cores 8 MB on-chip level2 cache processor bandwidth: 300GB/sec CORE ■ 1953 signal I/O, 5449 power I/O http://www-03.ibm.com/press/us/en/pressrelease/21580.wss TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

7 timing 5

# **Uncertain Delay**

- Data-dependent Delay

- Short and long combinational paths

- Device parameters variations (§3.4)

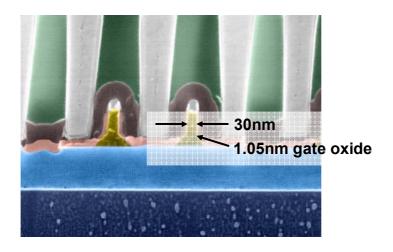

Batch to batch V<sub>t</sub> threshold voltage Wafer to wafer k' transconductance Die to die W, L dimensions

- Supply VariationsIR drop, dl/dt drop, ringing,

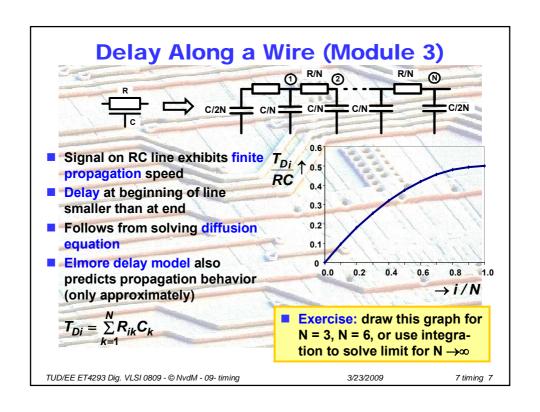

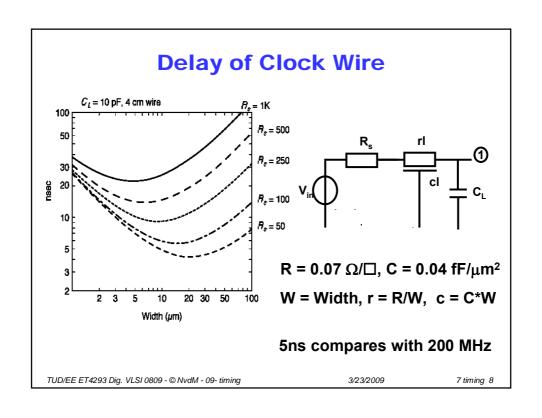

- Interconnect Delay Don't know length of line during logic design Delay at begin of line smaller than at end Interconnect parameter variability

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

# **Impact of Uncertain Delay**

- Combinational circuits will eventually settle at correct output values when inputs are stable

- Sequential circuits

- **■** Have state

- Must guarantee storing of correct signals at correct time

- Require ordered computations

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

# **Sequential Circuits**

- Sequential circuits require ordered computation

- Several ways for imposing ordering

- **∨** Synchronous (clock)

- **X** Asynchronous (unstructured)

- **X** Self-timed (negotiation)

Clock works like an orchestra conductor

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

7 timing 11

# **Synchronous Design**

- Global Clock Signal

- Synchronicity may be defeated by

- Delay uncertainty in clock signal

- Relative timing errors: clock skew

- Slow logic paths

- Fast logic paths

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

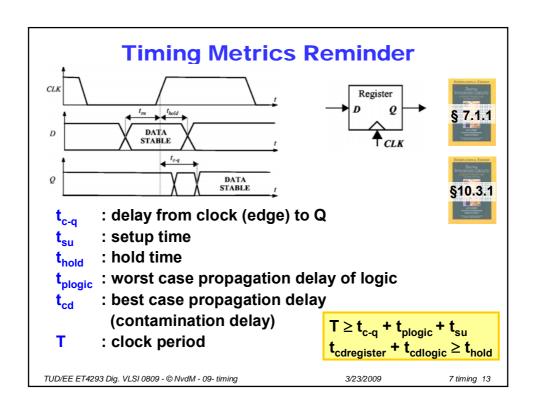

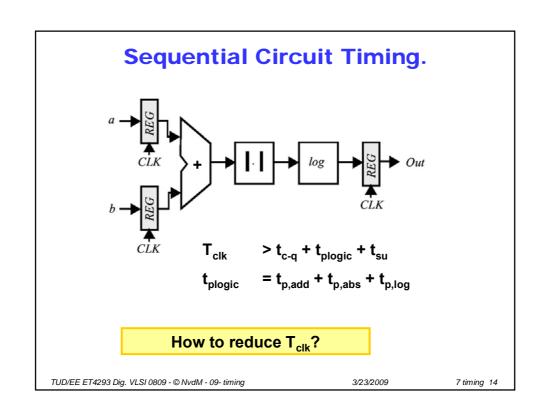

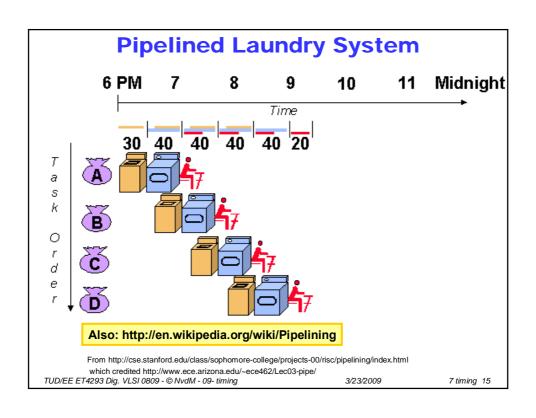

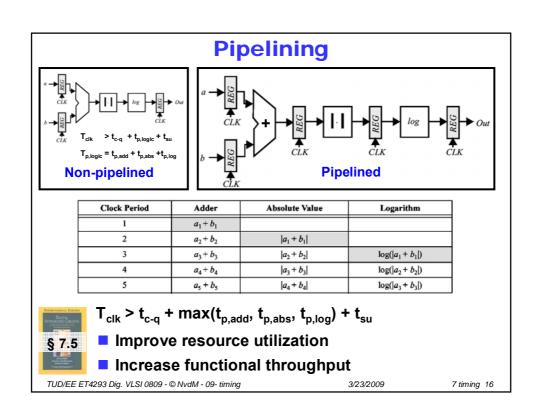

# **Pipelining Observations**

- Very popular/effective measure to increase functional throughput and resource utilization

- At the cost of increased latency

- All high performance microprocessors excessively use pipelining in instruction fetch-decode-execute sequence

- Pipelining efficiency may fall dramatically because of branches in program flow

- Requires emptying of pipeline and restarting

- Partially remedied by advanced branch prediction techniques

- But all is dictated by GHz marketing drive

- All a customer asks is: "How many GHz?"

- Or says: "Mine is ... GHz!"

Bottom line: more flip-flops, greater timing design problems

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

7 timing 17

# The Clock Skew Problem

- In Single Phase Edge Triggered Clocking

- In Two Phase Master-Slave Clocking

(Also: Katz § 6.2.2)

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

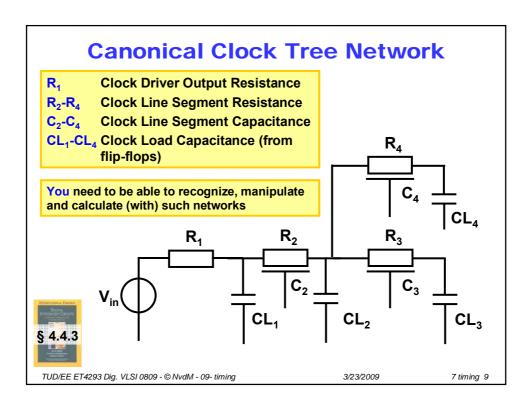

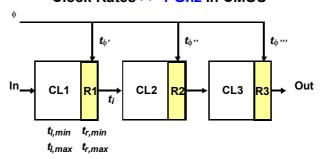

## **The Clock Skew Problem**

#### Clock Rates >> 1 Ghz in CMOS

- Clock Edge Timing Depends upon Position

- Because clock network forms distributed RC line with lumped load capacitances at multiple sites (see earlier slide)

- (Relative) Clock Skew  $\delta = \mathbf{t}_{\phi}$ ,  $-\mathbf{t}_{\phi}$

- Clock skew can take significant portion of T<sub>clk</sub>

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

7 timing 19

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

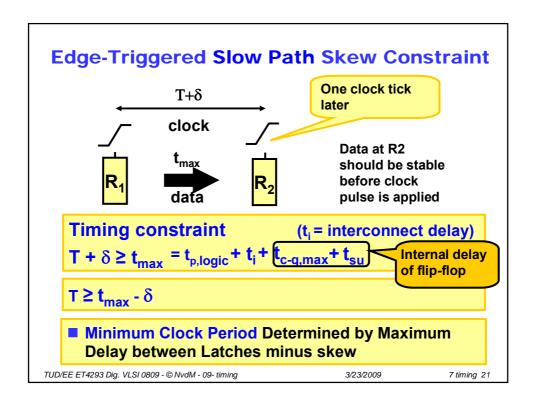

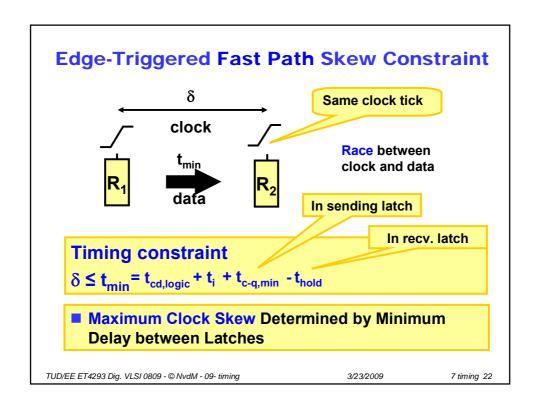

# **Clock Constraints in Edge-Triggered Logic**

$T \ge t_{max} - \delta$

$\delta \le t_{\min}$

#### **■ Observe:**

- Minimum Clock Period Determined by Maximum Delay between Registers minus clock skew

- Maximum Clock Skew Determined by Minimum Delay between Registers

- **Conclude:**

- Positive skew must be bounded

- Negative skew reduces maximum performance

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

7 timing 23

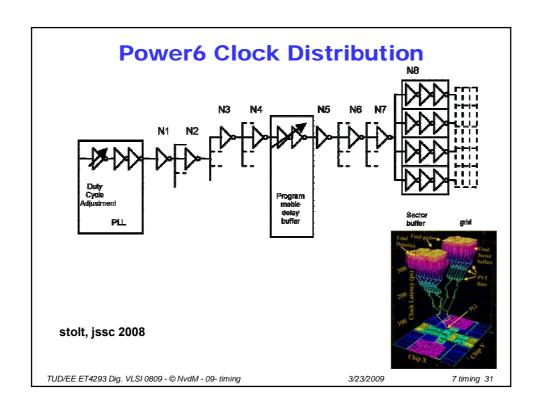

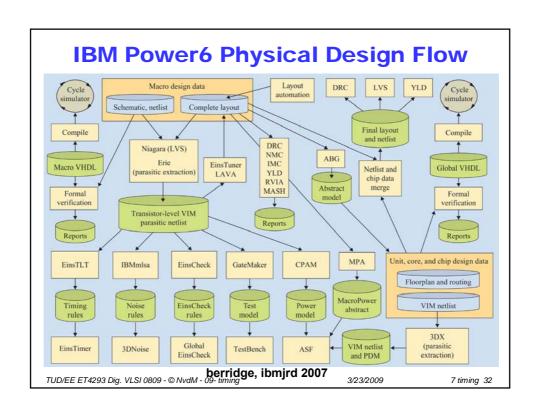

# **Controlling Clock Skew Case Study**

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

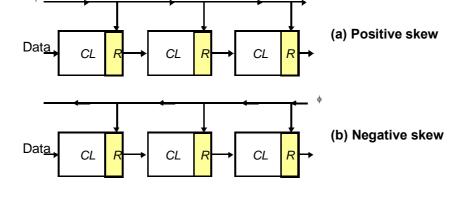

# **Countering Clock Skew Problems**

- Routing the clock in opposite direction of data (negative skew)

- Hampers performance

- Dataflow not always uni-directional

- Maybe at sub circuit (e.g. datapath) level

- Other approaches needed at global chip-level

- Useful skew (or beneficial skew) is serious concept

- Enlarging non-overlap periods of clock [only with two-phase clocking]

- Hampers performance

- Can theoretically always be made to work

- Delay in clock network may require impractical/excessively large scheduled T<sub>φ12</sub> to guarantee minimum T<sub>φ12</sub> everywhere across chip

- Is becoming less popular for large high performance chips

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

7 timing 25

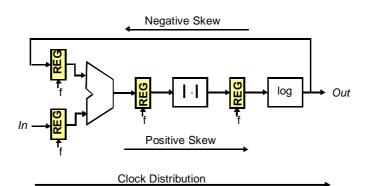

# **Dataflow not unidirectional**

- Data and Clock Routing

- Cannot unambiguously route clock in opposite direction of data

- Need bounded skew

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

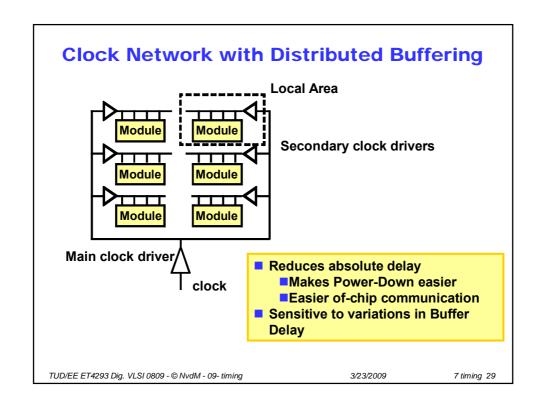

## **Need bounded Skew**

- Bounded skew most practical measure to guarantee functional correctness without reducing performance

- Clock Network Design

- Interconnect material

- Shape of clock-distribution network

- Clock driver, buffers

- Clock-line load

- Clock signal rise and fall times

- **...**

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

7 timing 27

# H-tree Clock Network All blocks equidistant from clock source ⇒ zero (relative) skew Sub blocks should be small enough to ignore intra-block skew In practice perfect H-tree shape not realizable CLOCK Observe: Only Relative Skew Is Important TUD/EE ET4293 Dig. VLSI 0809 - ⊕ NvdM - 09- timing 3232009 7 timing 28

# **Timing Design**

- Clocking Scheme is important design decision

- Influences

- Power

- Robustness

- Ease of design, design time

- Performance

- Area, shape of floor plan

- Needs to be planned early in design phase

- But is becoming design bottle neck nevertheless

- Clock frequencies increase

- Die sizes increase

- Clock skew significant fraction of T<sub>clk</sub>

- Alternatives

- Asynchronous or self-timed

Not in this course

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009

# **Summary**

- Timing Design Background and Motivation

- Delay variations, impact

- Sequential circuits, synchronous design

- Pipelining, metrics reminder

- The Clock Skew Problem

- Controlling Clock Skew

- Case Study

Got basic appreciation of some system level design issues?

TUD/EE ET4293 Dig. VLSI 0809 - © NvdM - 09- timing

3/23/2009