# SEQUENTIAL ELEMENTS

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

## **Sequential Elements - Outline**

- Background

- Timing, terminology, classification

- Static Flipflops

- Latches

- Registers

- Dynamic Flipflops

- **III** Latches

- Registers

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

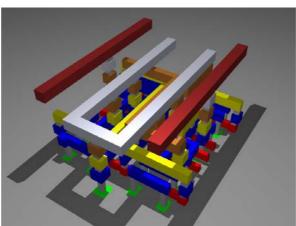

# FSM with Positive Edge Triggered Registers

- Flip-flops provide memory/state

- VLSI uses predominantly D-type flip-flops

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/200

### **Memory elements**

- Store a temporary value, remember a state

- Typically controlled by clock.

- May have load signal, etc.

- In CMOS, memory is created by:

- capacitance (dynamic);

- feedback (static).

- Also see http://en.wikipedia.org/wiki/Flip-flop\_(electronics)

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

#### **Variations in memory elements**

- Form of required clock signal.

- How behavior of data input around clock affects the stored value.

- When the stored value is presented to the output.

- Whether there is ever a combinational path from input to output.

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

5

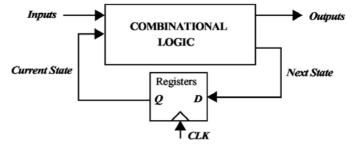

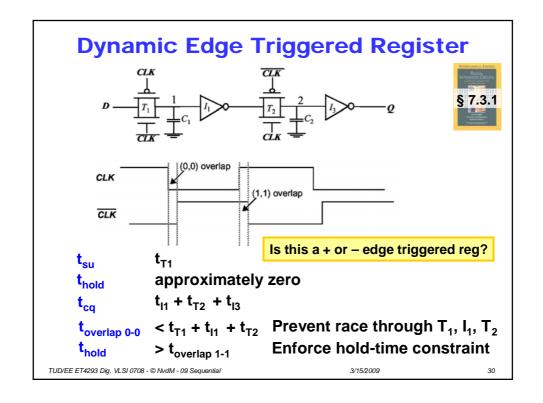

$t_{plogic}$ : worst case propagation delay of logic

t<sub>cd</sub>: best case propagation delay

(contamination delay)

T: clock period

$\begin{aligned} & T \geq t_{c-q} + t_{plogic} + t_{su} \\ & t_{cdregister} + t_{cdlogic} \geq t_{hold} \end{aligned}$

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

#### Latches vs. Registers

#### Latch

Level-sensitive

Transparent when clock is active

Clock active high: positive latch

Clock active low: negative latch

Faster, smaller

#### **Register**

**Edge-triggered**

Input and output isolated

Sampling on 0 → 1 clock: positive edge triggered

Sampling on 1 → 0 clock: negative edge triggered

Safer

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

7

#### **Static vs. Dynamic Memory Elements**

#### **Static**

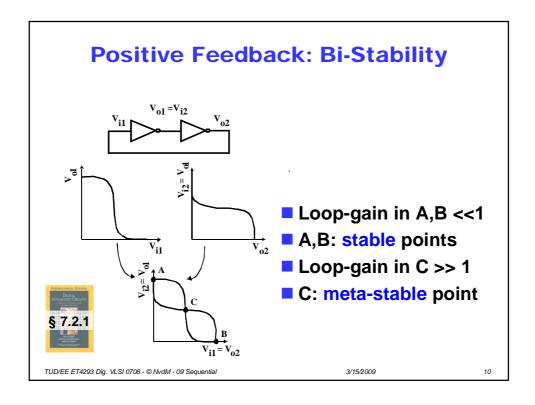

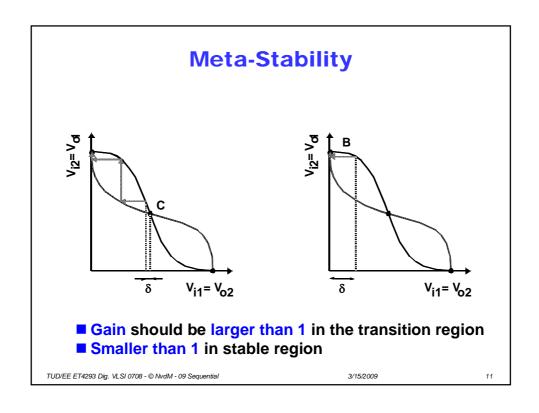

Operate through positive feedback

Preserve state as long as power is on

Can work when clock is off

More robust

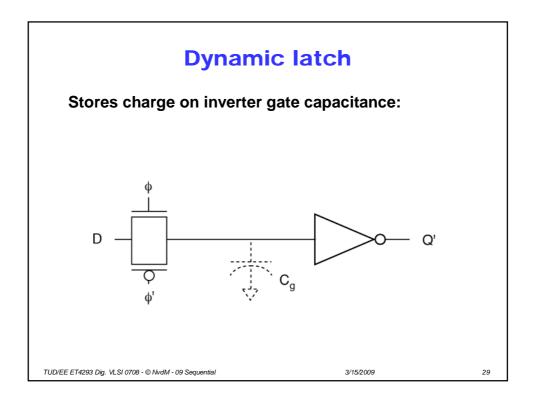

#### **Dynamic**

Store charge on (parasitic) capacitor

Charge leaks away (in milliseconds)

Clock must be kept running (for periodic refresh)

Faster, smaller

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

# **Static Flipflops**

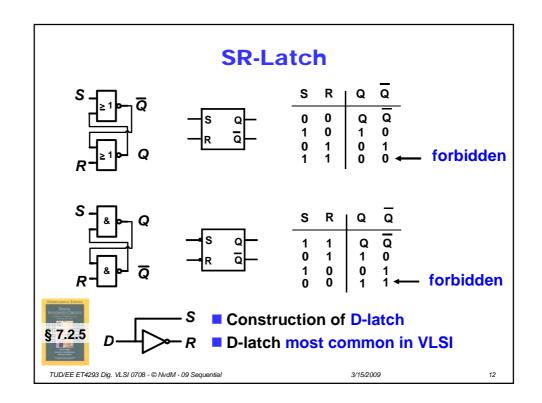

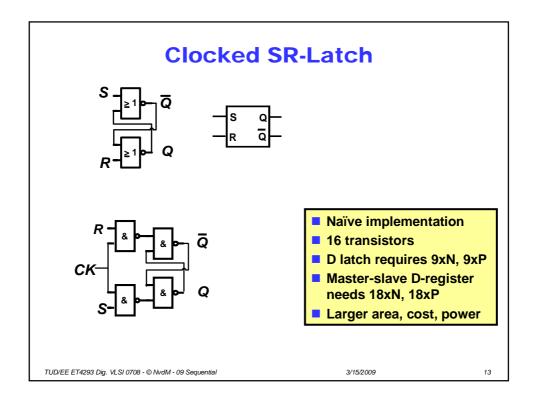

- **■**Latches

- **Registers**

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

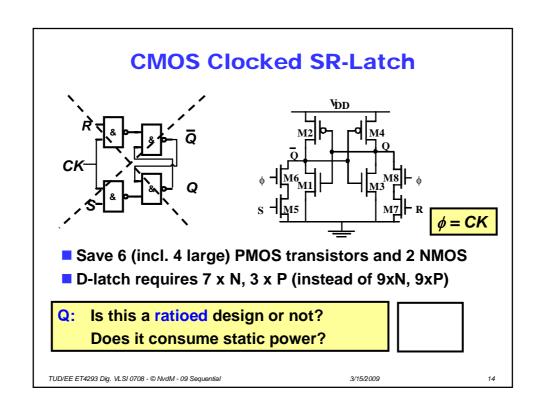

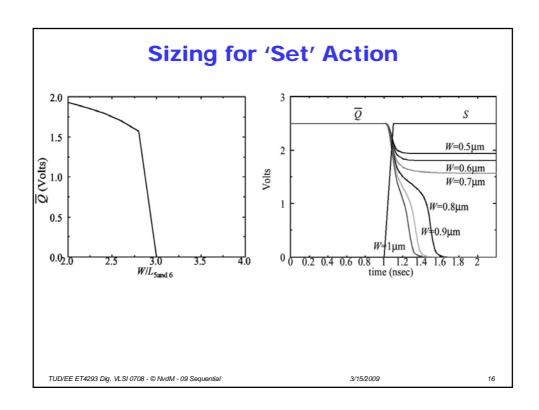

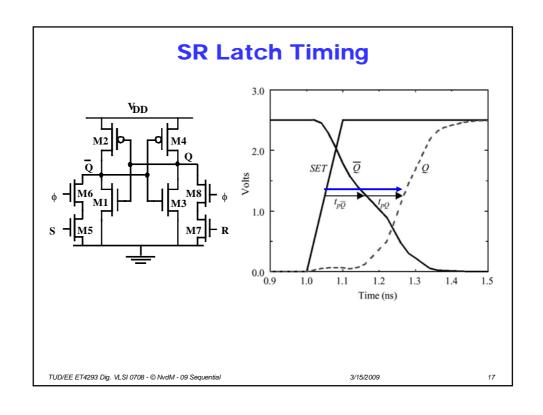

#### Sizing for 'Set' Action

- M<sub>3</sub>-M<sub>4</sub> form conventional inverter

- Model M<sub>5</sub>-M<sub>6</sub> as one equivalent (double length) transistor  $M_{56}$ Assume Q = 0  $\rightarrow$   $M_1$  is off,  $M_2$  is on

- M<sub>2</sub>-M<sub>56</sub> operate like ratioed pseudo **NMOS** inverter

- Latch switches when M<sub>56</sub> pulls input of M<sub>3</sub>-M<sub>4</sub> below their switching threshold (assume V<sub>DD</sub>/2)

- Positive feedback amplifies switching

- M<sub>2</sub> and M<sub>56</sub> both in velocity saturation around  $V_Q = V_{DD}/2$

$$k'_{n} \left(\frac{W}{L}\right)_{5-6} \left( (V_{DD} - V_{Tn}) V_{DSATn} - \frac{V_{DSATn}^{2}}{2} \right) = k'_{p} \left(\frac{W}{L}\right)_{2} \left( (-V_{DD} - V_{Tp}) V_{DSATp} - \frac{V_{DSATp}^{2}}{2} \right)$$

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

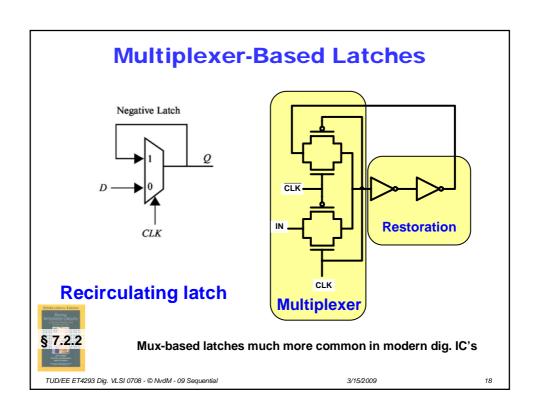

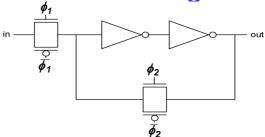

### **Recirculating latch**

- Quasi-static, static on one phase

- Feedback restores value

- Requires 4 x N, 4 x P, minimum size (compare 7 x N, 3 x P, non-minimum size)

- lacktriangledown  $\phi_1$  and  $\phi_2$  inverse but should be non-overlapping

- Can suffer from charge sharing (when  $\phi$  not non-overlapping)

- Output connected directly to input

- C<sub>in</sub> and C<sub>load</sub> form communicating vessels

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

19

### **Insensitive for Charge Sharing**

■ Non ratioed

Uni-directionality of this inverter prevents coupling between Q and D

High load to CLK

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

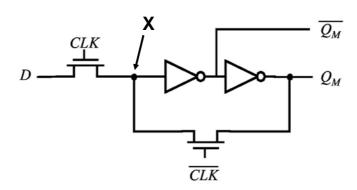

# **Recirculating NMOS Latch.**

- Degraded 1 at X

- Lower noise margin, higher delay, power

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

21

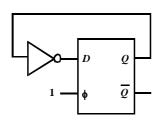

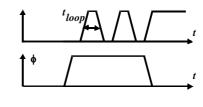

# Latch Designs can Suffer from Race Problems

# Signal can race around during $\phi = 1$

§ 7.2.3

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

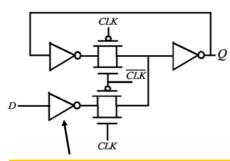

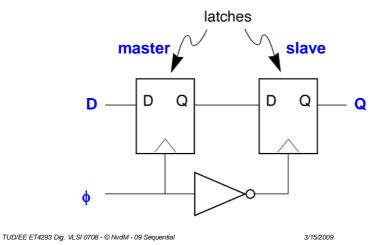

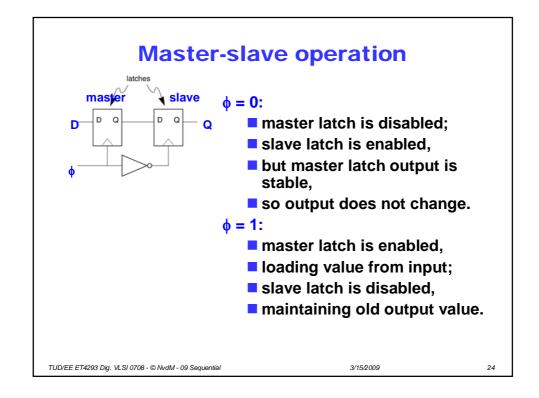

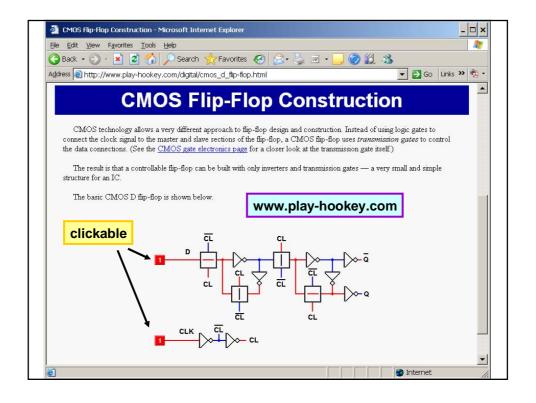

- Not transparent—use multiple storage elements to isolate output from input.

- Master-slave, edge triggered principle

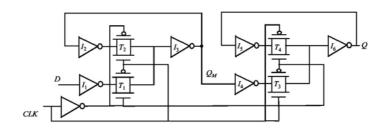

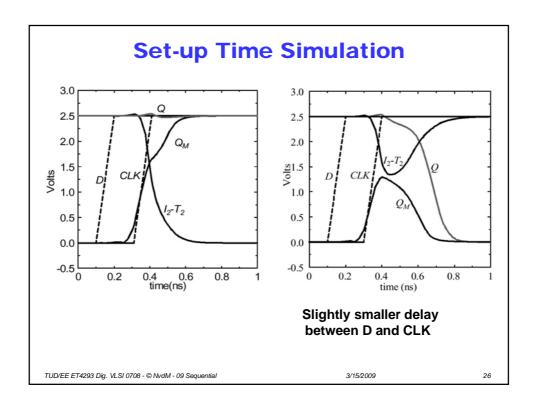

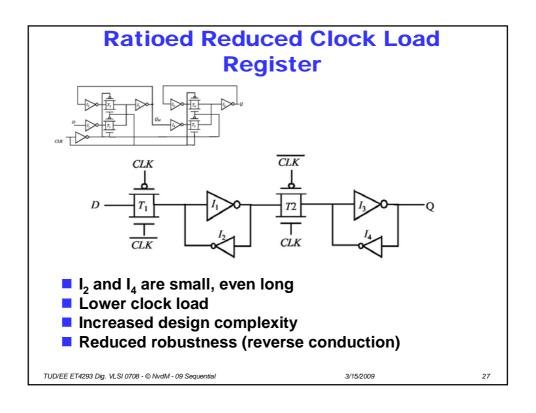

# **Transistor Level Master Slave Positive Edge Triggered Register**

- Robust Design

- Can eliminate I<sub>1</sub> and I<sub>4</sub>, however, they make design more robust (avoid charge sharing, robust input)

- High Clock Load (8 x)

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009

# **Summary**

- Background

- Timing, terminology, classification

- Static Flipflops

- Latches

- Registers

- Dynamic Flipflops

- Latches

- Registers

TUD/EE ET4293 Dig. VLSI 0708 - © NvdM - 09 Sequential

3/15/2009