TR 200511 S

# Propositions accompanying the thesis Trade-offs in Buffer Planning

by Giuseppe Garcea

- 1. It is anachronistic to focus exclusively on speed optimization of chip interconnect without taking into account the actual design costs.

- 2. The final result of an optimization problem knows two critical moments that only depend on the experience and the ability of the designer. The first is the translation of a problem in a standard form solvable by computer, the second is the interpretation of the solution.

- 3. In selecting design points, simplicity prevails over accuracy.

- 4. Now that process technology has become very difficult to tune, robust design is the only way to reduce costs and increase yield.

- 5. The true scientist is similar to an artist. Their ideas gush from the same creative source and both aim at producing something inspiring. However, the radical difference between them lies in the fact that the first has the moral duty to produce something reproducible, while the second is only interested in making something unique.

- 6. Fatalism and sense of mystery, which are intrinsic to our lives, prevent our mind from falling asleep. In fact, if everything is always as foreseen and programmed, there can be no curiosity in life.

- 7. "Laws are like spider webs. If some poor weak creature comes up against them it is caught. But the bigger one can break through and get away" (Solon, 594 B.C.). In older and in modern society authorities can circumvent the judicial system.

- 8. Communication anytime anywhere has changed our social relations. It brought faraway people closer together, and moved neighbors farther apart.

- 9. The business strategy to gain market by sinking the opponents using legal litigation wars will in the end have adverse results for the customers. In the long term, the investment in lawyer bills will consume precious resources that should be used to enhance the quality of the product.

- 10. The Dutch proverb "Een goede buur is beter dan een verre vriend" ("A good neighbor is worth more than a distant friend"), confuses the concept of friendship with that of pragmatic usage of favors for convenience. In fact "The true friendship is not slave of time and space, the material distance cannot separate us from our friends!" (Richard Bach)

# Stellingen behorende bij het proefschrift

## Trade-offs in Buffer Planning

door Giuseppe Garcea

- Het is niet meer van deze tijd om zich bij het ontwerpen van chips alleen op snelheidsoptimalisatie van verbindingen te richten en geen rekening te houden met de actuele ontwerpkosten.

- 2. Het eindresultaat van een optimalisatieprobleem hangt af van twee kritieke momenten die uitsluitend worden bepaald door de ervaring en bekwaamheid van de ontwerper. Het eerste is de vertaling van een probleem in een standaard vorm die opgelost kan worden met een computer, en het tweede is de interpretatie van de oplossing.

- 3. Bij het selecteren van een ontwerppunt prevaleert eenvoud boven nauwkeurigheid.

- Aangezien procestechnologieën steeds moeilijker op elkaar af te stemmen zijn, is robuust ontwerpen de enige manier om kosten te verminderen en opbrengst te vergroten.

- 5. Een echte wetenschapper lijkt op een artiest. Beiden putten hun ideen uit dezelfde bron van creativiteit en beiden proberen iets inspirerends te maken. Het grote verschil is dat de eerste de morele plicht heeft iets reproduceerbaars te maken, terwijl de tweede alleen genteresseerd is in het maken van iets unieks.

- 6. Fatalisme en het gevoel van mysterie horen bij het leven en zorgen ervoor dat onze hersenen niet in slaap vallen. Als alles altijd was zoals voorzien en geprogrammeerd, dan zou het leven oninteressant zijn.

- 7. "Wetten zijn net spinnenwebben. Als een zwak wezen erin terecht komt, zit hij gevangen. Maar een sterker wezen kan eruit ontsnappen en wegvliegen" (Solon, 594 B.C.). Zowel in het verleden als in de moderne maatschappij kunnen de autoriteiten het gerecht omzeilen.

- Communicatie waar dan ook, en op welk tijdstip dan ook, heeft onze sociale contacten veranderd. Het heeft mensen van ver dichter bij elkaar gebracht en mensen van dichtbij van elkaar verwijderd.

- 9. De business-strategie om marktaandeel te winnen door de concurrentie uit te schakelen d.m.v. een juridisch gevecht, uit zich uiteindelijk niet in een positief resultaat voor de klant. Op de lange termijn zullen de advocaatskosten geput moeten worden uit de bronnen die eigenlijk bedoeld zijn voor het verbeteren van de kwaliteit van het product.

- 10. Het Nederlandse gezegde: "Een goede buur is beter dan een verre vriend", verwart vriendschap met baat hebben bij gebruik maken van elkaars gunsten. Inderdaad, "Echte vriendschap is niet onderhevig aan tijd en plaats. Geografische afstand kan ons niet scheiden van onze vrienden!". (Richard Bach)

Deze stellingen worden verdedigbaar geacht en zijn als zodanig goedgekeurd door de promotor, Prof. dr. ir. R.H.J.M. Otten.

# Trade-offs in buffer planning

### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus, prof.dr.ir. J.T. Fokkema, voorzitter van het College voor Promoties, in het openbaar te verdedigen

op maandag 27 june 2005 om 13.00 uur

door

Giuseppe Stefano Garcea

Ingegnere elettronico, Università degli Studi di Firenze, Italië geboren te Taranto (Italië)

Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. ir. R.H.J.M. Otten

Samenstelling promotie commissie:

Rector Magnificus, voorzitter

Prof. dr. ir. R.H.J.M. Otten,

Dr. ir. N.P. van der Meijs,

Technische Universiteit Delft, promotor

Technische Universiteit Delft, toegevoegd

promotor

Prof. dr. C.I.M. Beenakker, Technische Universiteit Delft

Prof. dr. J.R. Long, Technische Universiteit Delft

Prof. dr. ir. P.R. Groeneveld, Technische Universiteit Eindhoven

Prof. dr. ir. D. Stroobandt, Ghent University Dr. K. Goossens, Philips Research

Proefschrift. - ISBN 90-809648-3-2

Copyright ©2005 by Giuseppe Garcea.

All rights reserved. No parts of this book may be reproduced in any form or by any electronic or mechanical means (including phothocopying, recording, or information storage or retrieval) without prior permission in writing from the author.

Front cover: René Magritte La reproduction interdite 1937, Museum

Boijmans van Beuningen, Rotterdam.

Back cover: Darlisa Riggs, Balance, 2002.

Bambino, se trovi l'aquilone della tua fantasia legalo con l'intelligenza del cuore.

Vedrai sorgere giardini incantati e tua madre diventerà una pianta che ti coprirà con le sue foglie.

Fa delle tue mani due bianche colombe che portino la pace ovunque e l'ordine delle cose.

Ma prima di imparare a scrivere guardati nell'acqua del sentimento.

Alda Merini

Child, if you find the kite of your fantasy bind it to the intelligence of your heart. You will see the rising of bewitched gardens and your mother will become a plant that will cover you with its leaves. Make of your hands two white doves that could carry everywhere the peace and the order of the things. But before learning to write look at yourself in the water of the feelings.

Alda Merini

Ai miei genitori Giuliano e Maria

# **Contents**

| 1 | Intr | oduction                                        | 1 |

|---|------|-------------------------------------------------|---|

|   | 1.1  | Performance characteristics                     | 2 |

|   | 1.2  | Scenarios for high-level design                 | 4 |

|   | 1.3  |                                                 | 5 |

|   | 1.4  |                                                 | 8 |

|   | 1.5  | This thesis                                     | 0 |

| 2 | Dela | ny modelling of IC interconnect                 | 3 |

|   | 2.1  | Interconnect parameters                         | 4 |

|   | 2.2  | Elmore time constants                           | 6 |

|   | 2.3  | Lumped and distributed RC configurations        | 0 |

|   | 2.4  | Modelling in-line buffers                       | 1 |

| 3 | Uni  | Form buffer planning 23                         | 3 |

|   | 3.1  | Optimal unconstrained repeater insertion        | 4 |

|   | 3.2  | Calibrating the in-line buffer delay model      | 6 |

|   | 3.3  | Area-delay trade-off                            | 7 |

|   | 3.4  | Area-power-delay trade-offs                     | 5 |

|   | 3.5  | Discussion                                      | 2 |

| 4 | Non  | -uniform buffering 4!                           | 5 |

|   | 4.1  | Sizing in-line buffers                          | 5 |

|   | 4.2  | Sizing in-line buffers under area constraints 5 | 1 |

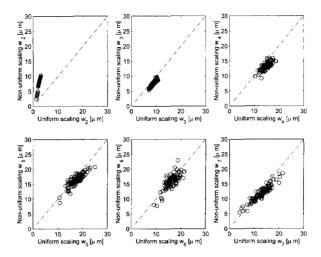

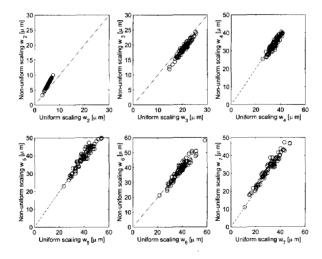

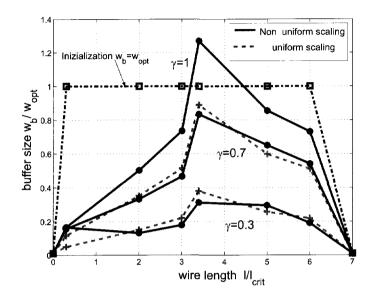

|   | 4.3  | Results                                         | 5 |

|   | 4.4  | Summary                                         | 9 |

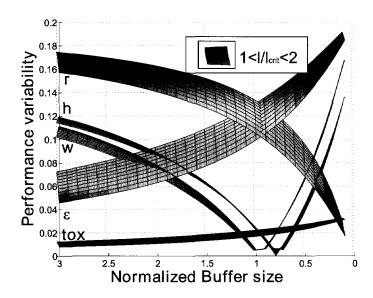

| 5 | Imp  | act of process variations 63                    | 1 |

|   | 5.1  |                                                 | 4 |

|   | 5.2  | Modelling performance variability 67            | 7 |

|   | 5.3  | Impact of interconnect variability 68           | 3 |

| ii | CONTENTS |

|----|----------|

|    |          |

|    | 5.4<br>5.5 | Impact of device variability                            | 74<br>76 |

|----|------------|---------------------------------------------------------|----------|

|    |            | Conclusions                                             | 78       |

| 6  |            | ust buffer planning                                     | 81       |

|    | 6.1        | Enhancing robustness                                    | 83       |

|    | 6.2        | The parameter variation space                           | 84       |

|    | 6.3        | The process variation space                             | 94       |

|    | 6.4        | Yield-centric buffering                                 | 97       |

|    | 6.5        | Conclusions                                             | 104      |

| 7  |            | lication: Network on chip                               | 105      |

|    | 7.1        | Preliminaries                                           | 108      |

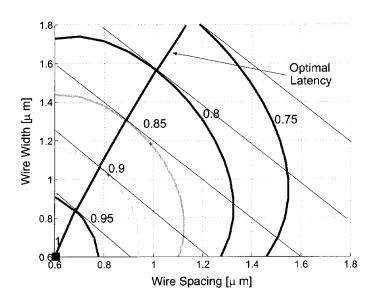

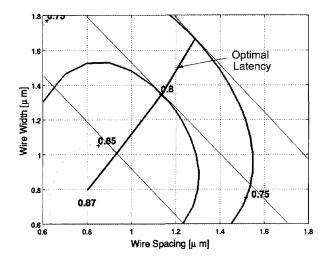

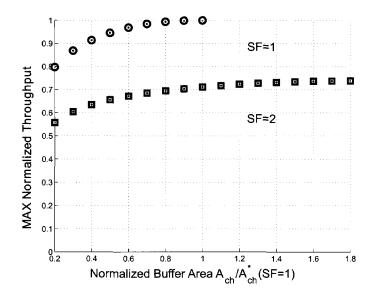

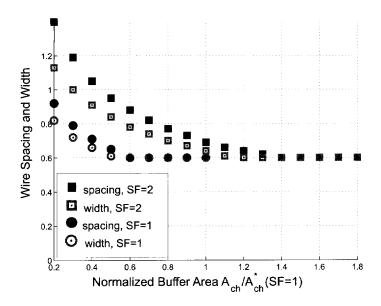

|    | 7.2        | Throughput driven buffer insertion                      | 112      |

|    | 7.3        | Unbuffered and unconstrained bus design                 | 113      |

|    | 7.4        | Constrained bus design                                  | 115      |

|    | 7.5        | Throughput under process variations                     | 122      |

|    | 7.6        | Summary                                                 | 125      |

| 8  | Tool       | s                                                       | 127      |

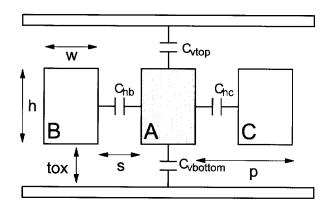

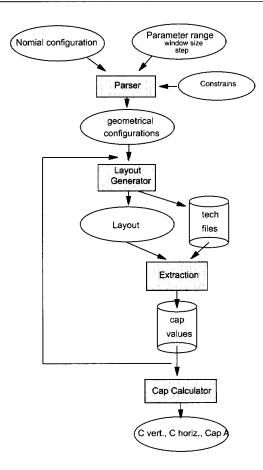

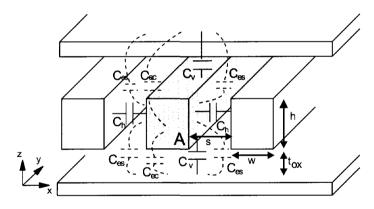

|    | 8.1        | CAIGE: CApacitance from Interconnect Geometry Extractor | 127      |

|    | 8.2        | WARP: Wire And Repeater Planning                        | 132      |

| 9  | Cone       | clusions                                                | 135      |

| A  | Spic       | e technology file                                       | 139      |

| В  | Sens       | sitivity parameters                                     | 143      |

| Ac | know       | rledgements                                             | 153      |

| Su | mma        | ry                                                      | 155      |

| Sa | menv       | ratting                                                 | 157      |

| Cu | rricu      | lum Vitae                                               | 159      |

# Chapter 1

# Introduction

#### **Contents**

| 1.1 | Performance characteristics     | 2  |

|-----|---------------------------------|----|

| 1.2 | Scenarios for high-level design | 4  |

| 1.3 | Global wires                    | 5  |

| 1.4 | Buffer planning                 | 8  |

| 1.5 | This thesis                     | 10 |

Many dissertations about digital microelectronics are introduced by a sentence like "the increasing demand for ...", when referring to complexity, speed, functionality, portability, etc., and support the statement by referring to the extraordinary evolution of the semiconductor industry in the last forty years. For already in 1963 Gordon Moore predicted that integration density on silicon was going to quadruple every four years, and until now the semiconductor industry has succeeded in fulfilling that prophesy, in spite of numerous discussions about when the evolution will deviate from this trend.

The very success of this industry is at the same time its burden: from a prediction Moore's law is, for decennia already, a goal setter, and reaching these goals nowadays is only possible with huge investments in production equipment, tight control of variability, and sophisticated design tools, while the market leaves only a narrow time window to compensate for these costs. This tremendous pressure can be illustrated by considering a product such as the Wi-Fi 802.11. Its market grew at an extreme pace, with many companies fighting for a share, but margins came down sooner than expected, making it very difficult to make a profit.

An average chip design in a 130nm process costs about ten million dollars, just to get the first chip out. A mask set for such a design could be 10% of that amount. It may have tens of millions of transistors. For 90nm processes this may be a tenfold, with costs roughly doubled. These are staggering numbers! But can it be used? Can design methodology cope with those complexities? The gap between what is really manufacturable in silicon and our design capability is growing.

#### 1.1 Performance characteristics

Performance has gotten a broader meaning: no longer is speed the only metric that counts. More an more products have demand for low power consumption and reliability. It is therefore of paramount importance in selecting a design point or identifying optimization problems, to understand that any decision is at best a compromise. The so-called "design for ..." approaches are pretty useless when they do not consider other characteristics. Making a circuit as small as possible, makes it often too slow, while optimizing speed may lead to unacceptable levels of power consumption. Modern IC-design is dominated by trade-offs, even when considering just a subproblem in the trajectory.

The smaller feature sizes will require new models to account for the new complex and no longer negligible physical effects. The growing design complexity as well as the complexity to have a reasonable representation of the physical implementation, requires the selection of the right level of abstraction and then making the right decision at that level. The lack of new physical models on one hand as well as the necessity to have right decisions at higher level of abstraction, open really challenging question on how to have a converging flow ready beyond 65nm. In this context predictions tools become of utmost importance. The common denominator is to build a bridge between technologists and designers by incorporating in the system level prediction tools, also for the relevant physical effects. The decisions made on the basis of predicted metrics will then improve the correspondence with the real implementation.

A serious shortcoming of today's tools used for analysis and design is that everything is considered "deterministic", meaning that they are based on fixed models for devices and wires and do not consider statistical variations in the underlying silicon. Current methodologies can predict best-case, worst-case and nominal parameters sets, but there is a lack of stochastic computing strategies which can model the probabilistic nature of

the variations.

We are on the verge of the era of probabilistic design [63, 30, 11]. Performance for example with this statistical approach will be not fixed to the nominal, best or worst case, but will be a statistical distribution. Engineers in optimizing their designs will ask not only whether the circuit has improved its performance, but also which percentage of its realizations presents a performance improvement. Performance estimations then will be more and more similar to the concept of acceptance already presented in the yield estimation.

Of course there is reluctance, both in EDA companies and with designers, to diverge from established design methodologies, but the investigation of trade-offs is gaining interest and statistical techniques are slowly getting accepted to significantly reduce the number of iterations in design flows. Vendors and academics predict that statistic timing analysis will hit the market in 2005 in order to address technologies of 65nm and below. That will require a lot of rethinking of the tools (extractions tools, technology files, libraries, place and route tools).

This thesis intends to represent a connection point between the new approach coming in the next years and the traditional "deterministic" approach. We propose an approach that uses traditional static performance prediction models and it estimates also its fluctuations due to random process parameters variations.

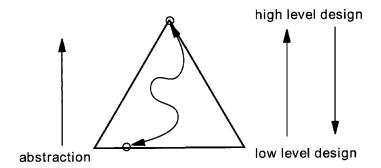

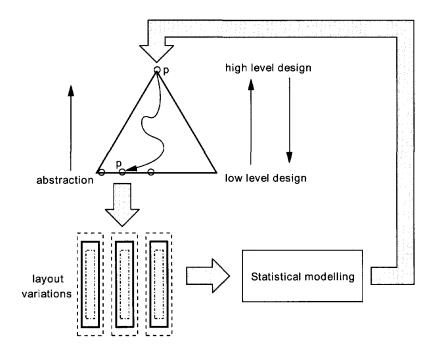

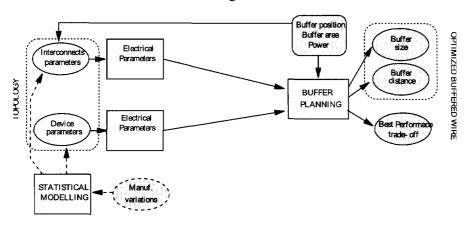

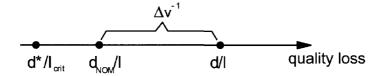

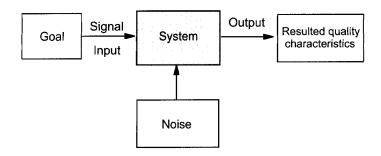

**Figure 1.1.** Traditional deterministic representation for the high level design abstraction

## 1.2 Scenarios for high-level design

The complexity of nowadays designs asks for a structured design flow with appropriate levels of abstraction for each step of that flow, such that the right decision and optimization can take place at that level assuring the final design convergence. Figure 1.1 illustrates that decisions taken at high levels using partial information about a system, can lead to several implementations at the low level showing more details. Any of the implementations at the low level on the bottom of the triangle could be reached by taking certain decisions at the various levels, thus exhibiting a specific path coming from a unique decision point taken at highest level represented by the top of the triangle. This traditional way to illustrate the importance of abstraction, perfectly valid in a deterministic framework, is now and for the future technologies much too simplistic.

Technology limitations used to get translated in *design rules* and following these rules enabled designers to make a design safe enough. As technology pushed further towards the physical limits the rules became stricter, constraining designers more and more, to the point where they can no longer comply without ending up with inadequate design, also where technology does support a solution.

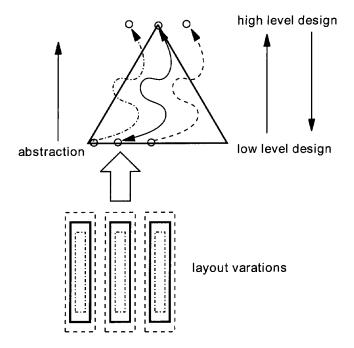

Figure 1.2 illustrates the fact that process variations are going to affect the outcome of the design decisions. Indeed process variations will affect the design point chosen at low level design, and if we reconstruct the design path deterministically as in figure 1.1 we see that variability causes unpredictability at high level design.

The result is that decisions at high level design tend to be too conservative under a worst-case variability scenario, or too optimistic when no variations are considered. Moreover, because of the nature of random process parameter variations the same procedures and abstractions that make the decisions in a flow may result in different implementations. The intrinsic uncertainty introduced by process variations, makes that there is no longer a single path connecting high level decision points to real design implementation.

Therefore it is necessary to rethink high-level decision methods to account for process variations in a statistical way. Figure 1.3 shows that a probabilistic term p should be associated with each decision indicating how many systems can be really implemented on silicon with certain specifications. This probability propagates from high to lower level design through different step of decisions, and ultimately represents a figure of yield relative to a certain specification, also denoted as  $parametric\ yield$ . Adequate

Figure 1.2. Impact of process variations on high level design

statistical modelling of the process parameters, translates the process variability in terms of parametric yield.

#### 1.3 Global wires

Global wires are seen as a key potential bottleneck for achieving high performance in integrated circuits. Of course their cross-sectional dimensions scaled with feature size, shrinking the metal pitches to maintain sufficient routing density. But with a more or less unchanged die size, relatively longer wires start to appear. The delay of these wires is becoming multiples of gate delay, and it is not even possible to cross the chip within the clock periods of today's processors

The development in the dimensions of these wires also decreases the predictability. The high aspect ratio height to width and the decreased spacing make the coupling capacitance between neighboring wires dominant in the total wire capacitance. It is difficult to predict in early stages because neighbors are not known than, and wires may run next to each other over long distances. Real behavior, that is switching activity on wires,

6 1.3 Global wires

**Figure 1.3**. Statistical modelling to account for process variations at high level of design abstraction

increases this unpredictability even more. And since long wires will be buffered process variations affecting transistor properties also have an impact on long interconnect.

The performance degradation and growing uncertainty under process variations can be countered by technology improvements as well as by design solutions:

#### New materials:

• The use of copper wires significantly alleviates electro-migration, which was a significant problem for aluminum processing technologies. Being a lower resistivity material, copper was also expected to reduce the total resistance of the conductors when compared to an equivalent aluminum wire. However, due in part to the roughness induced scattering effects, caused by the intrinsic island-type morphology of the copper-films, its resistivity increases with thickness reduction. Thinner copper-films turn out to have very high resistivity (it is estimated that for a 40nm

the resistivity value is twice the value obtained for broad lines  $(2.2\mu\Omega cm)$  [19]). This poses two problems: one is technology problem on how to control surface roughness, and the other is on how to have reasonable predictive models that account for this critical effect.

- Another way to reduce signal delay is by reducing the electrical permittivity, that is the k-value of the intermetal dielectric. The problem here is that low-k materials are really bad heat conductors and this implies complications in reliability.

- There are projects that already are investigating the possibility to have air gaps between the metal lines [19].

#### Design solutions:

- Buffer insertion can reduce delay by dividing a wire into smaller segments, making interconnect delay linear instead of quadratic in terms of the wire lengths. Optimal segmentation and sizing of buffers in point-to-point has been presented in [7, 21, 3, 15, 49], while buffer insertion in tree structures is subject of [62].

- Wire tapering, despite some theoretical benefits [24], remains problematic when it comes to integration into coherent a routing methodology and in generally it is not applied [4].

- Shielding of signal wires enhances predictability. Layout methodologies as the one proposed in [33] in which each signal has a constant effective capacitance achieved by alternating signal wires with power and ground on higher metal layers, are very effective. It frees up the resources usually taken by supply lines, but it probably will not fully compensate the decrease in wiring density.

#### Unconventional interconnect:

3D integration, that is the use of multiple active layers, for a lot of people seems to alleviate the delay problem [55, 52], without affecting the transistor packing and the chip area. This approach opens new degrees of freedom in system design, placement and routing. There are different techniques to use the different active layers. Several proposals for appropriate technologies were published (the processed wafer bonding [23], silicon epitaxial growth [44] and solid phase crystallization [35]), but film transfer [57] is the most promising. The main concerns are problems with heat dissipation and possibly an increase of coupling effects.

- Active top layers, a special case of 3D integration, were already proposed in [46] where it was stated that the essential interconnect complexity could not be curbed by adding more and more wiring layers. A top layer with optical receivers was suggested so that the clock can be flashed on the chip, reducing it claims on the wiring resource and solving skew problems. Later [48] the author added that the layer can also house the in-line buffers in long interconnect, avoiding via's through all layers to reach buffers in the bulk and the opportunity to reduce the critical delay.

- Photonic interconnects which will substitute polymers to the silicon for global wires. For the heterogeneous integration, wafer bonding will be used [45].

## 1.4 Buffer planning

With interconnect becoming a dominant factor in the total circuit performance, interconnect-centered synthesis techniques for performance optimization such as appropriate topology construction of the layer stack, buffer sizing, buffer insertion, wire and spacing sizing must be investigated. It has been estimated in [18] that appropriate buffer insertion and sizing and wire sizing can reduce the global interconnect delay (of a line of 2cm) by a factor of five to six when compared to the use of nominal wire width without buffers in  $0.07\mu m$  technology generation from [6].

Not surprisingly buffer planning got a lot of attention lately. We distinguish two main buffer strategies:

#### • Uniform buffer insertion

Uniform buffer insertion reduces the quadratic increase with length observed in unbuffered wires, to linear if the ensuing segmentation is optimal. The optimum depends on the wire geometry, and is therefore layer dependent. It does not (or almost not) depend on the buffer properties.

If we assume also that the buffers distributed along an optimally segmented wire are of equal size, then each wire segment between two of those buffers produces the same delay. Buffer planning is completely characterized by the number of buffers (or equivalently the buffer distance) and their size. That is, the result is independent of the length of the interconnect and one can focus on a single segment.

#### • Buffer block planning

Because of the smaller feature sizes and therefore a relatively larger chip area, the number of nets that need buffering for high performance design will increase for future technology generations. The number of these buffers on a single chip in 50nm technology is estimated to be 800.000 according to [17]. These buffers require silicon area and power-ground connections, and may not be placed arbitrarily inside and between existing modules.

Buffer block insertion during the floorplanning was proposed in [17]. Buffer blocks are constructed by using *feasible regions*. These are the biggest polygons in which buffers can be inserted satisfying the timing constraints for a specific net. One of the consequences of this approach is that the optima achievable with unconstrained buffer planning are out of reach.

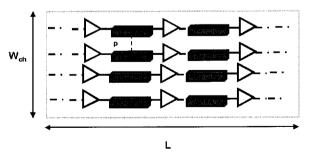

This thesis aims at developing a decision making procedure for effective buffer planning in interconnect. The use of these procedures is useful for design engineers/methodologists of high-performance microprocessors and application specific integrated circuits. In particular we will address problems of multi-objective optimization in buffering for a point-to-point wires assuming that the wire geometry is given. At the end we will extend our results to typical unidirectional multiwires structures used in *Network-on-Chip* (NoC) applications.

The nature of the trade-offs we are going to study are: performance versus buffer area, performance versus power, uniform performance versus non uniform buffering in an unconstrained as well as in an area-constrained situation. Those kind of trade-offs assume that there are no process variations. However, process variations do influence the performance prediction and they invalidate the traditional solution for buffering in a deterministic case. This is due to the fact that performance value is not anymore deterministically found, but performance has fluctuations. This implies that the choice of optimal buffering has to account somehow for this performance uncertainty. Our contribution in this field it is to propose a buffering which enhances performance robustness.

1.5 This thesis

It is important to stress that the solutions for these optimization problems are based on analytical models. Whenever possible closed-form expression for optimal buffer size and distance will be derived. Other solutions will be found by including analytical formulations in simple iterative schemes.

#### 1.5 This thesis

The main contributions of this thesis are:

Analysis We propose an analytical model based on elmore approximation and calibrated by using spice simulations. The most important performance metric will be the signal propagation velocity. Impact of process variations on this performance metric will be estimated analytically. We will characterize the statistical behavior of the performance in terms of its expected value and in terms of its standard deviation.

Synthesis We derive buffer strategies in presence of area and power constraints and we show that the solution gives the best performance under those constraints. From this approach complete trade-offs between performance, area and power can be composed. Restrictions on buffer locations will require a resizing of each of the buffers. A complete algorithm for that, which works also for limited buffer area, is described. We propose two techniques for buffer planning in the presence of process variations. The first one is an analytical approach which solves the optimization problem for each of the samples in the variability space. The other one uses the statistical characterization of the performance to derive a yield-centric buffering.

**NoC** We present how to trade uniform buffering with wire density for maximum throughput of a channel of fixed width.

The organization of this thesis is as follows.

First we establish the important parameters of ic interconnect and derive suitable models for wire segments between buffers in chapter 2. In chapter 3 we summarize the well-known fundamental results using that delay model for the traditional analytical solution for unconstrained buffer insertion. We will explain how to calibrate the model aided by spice simulations. We define a performance metric and present analytical methods

for performance-versus-buffer area and performance-versus-power tradeoffs. Moreover we compare the results for area-constrained problem with the power-constrained problem. Power and area constraint problems result in the same buffering provided that the short circuit power term can be neglected. Buffer planning under constrained allocation and the corresponding buffer resizing techniques are the subjects of chapter 4. Also resizing under area limitations is solved.

The chapters that follow discuss the impact of process variations on the performance. In chapter 5 an analytical method to predict performance variability is illustrated. In chapter 6, we propose buffering to enhance performance robustness and a parametric yield-centric buffering method is derived. We will show that optimal buffer planning in the deterministic case is not necessarily optimal in the presence of process variations. Starting from this consideration we maximize yield and we draw a complete trade-off between yield, buffer area and signal speed.

In chapter 7, we extend the results from the preceding chapters to unidirectional bus design, typically used for NoC applications. We show how to find the best wire density and buffering for maximum throughput of buses of fixed width. We also pay attention to parametric yield under process variations.

Chapter 8 illustrates two tools that where developed in this project. In particular, we present a tool for extracting accurate values for wire capacitance per unit length. A complete interactive demo suite which is webbased, has been written and its structure will be briefly explained.

# Chapter 2

# Delay modelling of IC interconnect

#### Contents

| 2.1 | Interconnect parameters                  | 14        |

|-----|------------------------------------------|-----------|

|     |                                          | 1.0       |

| 2.2 | Elmore time constants                    | 16        |

|     | T 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1  | 20        |

| 2.3 | Lumped and distributed RC configurations | 20        |

| 0.4 | No. 4-11: in 1: backers                  | 91        |

| 2.4 | Modelling in-line buffers                | <b>41</b> |

Interconnections are relatively small compared to the longitudinal "length". Several such traces may form topologically different structures, but for signal propagation they are almost exclusively trees. Some of these structures consist of a single trace and we will call them point-topoint connections.

It is safe to assume that the isolation is perfect, that is, there is no unintended conduction from the structures formed by these traces to other such structures or other conducting media. And also the intended return currents are typically not in the substrate. Ergo, a loss conductance will be insignificant, and on-chip interconnect can be characterized as a so-called RLC line with an in-line resistance r, a shunt capacitance c and an inline inductance c all per unit length, until the cross-sectional dimensions become noticeable.

In this chapter we are interested in the delay, and preferably in such a form that we can account for it in the early stages of design. Repeated simulations for all affected interconnect with models full of non-lumped elements is out of the question. In section 2.1 we explore what models might be valid for IC interconnect. The important parameters are length and signal speed. Once the pertinent region is identified, we try to get simple closed-form expressions that are accurate enough to predict the delay to be expected, knowing that detailed layout information is not available. They should support early design decisions, based on optimizing aspects of interconnect.

Depending on whether r is relatively small or large, the propagation behavior will (approximately) be governed by the telegrapher's equations or the diffusion equation. The first case will give rise to a constant velocity of propagation, which we will denote as  $v_{TEM}$  since we will approximate this value by that of a (quasi-)TEM line (a line with a transverse electromagnetic field, essentially a 2-dimensional transmission line). The second case will give rise to an RC mode of propagation, with a quadratic dependence of propagation time on distance such that we cannot strictly speak about velocity.

After settling that question in section 2.1 we want to come to approximations of line delay, with and without buffer insertion, a topic we explore further in chapters 3 and 4. The basis of the discussion is the well-known delay formula from [22] and the derivations from [7, 49]. The analysis here is deterministic, that is without taking statistical variations into account. The latter will be taken up in chapter 5 and 6.

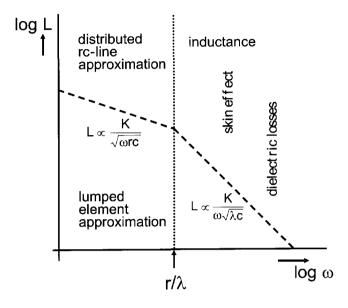

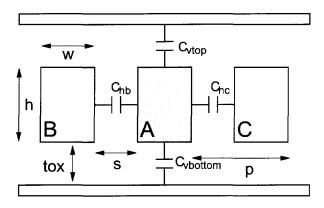

## 2.1 Interconnect parameters

Only when traces are "short" connections can be seen as equipotential areas, or nodes in a lumped network. And what "short" is, depends on how fast the transients are. Depending on length-speed combinations different approximations allow simplifications of the analysis. In figure 2.1 regions for approximations are indicated. For slow transients only the dc-resistance and the capacitance matter. Signal components with radial frequency less than  $r/\lambda$ , where r is the resistance per unit length and  $\lambda$  is the inductance per unit length, are not significantly affected by the inductance. At higher frequencies the inductive reactance becomes noticeable, and when the internal inductance of the conductors becomes comparable to the dc-resistance, a redistribution of current within the conductors takes place and we enter a region with skin effect. Modelling interconnect as a linear circuit then becomes more difficult. The behavior becomes more intricate

with increasing frequencies, and when the corresponding wavelength gets close to cross-sectional dimensions of the line waveguide techniques have to be applied to analyze behavior. One of the effects for speed of operation in that region is the dispersion of the rising and falling edges.

Figure 2.1. Approximation regions (after [31])

The value of  $\lambda$  can be estimated from transmission line theory, using the model for the so-called TEM regime. The velocity of propagation along a TEM line is given by  $v_{TEM} = \sqrt{1/\mu\epsilon} = c_0/\sqrt{\epsilon_r}$  with  $\mu$  the permeability of the medium (which in our case is equal to  $\mu_0$ , the permeability of vacuum),  $\epsilon$  the permittivity of the medium,  $c_0$  the speed of light in vacuum and  $\epsilon_r$  the relative permittivity of the medium. For the case of SiO<sub>2</sub> with  $\epsilon_r = 3.9$  as the dielectric medium, we arrive at  $v_{TEM} \approx 1.5c_0 = 1.5 \cdot 10^8 m/s$ . For a TEM line we also have  $\lambda c = \mu \epsilon = 1/v_{TEM}$  leading to  $r/\lambda = rcv_{TEM}^2$ . In the sequel of this thesis, we will present actual values of r and c for realistic technologies. Typically, they are around  $c = 25fF/\mu m$  and  $r = 25m\Omega/\mu m$ . Using these values, we arrive at  $r/\lambda = 14 \cdot 10^{12} rad/s \approx 2THz$ .

This means that only very fast components in the signal will be affected. For digital applications, and delay analysis in particular, these components are of no interest. Although much of the analysis are done under the assumption of square waveforms and step responses (and therefore with fast signal components present), such waveforms cannot be maintained in today's digital circuitry, and concern is rather in passing given voltage levels

than in the exact waveform (i.e. distortion is not a real concern).

This analysis suggests that it is justified to model interconnects as RC lines rather then LC(R) lines, which subsequently will lead us to the conclusion of a delay growing with the square of the length of the interconnect (see also equation 2.4). This quadratic dependence is traditionally subdued by segmentation of the line, by inserting buffers. Therefore, apart from the interconnect line itself, we also need to consider the driver and receiver models and their effect on the propagation delay. Without developing suitable models here, we note that the delay can only increase. In particular, the TEM velocity will form an upper bound for the actual effective velocity. Furthermore, we will in the sequel of this thesis develop accurate models for the RC mode of propagation including driver and receiver. Hence, if the effective RC propagation velocity including driver and receiver is small compared to the LC (TEM) propagation velocity, the RC mode of propagation prevails and our conclusion still stands.

Thus, as long as the effective velocities that we can achieve using our modeling and optimization procedures are small compared to  $v_{TEM}$  as derived above,  $1.5c_0=1.5\cdot 10^8 m/s$ , our models are justified. This will be the case for all our results, as can readily be concluded in what follows. The results in section 3.2 and table 3.1 in particular, confirm this as the velocity turns out to be around  $0.35\cdot 10^8 m/s$  for all considered process nodes.

It must be noted, however, that the above analysis does not imply that inductive effects cannot occur for on-chip interconnect systems. These can occur if the total series resistance would be small enough. This will happen with very wide wires and very large drivers, in regions of the design space that are not considered in this thesis.

#### 2.2 Elmore time constants

Delay is mostly analyzed by studying the response at an output to a steplike stimulus at the input. Unfortunately, even after simplifying interconnect to an RC line, there is no analytic solution, except for some special cases, not of interest for delay characterization on complex chips. However, useful approximations can be derived.

If an interconnect line can be modelled as resistance the delay can be measured by the time constant  $\tau$  of the RC low-pass filter consisting of the line resistance and the capacitive load at the destination. There are several ways of defining this constant, but convenient for the derivations that follows is to set  $\tau$  equal to the time it takes to let a non-zero voltage

over the capacitor drop by a factor e (e is the natural number: 2.718...) when the source end is grounded. We denote time constants thus defined by  $\tau_E$ . It is easy to verify that for the RC low-pass filter  $\tau_E = RC$ , and therefore equal to usual time constant for that circuit.

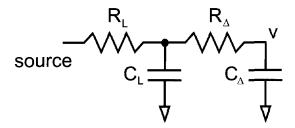

The question we want to answer is what RC low-pass filter has the same  $\tau_E$  as an interconnect line that cannot be modelled by a single RC section, but at best as an RC chain, if not as an inhomogeneously distributed resistance and capacitance. For short lines terminated by a capacitance considerably larger than the total line capacitance this is possible by simply taking the total resistance and total capacitance. That is how delay was modelled for complex chips even for the larger part of the nineties. Let us assume that it is possible for any line of length up to L by some resistance  $R_L$  and some capacitance  $C_L$  and determine the time constant  $\tau_E$  for a line of length  $L+\Delta$  where  $\Delta$  is short and has total resistance  $R_\Delta$  and total capacitance  $C_\Delta$ .

**Figure 2.2.** Model of a line of length  $L+\Delta$ .

With the line of length L modelled as a section with  $R_L$  and  $C_L$ , and the additional piece as a section with  $R_{\Delta}$  and  $C_{\Delta}$  an RC chain of two sections is obtained (figure 2.2). The voltage v over  $C_{\Delta}$  has to obey

$$\frac{d^2v}{dt^2} + \frac{R_LC_L + R_LC_\Delta + R_\Delta C_\Delta}{R_LC_LR_\Delta C_\Delta} \frac{dv}{dt} + \frac{v}{R_LC_LR_\Delta C_\Delta} = 0$$

with solution

$$v = Ae^{-\alpha t} + Be^{-\beta t}$$

if

$$\alpha + \beta = \frac{R_L C_L + R_L C_\Delta + R_\Delta C_\Delta}{R_L C_L R_\Delta C_\Delta} \qquad \alpha \beta = \frac{1}{R_L C_L R_\Delta C_\Delta}.$$

A+B is the voltage at t=0, the time when we ground the source end. Further, because the derivative of v with respect to time has to be 0 we also

or

have the initial condition  $A\alpha + B\beta = 0$ . This yields

$$v(t) = (A + B) \left( \frac{\beta}{\beta - \alpha} e^{-\alpha t} - \frac{\alpha}{\beta - \alpha} e^{-\beta t} \right)$$

and shows that  $\tau_E$  has to satisfy by definition

$$\frac{\beta}{\beta - \alpha} e^{-\alpha \tau_E} - \frac{\alpha}{\beta - \alpha} e^{-\beta \tau_E} = e^{-1}.$$

(2.1)

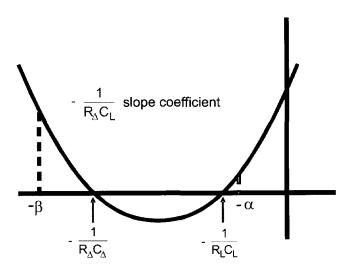

$\alpha$  and  $\beta$  are the solutions of the characteristic equation

$$p^2 + \frac{R_L C_L + R_L C_\Delta + R_\Delta C_\Delta}{R_L C_L R_\Delta C_\Delta} p + \frac{v}{R_L C_L R_\Delta C_\Delta} = 0$$

which can also be written as

$$p^{2} + \left(\frac{1}{R_{L}C_{L}} + \frac{1}{R_{\Delta}C_{\Delta}}\right)p + \frac{1}{R_{L}C_{L}}\frac{1}{R_{\Delta}C_{\Delta}} = -\frac{1}{R_{\Delta}C_{L}}p$$

$$\left(p + \frac{1}{R_{L}C_{L}}\right)\left(p + \frac{1}{R_{\Delta}C_{\Delta}}\right) = -\frac{1}{R_{\Delta}C_{L}}p.$$

Figure 2.3. Solutions of the characteristic equations.

A glance at figure 2.3 shows that, since  $R_L C_L \gg R_\Delta C_\Delta$ , we have  $\beta \gg \alpha$ . Going back to equation 2.1 we see that in that case

$$\frac{\beta}{\beta - \alpha} e^{-\alpha \tau_E} \approx e^{-1}$$

and from that follows

$$\alpha \tau_E \approx 1 - \ln\left(1 - \frac{\alpha}{\beta}\right) \approx 1 + \frac{\alpha}{\beta}.$$

Accuracy is better than 1%, even when  $R_L = R_{\Delta}$  and  $C_L = C_{\Delta}$ .

This is in essence the formula first derived, from a different insight, by W.C. Elmore in 1948 [22], because

$$au_E pprox rac{lpha + eta}{lpha eta} = (R_L + R_\Delta)C_\Delta + R_L C_L.$$

We therefore call  $\tau_E$  the *elmore time constant*. The usual interpretation is that the elmore time constant of an RC chain equals the sum of the time constants of single RC sections, obtained by combining every capacitance with the total resistance that separates it from the source. It has been demonstrated for two sections above, and the general result follows by induction. So, for an an RC chain with n sections, indexed from the source, we have

$$\tau_E = \sum_{i=1}^{n} \left[ C_i \sum_{j=1}^{i} R_j \right]$$

(2.2)

Elmore delay estimation applies to well-damped circuits composed of any number of series resistances and shunt capacitances. It does not apply (in its original form) to circuits involving inductance, resonance, overshoot, or any form of poorly damped or non-monotonic behavior.

When the input rise time significantly exceeds the response time of the circuit (that is,  $\tau_E$  is much less than the time the input takes to reach 90% of the swing), the output waveform tends to look like a strict delay of the input waveform and the elmore delay becomes exact. When the input rise time is shorter than  $\tau_E$ , the output waveform becomes distorted and the elmore delay serves as an estimate of delay.

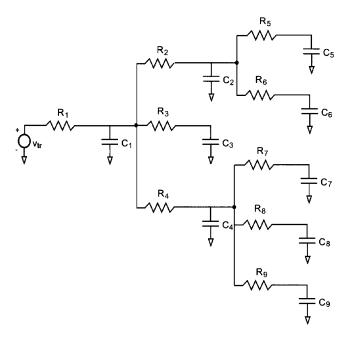

To apply the elmore delay concept to a tree-structured circuit, one must identify all the resistors  $R_i$  that lie along a path from the input to the output under analysis. Then, for each series resistor  $R_i$  one must identify the total downstream capacitance  $C_i$  charged by that resistance and sum all these  $R_iC_i$  time constants. The caption of figure 2.4 gives the the elmore estimate for the destination with index 9 in the schematic of that figure.

In practice, the elmore delay estimate may be successfully applied to well-damped RC networks, but not for lines having appreciable amounts of inductance or for non-monotonic inputs. In [28] an attempt is described to extend elmore delay estimation to account for line inductance.

**Figure 2.4.**  $\tau_{E,9} = R_1 \sum_{i=1}^9 C_i + R_4 \left( C_4 + \sum_{i=7}^9 C_i \right) + R_9 C_9.$

## 2.3 Lumped and distributed RC configurations

Cases where all sections are identical, except possibly the last one with capacitance  $C_d$ , are of special interest. In that case

$$\tau_E(n) = \frac{1}{2}n(n-1)RC + nRC_d.$$

(2.3)

If R = rL/n and C = cL/n are chosen, it models a homogeneous line, and taking the limit gives the famous result

$$\lim_{n \to \infty} \tau_E(n) = \frac{1}{2} rcL^2 + rLC_d, \tag{2.4}$$

showing that the delay of an homogeneous line increases quadratically with its length.

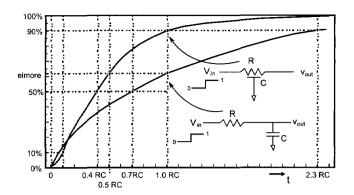

The elmore time constant was chosen to be the time for a step response to complete the  $1-e^{-1}$  part of the swing, that is about 63%. That is not always convenient, especially if we want to cascade interconnection structures. Figure 2.5 compares the step responses of an RC low-pass filter and a homogeneously distributed line of the same total resistance and capacitance. It also marks the points where 50%, 63.2% and 90% of the swing

**Figure 2.5**. Step responses of an RC section and a distributed line after [7].

is completed. Obviously, 63.2% is reached after 1.0RC for the section and after 0.5RC for the distributed line. It is the elmore time constant for these configurations. The 50% marks are at t=0.69RC and t=0.38RC respectively, while 90% requires 2.3RC and 1.0RC respectively. In general we will use aRC for distributed lines and bRC for lumped RC section, and calibrate the values for the situation at hand as for example in section 3.2.

## 2.4 Modelling in-line buffers

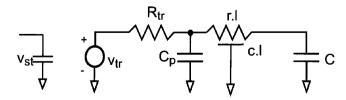

Elmore time constants are also useful for obtaining computationally convenient models for in-line buffers (or repeaters), as Sakurai showed in [53]. His buffer model is a simple inverter driving a line of length l, terminated with C. Although different delay models have been proposed in the literature, this one still seems the one which can guarantee a good trade-off between accuracy and simplicity. Figure 2.6 shows the model for a single segment.

Figure 2.6. Generic restoring buffer model

The repeater driving the line is represented as a voltage source controlled by the voltage  $v_{st}$  at the input capacitance. This voltage source switches instantaneously when the fraction denoted by x,  $0 \le x \le 1$  of the total swing has been reached. The switching at the voltage source is a perfect step.  $R_{tr}$  defines the equivalent transistor resistance which represents the sum of the channel resistance, the via resistances, and the source and drain resistance, which all scale inversely proportional with the transistor size. C is the capacitance at the end of the line, collecting the input capacitances of gates connected there.  $C_p$  stands for the drain capacitances in case of a CMOS-inverter. It scales with the size of the repeater.

Using the elmore formula (equation 2.2) yields the delay:

$$\tau = b(x)R_{tr}(C + C_p) + b(x)(R_{tr}c + rC) * l + a(x) * rcl^2$$

(2.5)

where a and b now also depend on the switching model being employed. Thus, this RC representation offers simple closed-form approximation for the delay of the circuit very useful in optimization problems of chapters 3 and 4. For another benefit provided by this kind of approximation is interconnect delay can be easily incorporated. The simplest metric of performance evaluation for IC interconnect is when interconnects are modelled in terms of RC circuits. A complete RC network will be then sufficient to describe repeater and line delay in combination.

# Chapter 3

# Uniform buffer planning

#### Contents

| 3.1 | Optimal unconstrained repeater insertion   | 24 |

|-----|--------------------------------------------|----|

| 3.2 | Calibrating the in-line buffer delay model | 26 |

| 3.3 | Area-delay trade-off                       | 27 |

| 3.4 | Area-power-delay trade-offs                | 35 |

| 3.5 | Discussion                                 | 42 |

A WELL known technique to reduce the performance degradation for global wires consists in using repeaters inserted along their length. The segmentation of these wires due to those repeaters is done ideally by regenerating the signal once the delay along the wire approaches the gate delay. The general problem here is to obtain the type of buffers, their number, their size and their positions in the line such that the delay is minimized. The optimal segmentation as well as the optimal buffer size can be determined for a given technology and for a defined interconnect architecture. [7] and [49] present analytic, closed-form formulas for optimal buffering without constraints on the area needed for repeaters.

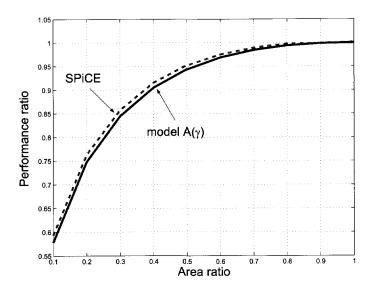

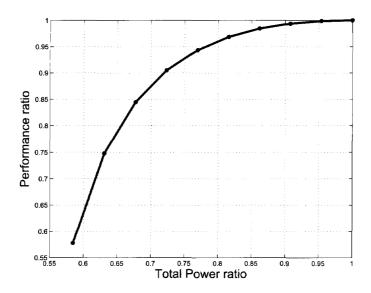

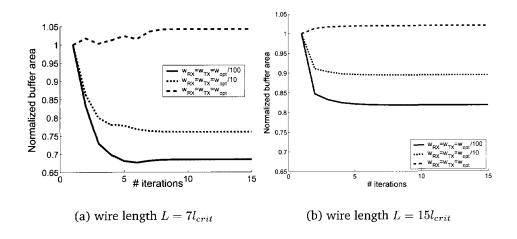

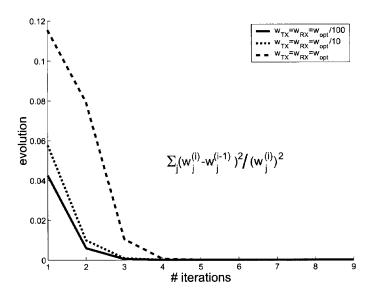

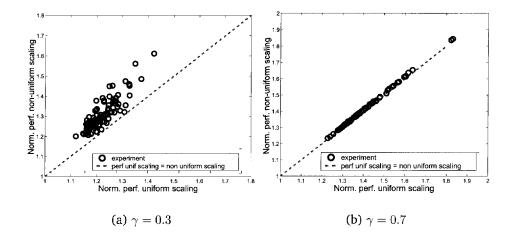

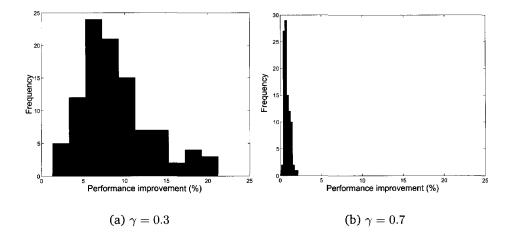

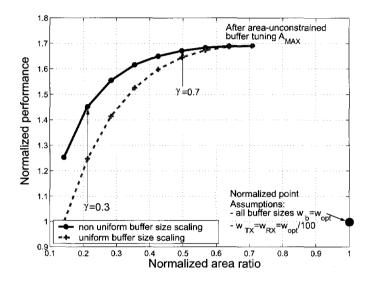

In this chapter we extend these results by constraining the buffer area and finding the best performance under constraint. These results enable us to draw the full trade-off curve for buffer area versus performance in global interconnects. Such curves show among other things that sacrificing 15% of the performance is paid off with a 70% reduction of area. The analytic results closely match spice simulation results.

The extension is relevant, because designers must always seek trade-offs between performance characteristics and because unconstrained buffering

might not be sustainable into the future. In [47] it has been shown that, accepting some assumptions for the rent exponent in statistical models for wire length distribution, unconstrained optimal buffering might require up to 80% of the total silicon area in imminent semiconductor technologies. Our current results show that this might be reduced significantly with only a slight performance degradation.

We will investigate in this chapter a deterministic uniform buffer planning, that is, we assume that there are no restrictions in placing the buffers, such that a perfect uniform distance between buffers is always possible. This provides a simplification to our problem, in part because it can become independent of the total length of the wire to be buffered.

This chapter has the following structure: after summarizing the results on unconstrained repeater insertion, we use them to devise a method for calibrating the parameters of the segment model of section 2.4. Section 3.3 is about reducing area at the cost of speed, while section 3.4 brings power into play, leading to a complete power-area-delay trade-off.

## 3.1 Optimal unconstrained repeater insertion

The repeaters, both driving and loading a segment, can be characterized by a linear output resistance  $R_{tr}$  (defined as the equivalent transistor resistance), input gate capacitance C and parasitic output capacitance  $C_p$ , mainly originating from the drain capacitance. The delay is given by:

$$\tau = b(x)R_{tr}(C + C_p) + b(x)(R_{tr}c + rC) * l + a(x) * rcl^2.$$

(3.1)

Defining the buffer size as  $w_b$ , its relation with the buffer parameters will be  $C = c_0 w_b$  and  $R_{tr} = r_0/w_b$  and  $C_p = c_p w_b$ . Moreover we will define a device dependent parameter  $\tau_0$  as  $\tau_0 = R_{tr}(C + C_p) = r_0(c_0 + c_p)$ .

If a wire of total length L is regularly segmented into n cells such that n = L/l, then the total delay along the wire will be:

$$T = n\tau = L\left(\frac{b\tau_0}{l} + b(\frac{r_0}{w_b}c + rc_0w_b) + a\tau_i l\right)$$

(3.2)

A remarkable property of equation (3.2) is that it only contains terms with either l (the segment length) or  $w_b$  (the buffer size). Therefore, the optimum segment length (obtained via differentiation to l) and buffer size (obtained via differentiation to  $w_b$ ) are independent! In particular, both

the l and  $w_b$  dependencies are of the form f(x) = A/x + Bx, with  $x_{min}$  equal to  $\sqrt{A/B}$ .

Thus, taking the derivative of equation (3.2) with respect to l and setting it to zero shows that the insertion of repeaters at a fixed optimal distance  $l = l_{crit}$  is found from the expression  $b\tau_0/l^2 = a * \tau_i$  and it will reduce the delay on wire length to a linear function. This optimal segment length will be

$$l_{crit} = \sqrt{\frac{\frac{b}{a}\tau_0}{\tau_i}} \tag{3.3}$$

The optimal buffer size  $w_b = w_{opt}$  can be obtained from taking the derivative of (3.2) with respect to  $w_b$  and setting it to zero:

$$w_{opt} = \sqrt{\frac{r_0}{c_0}} \sqrt{\frac{c}{r}} \tag{3.4}$$

Equations (3.3) and (3.4) clearly show that  $l_{crit}$  and  $w_{opt}$  are independent. An optimal segment will be defined as a segment with  $l=l_{crit}$  and  $w_b=w_{opt}$  and its delay  $\tau_{crit}$  will not be dependent on the geometry of the wire but only on the technology parameters. We will show in the next section a method to find these parameters. The value of  $\tau_{crit}$ , the delay of one segment of an optimally buffered line, can be expressed by:

$$\tau_{crit} = 2b\tau_0 \left( 1 + \sqrt{\frac{b}{a} \frac{r_0 c_0}{\tau_0}} \right) \tag{3.5}$$

and is a characteristic for a given technology.

The delay of an optimal segmented line of length  ${\cal L}$  with optimal buffer size will then be

$$T = \frac{L}{l_{crit}} \tau_{crit} = L \tau_{crit} \sqrt{\frac{a}{b} \frac{\tau_i}{\tau_0}}$$

(3.6)

In the rest of this thesis, it will prove useful to work with the reciprocal velocity of signals along the line. Reciprocal velocity is more convenient than velocity because it is additive. From (3.2) we can derive

$$v^{-1} = \frac{T}{L} = \frac{\tau_0}{l} + a\tau_i l + \frac{br_0 c}{w_b} + brc_0 w_b$$

(3.7)

This reciprocal velocity is a good characteristic for the performance, and it is independent of the total line length L (and the delay along equidistantly buffered lines is linear in L). In particular we will in section 3.3 minimize  $v^{-1}$  under area constraints.

For completeness, we also give the unconstrained minimum reciprocal velocity  $v^{-1}$ , to be derived from (3.6):

$$v_{min}^{-1} = \frac{\tau_{crit}}{l_{crit}} = \tau_{crit} \sqrt{\frac{a}{b}} \frac{\tau_i}{\tau_0}$$

(3.8)

## 3.2 Calibrating the in-line buffer delay model

The delay of a single optimally buffered segment, given in (3.5) does not depend on the wire geometry, but exclusively on the technology parameters. Of course, if  $r_0$  includes also the via resistance, this independence is not completely true. However, it is shown in [49] that the effect of via resistance remains negligible. Another characteristic of the uniform line segmentation is that the optimal distance between buffers is independent of the buffer size. This implies that  $l_{crit}$  and  $w_{opt}$  can be found using two decoupled interactive simulations loops.

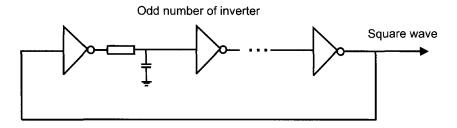

The circuit that we are simulating using hspice is a ring oscillator with an odd number of identical inverters connected by uniform wires. The wires are modelled with a certain number of lumped  $\pi$ -models. A ring oscillator, after a transient, has the property of oscillating with a certain a natural frequency. This frequency is a function of the number of buffers, but, more importantly, it is a function of the wire length and inverter size. The delay of a single segment  $\tau$  is related to the natural frequency of the ring oscillator  $1/T_{ring}$  by the relation  $\frac{T_{ring}}{2} = N\tau$ .

Our objective is to find the values of technology parameters by simulating a ring oscillator, and using reverse engineering to find  $r_0$  and  $c_0$ , which are properties of the process technology, through the analytical model presented in the previous section.

Figure 3.1. Ring oscillator with RC interconnect parasitics

First,  $l_{crit}$  is derived by changing the wire length of each of the segments in the ring oscillator and assuming that the buffer sizes are sufficiently large

so that the contribution of the gate delay is negligible when compared to the wire delay. The optimal value  $l_{crit}$  is found once  $\tau/l$  is minimum. Once  $l_{crit}$  is obtained, the optimal size of the inverters  $w_{opt}$  is found by simulating ring oscillators with inverters located at distance  $l_{crit}$ . Again the minimum  $v^{-1} = \tau/l$  gives the actual value of optimal inverter size  $w_{opt}$ . Finally for the value of  $l_{crit}$  and  $w_{opt}$  we can compute  $\tau_{crit}$  from simulations. The value of  $\tau_0 = \tau_{l=0}/b$  is retrieved by imposing length 0 on the wires between the inverters in the ring oscillator.

The inverter parameters  $r_0$  and  $c_0$  are found using the equations from the previous sections. The results can be summarized as follows:

$$r_0 = \sqrt{\frac{r}{c} \frac{\tau_0}{(1 + \alpha_p)}} * w_{opt}$$

(3.9)

and

$$c_0 = \sqrt{\frac{c}{r} \frac{\tau_0}{(1 + \alpha_p)}} * \frac{1}{w_{opt}}$$

(3.10)

where  $\alpha_p = c_p/c_0$ . It can be considered constant through technology scaling. The explicit expression for  $\alpha_p$  as function of the quantities derived from simulation is:

$$\alpha_p = \frac{1}{a\tau_0 \left(\frac{\tau_{crit}}{2b\tau_0} - 1\right)^2} - 1 \tag{3.11}$$

Table 3.1 summarizes for different technology nodes, the value of the device parameters used in elmore delay model calibrated with the spice simulations. Wire geometry values are taken from [1], wire capacitance values are obtained by using the analytical model presented in [65, 10] and the spice technology files used are available in [10].

Experimentally, it can be confirmed that  $w_{opt}$  is only a weak function of l and that  $l_{crit}$  is only a weak function of  $w_{opt}$ . This confirms the validity of the model represented by equation (3.7).

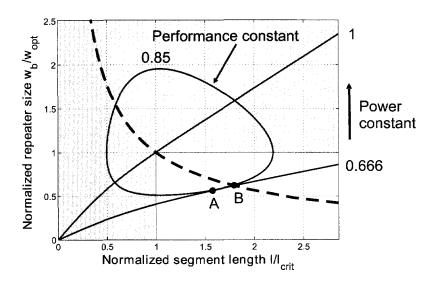

### 3.3 Area-delay trade-off

Area can be reduced by increasing the segment length l over  $l_{crit}$  and/or reducing the buffer size  $w_b$  to values smaller than  $w_{opt}$ , where  $l_{crit}$  and  $w_{opt}$  are defined in (3.3) and (3.4) respectively. It is indeed to be expected that some combination of both measures gives optimal results, where optimality

| Process (μ)                 | 0.18               | 0.13 | 0.10 | 0.07 |      |

|-----------------------------|--------------------|------|------|------|------|

| $V_{DD}$ (V)                | 1.8                | 1.5  | 1.2  | 0.9  |      |

| $L_{\mathrm{eff}}$ (nm)     |                    | 100  | 70   | 50   | 35   |

| $t_{ox}$ (Å)                |                    | 45   | 35   | 30   | 20   |

| $V_{TH}$ (V)                |                    | 0.37 | 0.27 | 0.22 | 0.16 |

| number of levels            |                    | 6    | 7    | 8    | 9    |

|                             | h (μ)              | 1.2  | 1.15 | 1.15 | 1.15 |

|                             | <b>w</b> (μ)       | 0.7  | 0.5  | 0.4  | 0.45 |

| Global wires parameters     | s (µ)              | 0.7  | 0.5  | 0.4  | 0.35 |

|                             | $t_{ox}$ ( $\mu$ ) | 1    | 0.7  | 0.6  | 0.5  |

|                             | $\rho$             | 2.2  | 2.2  | 2.2  | 2.2  |

|                             | $\kappa$           | 3.5  | 3.2  | 2.8  | 2.2  |

| $	au_0 \; (ps)$             |                    | 17.8 | 14.6 | 11.6 | 10.3 |

| $	au_{crit} \ (ps)$         |                    | 78.9 | 69.6 | 46.9 | 44.6 |

| $l_{crit}$ (mm)             | 2.9                | 2.2  | 1.5  | 1.7  |      |

| $w_{opt}(\mu)$              | 60                 | 50   | 40   | 40   |      |

| $r_o (k\Omega \cdot \mu m)$ | 2.9                | 2.6  | 1.94 | 1.8  |      |

| $c_o (fF/\mu m)$            | 8.09               | 7.84 | 7.45 | 7.1  |      |

| $\alpha_p = c_p/c_0$        | 0.12               | 0.15 | 0.17 | 0.14 |      |

Table 3.1. Calibrated parameters

is defined as the best possible performance for a given total buffer area. It has to be noted again that we only consider uniformly segmented lines.

So, let  $l=\alpha l_{crit}$  and  $w_b=\beta w_{opt}$ , where l and  $w_b$  are our area-constrained segment length and buffer size respectively. We will consider  $\alpha\geq 1$  and  $0<\beta\leq 1$ , assuming that the optimum always lies in that range. They occur when  $l>l_{crit}$  and  $w_b< w_{opt}$ . Also, let  $\gamma=A/A_{opt}$ , that is,  $\gamma$  ( $0<\gamma\leq 1$ ) is the ratio of buffer area in the area-constrained case to that in the area-unconstrained case. We will in sequel refer to  $\gamma$  as the normalized total buffer area, to  $\beta$  as the normalized single buffer area and to  $\alpha$  as the normalized buffer distance.

The area A for buffering a line of length L, with segments of length l, is given by the number of segments times the area of one buffer, denoted by  $A_b$ . This area is proportional to  $w_b$ , say  $A_b = \frac{L}{l} . L_{\rm eff} . w_b$ . The total buffer area normalized to the area for optimal buffering, denoted by  $\gamma$ , is given by:

$$\gamma = \frac{A}{A_{opt}} = \frac{L.L_{\text{eff}}.w_b}{l} \cdot \frac{l_{crit}}{L.L_{\text{eff}}.w_{opt}} = \frac{\beta}{\alpha}$$

(3.12)

Substituting (3.3) and (3.4) yields

$$\gamma = \frac{\beta}{\alpha} = \sqrt{\frac{b}{a} \frac{\tau_0 c_0}{r_0}} \frac{1}{c} \frac{w_b}{l} \tag{3.13}$$

Because we are considering uniformly segmented lines, this expression is independent of L. The area expressed by  $\gamma$  is then proportional to the total area of the complete line if the number of segments is large enough such that it can be approximated by the number of buffers. (Always, the number of buffers is one plus the number of segments.) This assumption sensibly simplifies our analytical approach and gives a worst-case solution. That is, the simulated performance for a certain area is always better than the performance predicted by the model. Later in section 3.3, we will show that if we compensate for this difference, the simulated and the predicted results show excellent agreement.

Now, substituting the values  $w_b = \beta w_{opt} = \gamma \alpha w_{opt}$  and l in the reciprocal velocity, equation (3.7), we obtain

$$v^{-1}(\alpha, \gamma) = \frac{\sqrt{\tau_i}(\sqrt{ab\tau_0} + \frac{b\sqrt{r_0c_0}}{\gamma})}{\alpha} + \sqrt{\tau_i}(\sqrt{ab\tau_0} + b\sqrt{r_0c_0}\gamma)\alpha$$

(3.14)

This equation is a function of  $\alpha$ , with the same structure of dependency as (3.7) on both  $w_b$  and l. It reaches a minimum when the derivative w.r.t.  $\alpha$

equals zero, resulting in:

$$\alpha_{opt}(\gamma) = \sqrt{\frac{\sqrt{ab\tau_0} + \frac{b\sqrt{r_0c_0}}{\gamma}}{\sqrt{ab\tau_0} + b\sqrt{r_0c_0}\gamma}}$$

(3.15)

and the buffer size ratio becomes:

$$\beta_{opt}(\gamma) = \alpha_{opt}(\gamma).\gamma \tag{3.16}$$

Note that we see  $\alpha$  as a function of  $\gamma$ , that is, for each value of  $\gamma$ , equation (3.15) gives the value of  $\alpha$  that minimizes the reciprocal velocity (and thus maximizes the performance) for that  $\gamma$ . Because  $\gamma$  is defined as the normalized buffer area, equations (3.15) and (3.16) present the optimal trade-off between segment length and buffer size versus area. These equations are our principle sizing results for area constrained repeater insertion.

The key to this behavior is in equation (3.12), where it is shown that  $\gamma = \beta/\alpha$ . Although both  $\alpha$  and  $\beta$  can be chosen independently, this equation establishes an elegant and useful connection to the ratio of the total buffer area,  $\gamma$ , such that the results (3.15) and (3.16) will follow.

If we substitute  $\alpha_{opt}(\gamma)$  into (3.12) and (3.14) and we take the ratio, we will find the normalized performance:

$$\frac{v_{min}^{-1}(\gamma)}{v_{min}^{-1}} = \frac{\sqrt{(\sqrt{ab\tau_0} + \frac{b\sqrt{r_0c_0}}{\gamma})(\sqrt{ab\tau_0} + b\sqrt{r_0c_0}\gamma)}}{\sqrt{ab\tau_0} + b\sqrt{r_0c_0}}$$

(3.17)

This equation, unlike the equation for  $v_{min}^{-1}$  alone, but like the evaluation for  $\tau_{crit}$ , is independent of the wire geometry. We will use this fact in section 7.2 on throughput driven repeater insertion.

The delay of a segment of the wire can be expressed by:

$$\tau(\gamma) = 2b\tau_0 \left( 1 + \sqrt{\frac{b}{a} \frac{r_0 c_0}{\tau_0}} \frac{1}{\gamma} \right) \tag{3.18}$$

which only differs form (3.5) in the  $1/\gamma$  term.

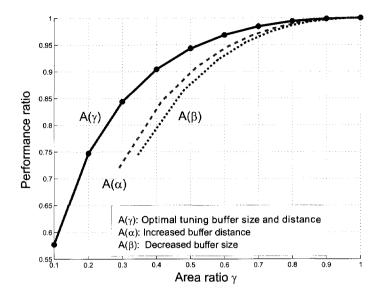

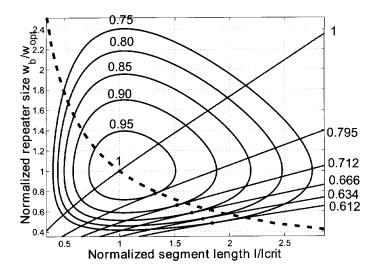

Figure 3.2 plots the normalized performance versus the normalized area. The solid line, labelled with  $A(\gamma)$ , is the result of the equation (3.17), where the normalized area is given by  $\gamma=\beta/\alpha$ . This graph really confirms that the ultimate performance is expensive in terms of area. For example, 50% of the total buffer area is needed for 95% of the absolute maximum speed and 20% of total area for 75% of the speed and only 10% of the total

**Figure 3.2.** Normalized relation between total buffer area and performance

area for 57% of the speed. It follows from (3.17) that the curve presented in figure 3.2 is independent from the geometry of the wire and partly dependent on the technology through the ratio  $c_p/c_0$ . However this ratio tends to remain pretty constant through technology scaling and then the figure 3.2 tends to be same.

For comparison, the graph also shows two other area reduction scenarios. The dashed line, labelled with  $A(\alpha)$ , corresponds to the case with optimal buffer size but increased segment length and the dotted line, labelled with  $A(\beta)$ , corresponds to the case with optimal segment length but reduced buffer size.

Like equation (3.12), we can derive

$$\frac{A(\alpha)}{A_{opt}} = \frac{L.L_{\text{eff}}.w_{opt}}{l} \cdot \frac{l_{crit}}{L.L_{\text{eff}}.w_{opt}} = \frac{l_{crit}}{l} = \frac{1}{\alpha}$$

(3.19)

and

$$\frac{A(\beta)}{A_{opt}} = \frac{L.L_{\text{eff}}.w_b}{l_{crit}} \cdot \frac{l_{crit}}{L.L_{\text{eff}}.w_{opt}} = \frac{w_b}{w_{opt}} = \beta$$

(3.20)

and the normalized performance follows analogously to (3.17). We can conclude that the  $A(\gamma)$  solution indeed presents a better trade-off than the  $A(\alpha)$  and  $A(\beta)$  solutions.

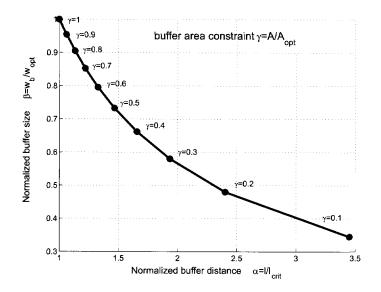

Figure 3.3 shows the optimal trade-off relation between buffer size and segment length, as derived from (3.12). The point (1,1) corresponds to the unconstrained optimum, increasing the segment length goes together with reducing the buffer size. The dots along the curve correspond to  $\gamma = 1, 0.9, \ldots, 0.1$

**Figure 3.3**. Normalized relation between buffer size and segmentation length

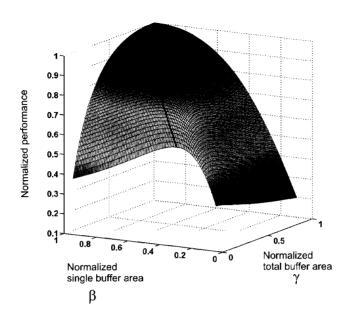

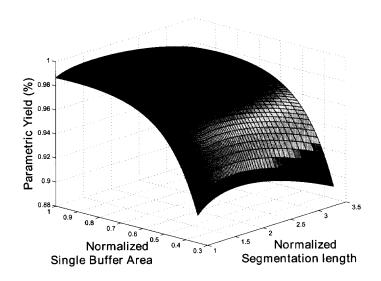

A graphical confirmation that  $A(\gamma)$  is indeed the best possible trade-off, is presented in figure 3.4. It plots the normalized total buffer area  $(\gamma)$  and the normalized single buffer area  $(\beta)$  along the two horizontal axes and the normalized performance along the vertical axis. Via (3.12), each point on the horizontal  $(\beta,\gamma)$  plane also corresponds to a value of  $\alpha$ , i.e.  $\alpha=\beta/\gamma$ . The surface mesh in the graph shows the normalized performance, as obtained by substituting  $\alpha$  and  $\beta$  in 3.14.

However, not all  $(\gamma, \beta)$  pairs satisfy our optimality relation (3.15). Those that do, are highlighted on the surface mesh with the solid line. Now, by traversing the horizontal plane along the lines of constant area (i.e.  $\gamma$ ), we can see that the highest performance indeed occurs at the highlighted line corresponding to (3.15). Again this confirms the fact that repeater insertion using (3.15) and (3.16) presents the best trade-off between area and performance.

**Figure 3.4.** Optimal performance by assessing single buffer size for constrained area

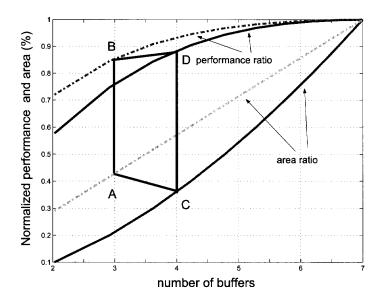

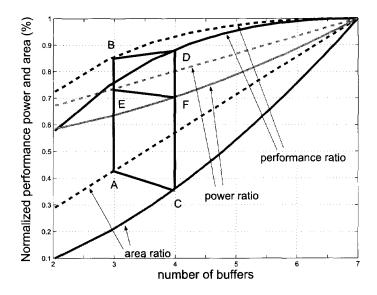

Figure 3.5 shows for a line of 2cm the result from our area-constrained repeater insertion as a function of the number of buffers. For this graph, we are assuming a typical  $0.18\mu m$  technology from the MOSIS website [40] and we consider the uppermost metal layer. Both the wire width and spacing are  $0.7\mu m$  and the dielectric has k=3.5 with a  $1\mu m$  thickness to the metal layer beneath. We are considering a buffered line that is in between two other lines, assumed grounded. Its capacitance was derived from closed-form models presented in [65] and included in the Berkeley Prediction Model [10]. The transistors were characterized using the procedure in section 3.2. The results are:

| $r_0 = 3k\Omega.\mu m$  | $c_0 = 8.44 fF/\mu m$ | $\alpha_p = 0.12$ |

|-------------------------|-----------------------|-------------------|

| $r = 23.8m\Omega/\mu m$ | $c = 23.7 fF/\mu m$   |                   |

**Table 3.2.** Typical parameters for  $0.18\mu m$  technology

Given the data, (3.3) and (3.4) with a=0.38 and b=0.69 (see section 2.3) will give  $l_{crit}=2.82mm$  and  $w_{opt}=60\mu m$ . Rounding the results to 7 repeaters of size  $w_{opt}$ , the optimal performance is  $v=3.51e^{+13}\mu m/s$ .

**Figure 3.5.** Normalized relation between performance and buffer area as function of the number of buffers

Figure 3.5 has along the horizontal axis the number of buffers and along the vertical axis the normalized performance (w.r.t. the unconstrained optimum performance) as well as the normalized total buffer area (with respect to the area for unconstrained optimum performance). The graph has two sets of curves, one for performance and one for the area ratio. The solid curves are from our area-constrained buffer insertion, while the dashed curves belong to the case where buffers keep their unconstrained optimum size but with the segment length increased. This will indeed give a straight line for the area ratio, since, with fixed buffer size, the total area is proportional to the number of buffers.

If we look at the case of three buffers with size  $w_{opt}$  (point A in the graph), and the associated performance (point B), then we see that, using the area-constrained repeater insertion results, better performance (point D) is achieved with less area (point C) though four buffers have been inserted.

Finally, we compare our analytic model with results from spice simulations for the same  $0.18\mu m$  technology as above. The simulation served to determine the period of the same 7-stage ring oscillator with a 7-stage  $\pi$ -model for interconnect as was used for calibration earlier in this section. Using a ring oscillator automatically produces realistic waveforms at the

input of each inverter, which is an advantage over using synthetic step or ramp inputs. For each value of  $\gamma$ , the transistors and interconnect in the oscillator were sized according to (3.15) and (3.16). The performance was obtained by dividing the period of oscillation by 14.

Figure 3.6. Comparison between spice and the proposed model

The results are depicted in figure 3.6, again with area ratio against performance ratio. The solid curve presents the results of (3.17) for that specific technology. The dashed curve presents the spice results, with the same normalization as for the analytic results. In point (1,1) both results match precisely, of course, since this point was used for calibration of the model. However, the results also match very well when the area is reduced, confirming the validity and fidelity of our results.

### 3.4 Area-power-delay trade-offs

We adopt the repeater power dissipation as proposed in [8]:

$$P_{repeater} = P_{switching} + P_{leakage} + P_{short-circuit}$$

(3.21)

where the terms are respectively the *switching power*  $P_{switching}$ , the *leakage* power  $P_{leakage}$ , and the *short-circuit power*  $P_{short-circuit}$ , explained below.

**Switching Power:** The switching power is the power needed to charge the total fanout capacity. For an inserted buffer the latter consists of wire capacitance, parasitic capacitance and input gate capacitance. Consequently,

$$P_{switching} = \alpha_1(w_b(c_p + c_0) + lc)V_{DD}^2 f_{clk}$$

(3.22)

where  $\alpha_1$ , the *activity factor*, is the fraction of repeaters that are on average, switching in a clock cycle. This number can typically be taken 0.15. The precise value does not influence the validity of the results to be developed.  $V_{DD}$  is the supply voltage and  $f_{clk}$  is the clock frequency.

**Leakage Power:** The leakage power is due to the current flowing in the reverse-biased diode junctions of the transistors, located between source or drain and the substrate. The leakage power can be modelled as:

$$P_{leakage} = \frac{1}{2} V_{DD} (I_{\text{offn}} W_n + I_{\text{offp}} W_p) \simeq \frac{3}{2} V_{DD} I_{\text{offn}} w_b$$

(3.23)

The assumptions are here that  $I_{\rm offn} \simeq I_{\rm offp}$  and  $W_p = 2W_n = 2w_b$ . Leakage current is caused by the thermally generated carriers and the generation of these carriers grows exponentially with the temperature. At  $85^{\circ}C$ , the leakage current increases by a factor of 60 over the room-temperature values. Since the temperature is a function of the dissipated heat, it becomes important to use efficient heat removal mechanisms. According to some authors [8] this term is expected to become significant and even dominant compared with the other terms in (3.21).

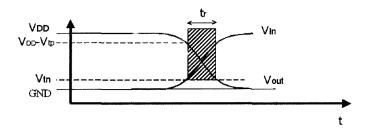

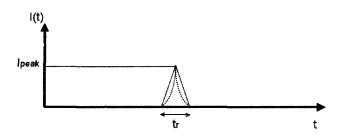

**Short circuit Power:** The finite slope of the input signal causes a situation where both nmos and cmos transistors in an inverter are conducting for a certain time  $t_r$ . There is then a current path from  $V_{DD}$  to GND which causes power consumption. Short-circuit power can be modelled as follows:

$$P_{short-circuit} = \alpha_1 t_r V_{DD} I_{peak} f_{clk} \frac{3}{2} V_{DD} I_{offn} w_b$$

(3.24)

It depends on the rise time  $t_r$  as shown in figure 3.7. It has been demonstrated, by using spice simulations, that  $I_{peak} \simeq w_b I_{short-circuit}$  where  $I_{short-circuit}$  is fairly constant (and equal to  $65\mu A/\mu m$  across all technologies).

If we assume that the input voltage waveform can be approximated by a single time-constant exponential and that  $V_{t_n} = V_{t_p} = 1/4V_{DD}$  we can

**Figure 3.7**. Voltage and approximated current waveforms for a CMOS inverter

relate the rise time  $t_r$  to the elmore delay of a buffered segment  $\tau$  by the following equation:

$$t_r = \tau \ln \left( \frac{V_{DD} - V_{t_p}}{V_{t_n}} \right) = \tau \ln 3$$

(3.25)

The contribution of this term remains relatively small [8]. Moreover, for smaller technologies it becomes less and less significant when compared to the increased leakage current. If we remain close to the unconstrained optimal buffer insertion,  $\tau$  and thus  $t_r$  will be small and then so is short-circuit power. However, in the next section we will show that for certain non-uniform area-constrained buffer insertions the relative contribution of the short-circuit power is no longer negligible.

Substituting the individual contributions in equation 3.21 yields for a

single segment of length l and a repeater with buffer size  $w_b$

$$P_{repeater} = P_{switching} + P_{leakage} + P_{short-circuit}$$

=  $k_1((c_0 + c_p)w_b + cl) + k_2w_b + k_3w_b\tau$  (3.26)

where  $k_1 = \alpha_1 V_{DD}^2 f_{clk}$ ,  $k_2 = \frac{3}{2} V_{DD} I_{offn}$  and  $k_3 = \alpha_1 V_{DD} I_{sc} f_{clk} \ln 3$  are constants that do not depend on buffer sizing. When the short-circuit power is neglected, (3.26) can be rewritten as:

$$P_{repeater} \approx P_{switching} + P_{leakage}$$

$$= k_1((c_0 + c_p)w_b + cl) + k_2w_b$$

(3.27)

For a line with n buffers uniformly inserted we can consider the power p per unit length: it

$$p = \frac{nP_{repeater}}{L} = (k_1(c_0 + c_p) + k_2)\frac{w_b}{l} + k_1c$$

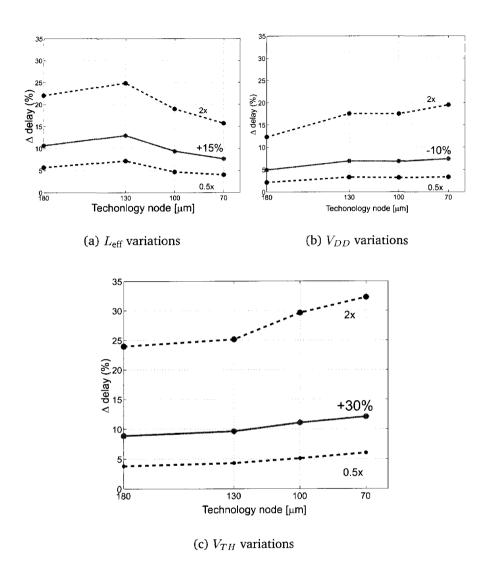

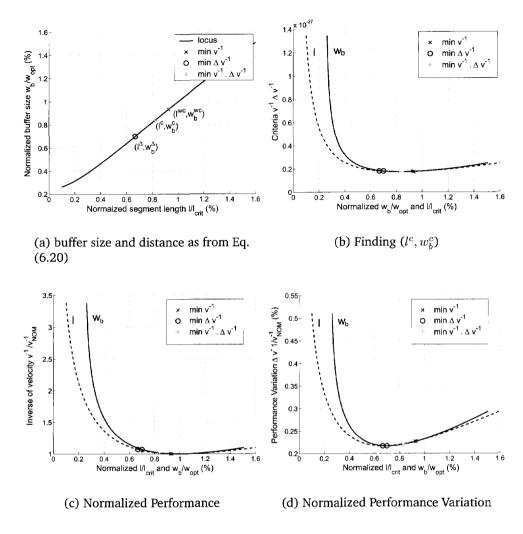

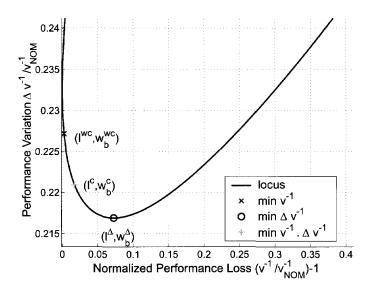

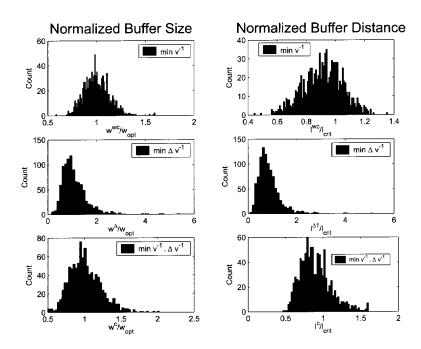

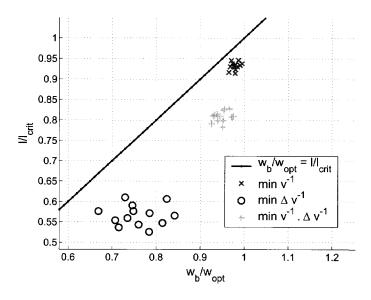

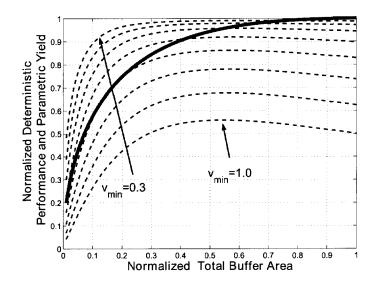

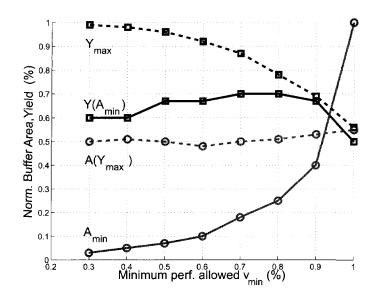

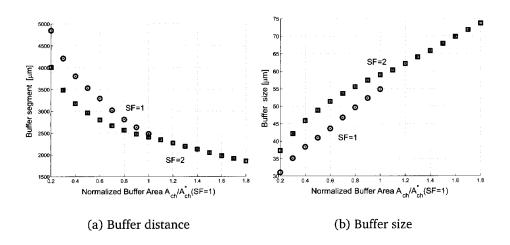

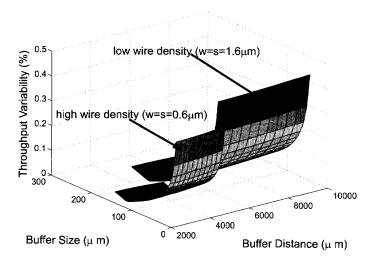

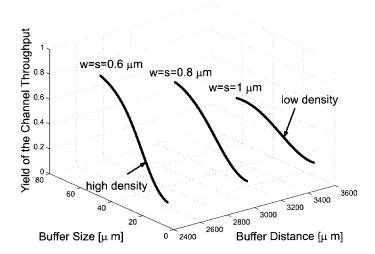

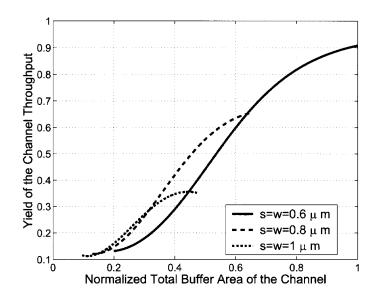

(3.28)