MSc thesis project proposal

Flip-chip interconnect with superconducting pillars

Background

Quantum computers are increasingly recognized as a transformative technology with the potential to revolutionize fields ranging from cryptography and drug discovery to materials science and optimization problems. Superconducting qubits have demonstrated the ability to achieve high-fidelity quantum operations and control, meaning they can perform quantum gates and measurements with a high degree of accuracy and reliability. This is essential for building fault-tolerant quantum systems capable of running complex algorithms without significant errors. However, as the number of qubits increases, the likelihood of encountering issues with Josephson Junctions in superconducting qubits also grows. This impending challenge is prompting a shift in both the scientific community and industry towards adopting a modular multi-chip quantum processing unit (QPU) instead of a single monolithic chip approach. In this project, the main goal is to conduct a feasibility study of a modular multi-chip QPU and experimentally demonstrate its early performance.

Similar to conventional advanced microelectronics, flip-chip technology can play a crucial role in assembling multiple quantum chips. However, unlike traditional microelectronics, quantum computers must operate at cryogenic temperatures, where most materials exhibit unfavourable mechanical properties, such as increased brittleness, which hinders the formation of reliable electrical interconnects. Moreover, the interconnects must be superconducting to preserve quantum coherence, significantly limiting material choices for integration. Additionally, flip-chip technology for quantum chips must maintain a precise stand-off height—the specific distance between the mating surfaces of the chips—to ensure proper mechanical and electrical performance.

This project proposes a novel approach for QPU packaging: the required stand-off height is provided by pillars coated with metals commonly used for chip interconnects, such as aluminium or tin, both superconductors. In this design, the mechanical robustness at cryogenic temperatures is ensured by the pillar structure, while the superconducting metal coating provides the electrical interconnects. The pillar metallization is selected to be compatible with the metallization on both quantum chips, ensuring reliable superconducting connections.

Technology development

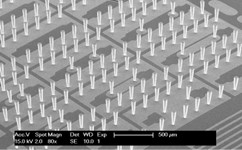

One of the most promising materials for pillar formation is the photo-imageable polyimide SU-8. Using microlithography, large arrays of pillars with precise diameters, shapes, and heights can be fabricated, as illustrated in the figure.

However, there is limited information available regarding the mechanical properties of polyimides at cryogenic temperatures. Additionally, the impact of thin metal coatings applied to the pillars must also be considered.

To address these gaps, a feasibility study will be conducted that includes the design, fabrication, and testing of relevant polyimide test structures at cryogenic temperatures. This study aims to provide a better estimation of the mechanical properties of polyimide and metal-coated polyimide structures at cryogenic temperatures. The results will support the further optimization of flip-chip pillar designs through a combined approach of finite element analysis and experimental validation. The optimized design and process parameters will then be applied to fabricate a pillar flip-chip interconnect to demonstrate the concept.

Assignment

This master’s thesis aims to investigate key design and process parameters for fabricating a pillar flip-chip interconnect intended for the integration of quantum computing chips. The application demands operation at extremely low temperatures, requires an all-superconducting interconnect, and a precise stand-off height between the two chips. The outcome of this project will be a proof-of-concept for the pillar flip-chip interconnect, along with design and process guidelines to facilitate the further scaling of this interconnect technology, enabling heterogeneous integration of quantum computing chips.

Project activities

- Conduct a literature review to assess the state of the art.

- Define a design of experiments (DoE) to estimate the mechanical properties of the photo-imageable polymer at cryogenic temperatures.

- Develop a process flowchart for fabrication in the EKL cleanroom.

- Complete cleanroom process training.

- Design and fabricate relevant test structures.

- Perform cryogenic testing and evaluate the results.

- Fabricate devices with improved layout and optimized process parameters.

- Perform electrical characterization at relevant temperatures.

- Write the final report and thesis.

Contact information

Dr. Henk van Zeijl, h.w.vanzeijl@tudelft.nl

Dr. Nadia Haider, s.n.haider@tudelft.nl

Prof. Willem van Driel, willem.vandriel@tudelft.nl

Contact

prof.dr.ir. Willem van Driel

Electronic Components, Technology and Materials Group

Department of Microelectronics

Last modified: 2026-02-06