# Power-Aware Architecting

for data-dominated applications

## Power-Aware Architecting

for data-dominated applications

## Power-Aware Architecting

## for data-dominated applications

#### Proefschrift

ter verkrijging van de graad van doctor aan de Technische Universiteit Delft, op gezag van de Rector Magnificus prof. dr. ir. J.T. Fokkema, in het openbaar te verdedigen ten overstaan van een commissie, door het College voor Promoties aangewezen, op maandag 19 april 2004 te 15:30 uur

door

Maarten DITZEL

elektrotechnisch ingenieur geboren te Hattem.

Dit proefschrift is goedgekeurd door de promotor:

Prof. dr. ir. R.H.J.M. Otten

Toegevoegd promotor:

Dr. ir. W.A. Serdijn

#### Samenstelling promotiecommissie:

Rector Magnificus voorzitter

Prof. dr. ir. R.H.J.M. Otten Technische Universiteit Delft, promotor

Dr. ir. W.A. Serdijn Technische Universiteit Delft, toegevoegd promotor

Prof. dr. ir. H.J. Sips

Technische Universiteit Delft

Prof. dr. J.R. Long

Technische Universiteit Delft

Prof. dr. ir. C.H. Slump Universiteit Twente

Prof. dr. ir. P.H.N. de With Technische Universiteit Eindhoven Prof. dr. ir. J.L. van Meerbergen Technische Universiteit Eindhoven

M. Ditzel. Power-aware architecting for data-dominated applications. PhD thesis, Delft University of Technology, April 2004.

ISBN: 90-6464-398-9

Copyright © 2005 by Maarten Ditzel.

All rights reserved. No part of the material protected by this copyright notice may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying, recording or by any information storage and retrieval system, without permission from the author.

Printed in the Netherlands by:

Ponsen en Looijen B.V., Wageningen.

## Contents

| 1        | Intr | roduction                             | 1  |

|----------|------|---------------------------------------|----|

|          | 1.1  | High-level system design              | 2  |

|          |      | 1.1.1 Hardware-software partitioning  | 3  |

|          |      | 1.1.2 Hardware specification          | 4  |

|          |      | 1.1.3 Design flow                     | 6  |

|          | 1.2  | Power as design constraint            | 7  |

|          | 1.3  | Application                           | 9  |

|          | 1.4  | Outline                               | 9  |

| <b>2</b> | Des  | ign trade-offs 1                      | 1  |

|          | 2.1  |                                       | .1 |

|          | 2.2  |                                       | 1  |

|          |      | 2.2.1 Gate area estimation            | 2  |

|          |      | 2.2.2 Interconnect estimation         | 5  |

|          | 2.3  |                                       | 6  |

|          |      | 2.3.1 Resource delay estimation       | 6  |

|          |      | 2.3.2 System level delay estimation   | 9  |

|          | 2.4  |                                       | 20 |

|          |      | 2.4.1 Static power dissipation        | 22 |

|          |      | 2.4.2 Dynamic power dissipation       | 22 |

|          |      | 2.4.3 Activity-based power estimation | 23 |

|          |      |                                       | 26 |

|          | 2.5  | Area, delay, power trade-offs         | 27 |

|          |      | 2.5.1 Area versus delay               | 27 |

|          |      | 2.5.2 Delay versus power              | 29 |

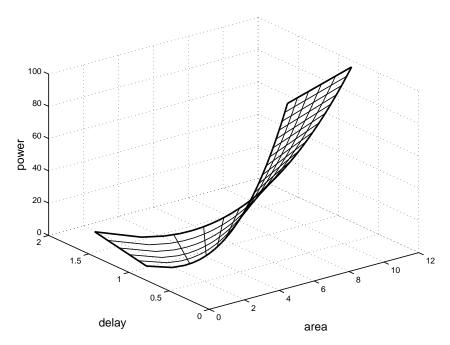

|          |      | 2.5.3 Area versus delay versus power  | 80 |

|          | 2.6  | Summary                               | 32 |

| 3        | Arc  | chitecting with uncertainties 3       | 5  |

|          | 3.1  | Introduction                          | 35 |

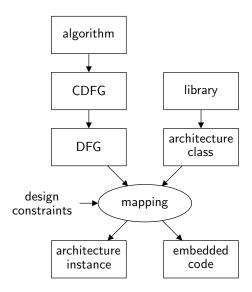

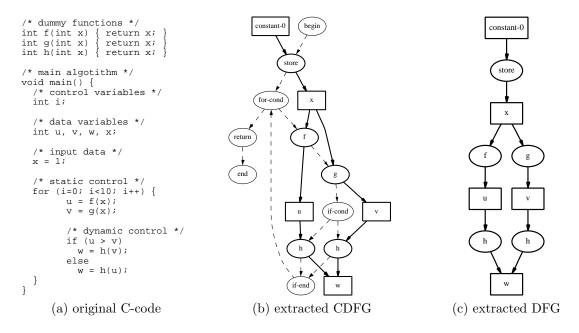

|          | 3.2  | Application model                     | 37 |

|          | 3.3  | Architecture class                    |    |

|   | 3.4 |        | vare-software partitioning                      |

|---|-----|--------|-------------------------------------------------|

|   |     | 3.4.1  | Selection constraints                           |

|   |     | 3.4.2  | Cost constraints                                |

|   |     | 3.4.3  | Mixed integer linear programming formulation 49 |

|   | 3.5 | Exten  | sion to multiple algorithms                     |

|   |     | 3.5.1  | Multiple algorithm support                      |

|   |     | 3.5.2  | Algorithm selection support                     |

|   |     | 3.5.3  | Combined solution                               |

|   | 3.6 | Dealin | ng with uncertainty                             |

|   | 3.7 | C to S | SystemC conversion                              |

|   |     | 3.7.1  | SystemC language                                |

|   |     | 3.7.2  | Conversion approach                             |

|   |     | 3.7.3  | Behavioral conversion                           |

|   |     | 3.7.4  | Structural conversion                           |

|   |     | 3.7.5  | Conversion alternatives                         |

|   | 3.8 |        | ary                                             |

|   |     |        |                                                 |

| 4 |     |        | rier communications 63                          |

|   | 4.1 |        | uction                                          |

|   | 4.2 |        | path channels                                   |

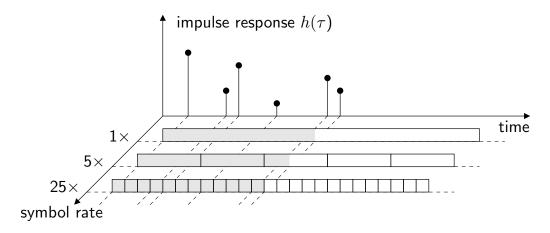

|   |     | 4.2.1  | Channel impulse response                        |

|   |     | 4.2.2  | Delay spread                                    |

|   |     | 4.2.3  | Inter-symbol interference                       |

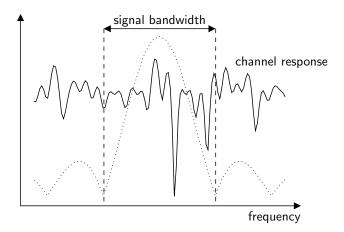

|   |     | 4.2.4  | Frequency-selective fading                      |

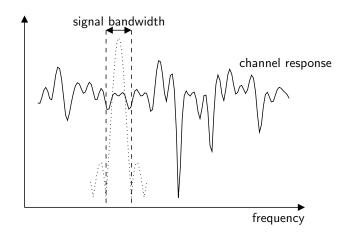

|   | 4.3 | Princi | ples of multi-carrier modulation                |

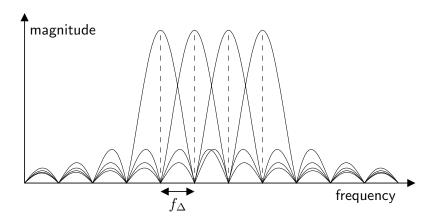

|   |     | 4.3.1  | Orthogonal FDM                                  |

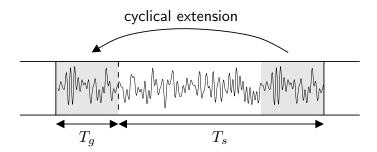

|   |     | 4.3.2  | Guard interval                                  |

|   |     | 4.3.3  | OFDM demodulation                               |

|   | 4.4 | Optim  | nal energy assignment                           |

|   |     | 4.4.1  | Channel model                                   |

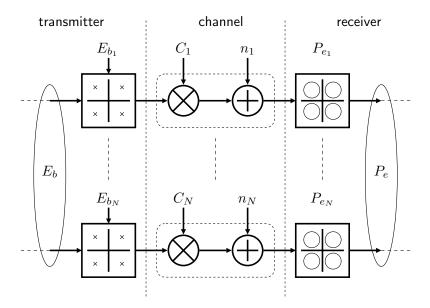

|   |     | 4.4.2  | System model                                    |

|   |     | 4.4.3  | Optimization problem                            |

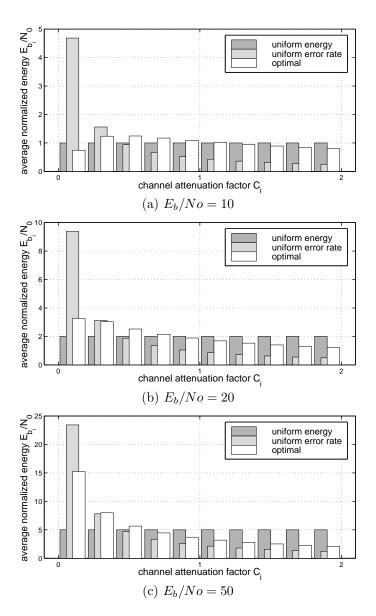

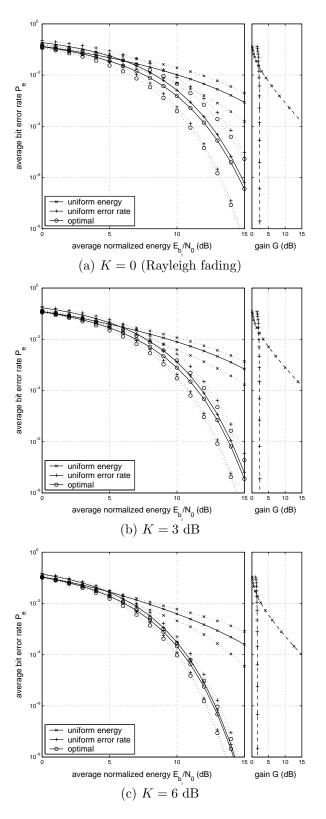

|   |     | 4.4.4  | Comparison                                      |

|   | 4.5 | Quant  | ization level                                   |

|   |     | 4.5.1  | System model                                    |

|   |     | 4.5.2  | Performance of quantized OFDM systems           |

|   |     | 4.5.3  | Verification                                    |

|   | 4.6 |        | ng level                                        |

|   | 1.0 | 4.6.1  | System model                                    |

|   |     | 4.6.2  | Noise modeling                                  |

|   |     | 4.6.3  | Performance of soft-limited OFDM systems        |

|   |     | 4.6.4  | Verification                                    |

|   | 4.7 |        |                                                 |

|   | 4.1 | Summ   | ary                                             |

| <b>5</b>         | App     | olication                                                              | 91  |  |  |  |  |

|------------------|---------|------------------------------------------------------------------------|-----|--|--|--|--|

|                  | 5.1     | 1 Introduction $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ $\dots$ |     |  |  |  |  |

|                  | 5.2     | Transceiver specification                                              | 91  |  |  |  |  |

|                  |         | 5.2.1 Frequency band                                                   | 92  |  |  |  |  |

|                  |         | 5.2.2 Gross bit rate                                                   | 92  |  |  |  |  |

|                  |         | 5.2.3 Symbol format                                                    | 94  |  |  |  |  |

|                  |         | 5.2.4 Sub-symbol encoding scheme                                       | 96  |  |  |  |  |

|                  |         | 5.2.5 Time and frequency synchronization                               | 97  |  |  |  |  |

|                  |         | 5.2.6 Multiple access                                                  |     |  |  |  |  |

|                  |         | 5.2.7 Summary                                                          |     |  |  |  |  |

|                  | 5.3     | Implementation alternatives                                            |     |  |  |  |  |

|                  |         | 5.3.1 Building blocks                                                  |     |  |  |  |  |

|                  |         | 5.3.2 Processor alternatives                                           |     |  |  |  |  |

|                  |         | 5.3.3 Cost estimates                                                   |     |  |  |  |  |

|                  |         | 5.3.4 Implementation alternatives                                      |     |  |  |  |  |

|                  | - 1     | 5.3.5 Partitioning results                                             |     |  |  |  |  |

|                  | 5.4     | Summary                                                                | 115 |  |  |  |  |

| 6                | Con     | clusions                                                               | 17  |  |  |  |  |

| $\mathbf{A}$     | Ubi     | quitous Communications 1                                               | 21  |  |  |  |  |

|                  |         | Applications                                                           | 121 |  |  |  |  |

|                  |         | Necessities and consequences                                           |     |  |  |  |  |

|                  | A.3     | Preliminary choices                                                    |     |  |  |  |  |

|                  |         | A.3.1 Carrier frequency and OFDM modulation                            |     |  |  |  |  |

|                  |         | A.3.2 Infrastructure                                                   | 123 |  |  |  |  |

| В                | Mix     | red integer programming 1                                              | 25  |  |  |  |  |

|                  | B.1     | Linear programming                                                     | 125 |  |  |  |  |

|                  | B.2     | Mixed integer programming                                              |     |  |  |  |  |

|                  | В.3     | Boolean algebra                                                        |     |  |  |  |  |

|                  |         | B.3.1 Boolean inversion                                                |     |  |  |  |  |

|                  |         | B.3.2 Boolean and                                                      | 127 |  |  |  |  |

|                  |         | B.3.3 Boolean or                                                       |     |  |  |  |  |

| $\mathbf{C}$     | Poss    | sibilistic linear programming 1                                        | 29  |  |  |  |  |

| _                |         | Introduction                                                           |     |  |  |  |  |

|                  | C.2     | Fuzzy objective coefficients                                           |     |  |  |  |  |

|                  | _       | Fuzzy objective, constraint and limit coefficients                     |     |  |  |  |  |

| D:               |         | _                                                                      | 32  |  |  |  |  |

|                  |         | · · · · ·                                                              |     |  |  |  |  |

| Summary          |         |                                                                        |     |  |  |  |  |

| Samenvatting     |         |                                                                        |     |  |  |  |  |

| Na               | Nawoord |                                                                        |     |  |  |  |  |

| About the author |         |                                                                        |     |  |  |  |  |

## Introduction

World-wide, the demand for portable, hand-held devices is increasing strongly. More and more cellphones, personal digital assistants (PDAs), MP3 players and Game Boys are bought. At the same time, there is an increase in the number of different tasks such devices are expected to be capable of doing, ranging from image processing to data communications. Thus, an overall trend is visible towards ever smaller devices integrating ever more functions. Furthermore, most processing tasks tend to be data-centric, i.e., most computational effort is put in processing data streams. As such, the operating cores can be seen as data stream processors.

The tendency of cramming more functionality in smaller devices is enabled by the continuing growing capabilities of semi-conductor technology. Ever smaller devices can operate on ever higher frequencies, at lower operating supply voltages. Unfortunately, the advances in semi-conductor technology do not solve all of our problems, because we do not want to do the same with improved devices, we want to do more with less. Therefore, the tools used to design and create the chips have to be improved, so that the increasing design gap between ideas and silicon realizations can be bridged.

The call for portable devices, especially in telecommunication applications, imposes increasingly strict requirements on, for instance, the dimensions and the energy consumption of the apparatus. Ideally, your cellphone should be able to operate for months on a single lightweight battery. Unfortunately, the energy storage capacity of batteries is only being improved slowly [57, 66]. Therefore, already at the design stage, care must be taken to reduce the energy consumption of the devices as much as possible, but this should not affect the performance of the device or the required silicon area. A designer must find a balance between these competing design objectives.

In this thesis, a high-level design method is presented that aids the designer in finding that balance. Furthermore, design automation tools are implemented to test and verify this method for the design of an OFDM (orthogonal frequency-division multiplexing) transceiver. This chapter introduces the ideas and concepts underlying the method and tools.

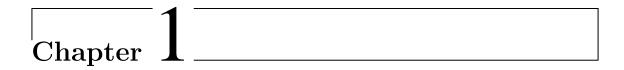

Figure 1.1: The abstraction pyramid represents the trade-offs between the abstraction level, the cost of changes, the impact of design decisions and available information.

## 1.1 High-level system design

As device sizes shrink, the complexity of a chip increases. To describe the complex designs, designers have to make use of languages at higher levels of abstraction in order to meet time-to-market deadlines. Current hardware description languages (HDLs) such as VHDL (very high speed integrated circuit hardware description language) and Verilog are not equipped to handle these levels of abstraction. As a result, designers resort to general programming languages to start with the functional exploration of their designs.

High-level exploration of the design space is crucial when one must design an embedded system with competing objectives while limited design time is available. Significant changes to the functionality or the architecture at lower levels are extremely expensive and should be avoided in all cases. Furthermore, choices made at a high level tend to have a huge impact on the performance and costs of the final design. For example: given an ultra low-power multiplier, a change in algorithm that doubles or triples the number of multiplications still causes a large increase in the power consumption. In figure 1.1, the trade-offs between abstraction level, the cost of changes, the impact of design decisions and the available information is depicted in a so-called abstraction pyramid, originally introduced in [34]. A similar representation of the design space "reachability" can be found in [13].

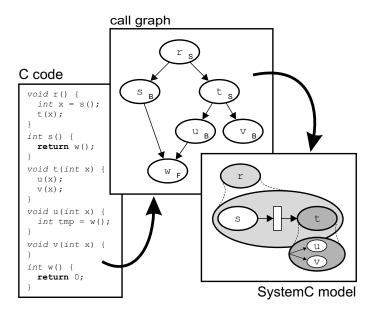

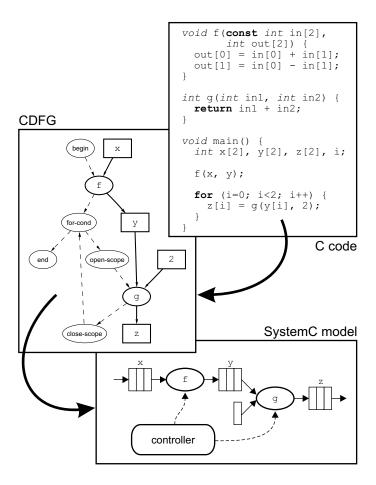

Because of their popularity as general-purpose programming languages, and the corresponding abundance of libraries and tools, C and C<sup>++</sup> are commonly used to construct an executable specification of the functional part of the design. The

desired functionality is described by a set of functions that together implement the algorithm. Functions are expressed purely sequentially and an explicit notion of time is lacking. Hence, timing can only be expressed as the order in which the functions are called.

However, the high abstraction level of these programming languages allows for a very terse description of the algorithm. Moreover, changes to the algorithm are easily incorporated and, because of the high simulation speeds, quickly verified. These properties make programming languages like C or C<sup>++</sup> the de facto standard for the initial, high-level specification of a complex design, even though originally these languages were never intended for this purpose.

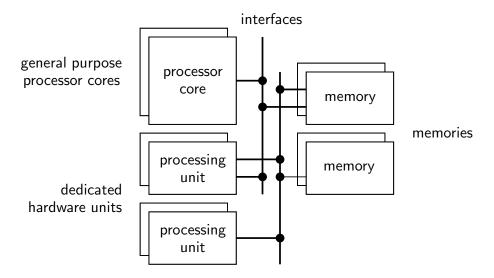

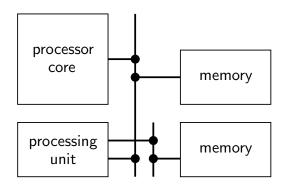

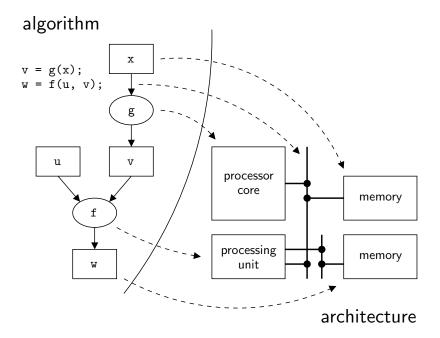

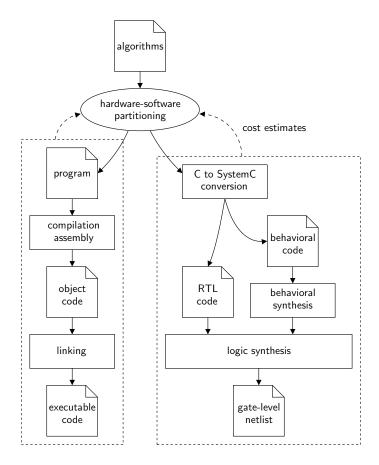

### 1.1.1 Hardware-software partitioning

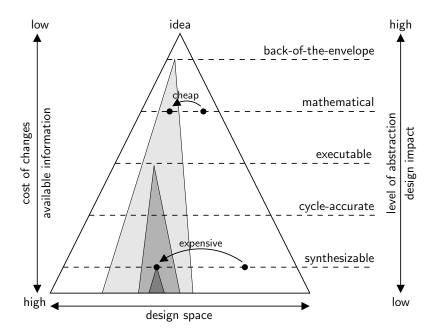

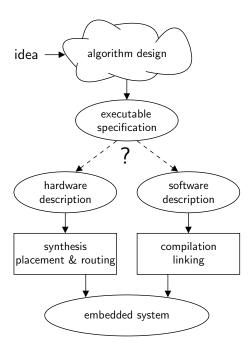

Once the initial specification of the algorithm is fixed, one of the first questions that arises is which parts of the algorithm should be implemented in hardware and which in software in order to find an implementation that best suits the design's requirements (see figure 1.2). A key problem is that at this stage usually only insufficient or at least inaccurate information to make a proper decision is available to the designer. Moreover, the partitioning problem is a multi-objective optimization problem and although methods for multi-objective optimization exist, normally the designer wants to have a firm control over the decision process. In the end, it is up to the designer to prioritize the design objectives.

Figure 1.2: Once the algorithm is fixed, the design flow of an embedded system starts with an executable specification. Subsequently, it is decided which parts to implement in software and which in hardware.

The overwhelming number of options and the pace with which they change, render it impossible for a human to make a sound decision about today's complex designs. He simply cannot predict the consequences of a particular choice accurately. Therefore, a tool to quickly identify the trade-offs is indispensable in making well-founded partitioning decisions. Such a tool should be able to cope with the inherent uncertainties due to the high level of design.

In addition to the aforementioned uncertainties there is another complicating factor: the precise algorithm or the set of algorithms to be implemented may not even be given yet. Several implementations and alternatives may be available, out of which the best should be selected and for which an optimal architecture should be constructed.

In support of the partitioning tool, additional instruments should be available to quickly generate estimates of cost and performance figures, if not absolute then at least relative numbers. If all these tools are available, a designer can quickly explore different partitionings and select the one that best suits his needs. In this thesis a solution to the partitioning problem is presented. Its workings are verified by implementing the solution in a partitioning tool and applying it to a test case.

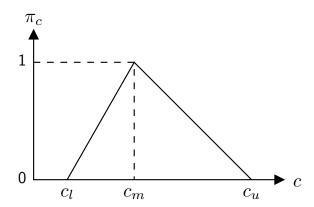

The partitioning tool takes as input a series of algorithms specified as data flow graphs. The possible architectures are specified by data processing blocks, such as processing cores and memories, and data transfer elements such as busses. The optimization problem itself is formulated as a mathematical programming problem, more precisely, as a mixed integer linear program. In order to deal with the imprecise nature of the cost and performance figures, the linear program uses fuzzy instead of crisp numbers to represent the coefficients. The necessary fuzzy solver is constructed in such a way that it optimizes the most probable outcome, while minimizing the chances of finding a worse solution and maximizing the chances of a better one.

## 1.1.2 Hardware specification

After establishing the functional correctness, one has to create a high-level hardware description of the design for the parts of the design to be implemented in hardware. That is, one must model the system as concurrently executing processes. Also the notion of time has to be introduced. To represent the system at this level, one can use a hardware description language.

A hardware description language typically supports different description models for hardware. These commonly include a register transfer level (RTL) model and a behavioral model.

• Register transfer level: Formally speaking an RTL model describes hardware as state elements (registers) together with the combinatorial logic connecting them. The resulting description is cycle accurate, both at the interfaces and internally.

RTL is best suited for a design if the design is best conceived by its structure. The structure is usually divided into a data path and a a finite state machine

(FSM) as controller. Because RTL specifies a structural view of hardware, algorithms are difficult to express. However, RTL allows the designer complete control over the architecture, enabling very high-performance designs.

• Behavioral model: A behavioral model describes a design algorithmically. Although the internal behavior of the design is not described cycle accurate, the input-output behavior is.

Behavioral languages commonly allow for higher levels of abstraction with respect to an RTL description. Hence, more concise descriptions are possible.

Today, Verilog and VHDL are the most popular HDLs. Numerous tools are available for simulation and synthesis, either directed to ASICs (application specific integrated circuit) or FPGAs (field programmable gate array).

Difficulties arise when one tries to translate the executable specification into a hardware description, because of the differences in representation: sequential versus concurrent. Current solutions that automatically convert the executable specification to an HDL either extend the language with specific constructs for hardware description, or target a predefined fixed architecture. Examples of these solutions are Ocapi [72] from IMEC, and A|RT Designer from Adelante Technologies (former Frontier Design), respectively. Serious drawbacks of these solutions are that the designer either must learn the specific extensions to standard C or  $C^{++}$ , or has to restrict himself to the particular architecture targeted. Other approaches, such as SA-C [67] and Handel-C [42] use variants of the C language, thus also forcing the designer to learn a new language.

As a final resort, the conversion can be done manually by rewriting the system model from scratch. The major drawback is the time-consuming and error-prone nature of this process. Furthermore, discrepancies between the executable specification and the hardware description are easily introduced. This significantly increases the risk that the final product does not meet its specifications. In that case, an expensive re-design would be necessary, introducing a delay in the time-to-market of the product.

Moreover, at this stage it is often still unclear which parts of the design should be implemented in software and which in hardware. Therefore, the time and effort invested in the conversion should be kept to a minimum, as some of this work might become obsolete in a later stage.

Recently, with the introduction of SystemC as a modeling language, an alternative trajectory has become possible. Now, the executable specification is translated into SystemC instead of into a conventional HDL. SystemC offers the same modeling properties as these, but additionally it provides a higher level of abstraction, effectively offering all features of the high-level programming language C<sup>++</sup>. Of course not all constructs are synthesizable, but the translated code offers a good starting point for further refinement towards synthesis.

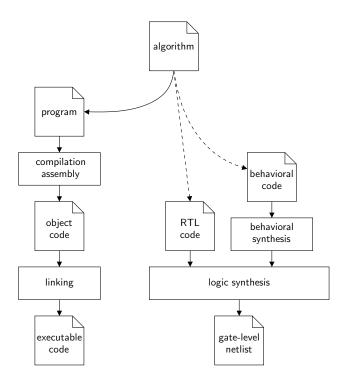

Figure 1.3: Design flow used throughout this thesis; the dashed arrows denote missing tools in the flow.

## 1.1.3 Design flow

In accordance with the arguments raised in the previous sections, we come to the design flow presented in figure 1.3. First, the algorithm to be implemented is described in a high-level programming language, in particular in C. Then, a partitioning has to be made, deciding which parts to implement in hardware and which parts to implement in software. The original C code can directly be used to describe the software, and additional steps are not needed. In contrast the C code describing the functionality of the hardware parts has to be converted into an HDL, either an RTL or a behavioral description. For both descriptions, we choose to use SystemC.

It is apparent that a number of steps cannot be done automatically yet. The first is the decision how to divide the design into hardware and software parts. The second is the automatic generation of the hardware descriptions, either using a structural (RTL) or a behavioral representation. The focus of this thesis is on partial automation of these steps, in order to quickly guide a designer towards a feasible solution that meets the requirements.

To test and verify the ideas and the design flow presented thus far, several design tools have been written to aid a chip designer in making architectural decisions at a high level. Because these decisions are made at a high level, they have a large impact on the performance and costs of the final design. In particular attention is paid to the energy consumption of a device, and therefore, power is incorporated into the design flow as one of the primary design constraints.

## 1.2 Power as design constraint

In general, power is defined as the conversion rate of energy. In the context of this thesis a more restricted definition is used, because the thesis focuses on integrated circuits (ICs). In this restricted context, power is defined as the rate at which electrical energy is converted into some other form, usually heat (dissipation). Equivalently, it is defined as the rate at which an IC consumes energy from an electrical power source.

It is important to note that the terms 'power' and 'energy' are often used interchangeably, although they are not the same quantities. To be precise, if at time instance  $\tau_0$  a system has energy  $E(\tau_0)$ , and at  $\tau_1$  only  $E(\tau_1)$  is left, then the power P is defined as the amount of energy  $\Delta E = E(\tau_1) - E(\tau_1)$  consumed in that particular time interval  $\Delta t = \tau_1 - \tau_0$

$$P = \frac{\Delta E}{\Delta t} = \frac{E(\tau_1) - E(\tau_1)}{\tau_1 - \tau_0}.$$

(1.1)

Taking the limit  $\Delta t \to 0$  leads to the definition of the instantaneous power consumption p(t) at time t

$$p(t) = \frac{d}{dt}E(t), \tag{1.2}$$

where E(t) is the energy present in the system at time t.

Power has been a constraint in the design of analog systems for a long time, for instance in medical applications such as pacemakers and hearing aids. However, power was not an issue in the design of digital systems. Area and timing were by far the most important design constraints. However, recently power has become a more and more important constraint, for a number of reasons.

- Rapidly growing complexity: The current trend towards higher operating frequencies, higher integration densities and higher performance still continues in accordance with Moore's law [45].

- Application in mobile devices: The rapidly growing demand for mobile devices, such as personal digital assistants (PDAs) and cellular phones, increases the need for battery-powered devices.

- Slowly increasing battery capacity: Unfortunately progress in battery technology cannot keep pace with advances in electronics circuits [57, 66], thereby increasing the gap between supply and demand.

- Reduced lifetimes because of heating: With the higher frequencies and the increasing integration densities, operating temperatures rise, thereby increasing the failure rate of electronic devices.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>The failure rate can be estimated using the Arrhenius equation  $\lambda = \lambda_0 e^{-\frac{E_a}{kT}}$ , where  $\lambda$  is

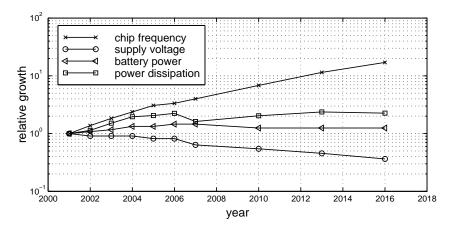

Figure 1.4: Predicted relative growth (data taken from [3]).

• Problematic power supply: The required energy must be transported from an external source (for instance a battery) onto the chip via its pins and bonding pads. Because of the large currents involved, many pins are required in order to reduce the current per pin.

A number of these effects are depicted in figure 1.4. Plotted are the relative predicted increase of frequency, supply voltage, battery power and power dissipation. The data for the graphs originate from [3]. The increase in dissipation is apparent, as is the lagging of the battery power.

Depending on the application, power consumption varies from a marginal design constraint to the most important one. It can nearly be neglected in low performance designs connected to a fixed power grid, while in high-performance battery-powered mobile devices it is crucial. Furthermore, power consumption is a dominant factor for systems which are hard to access, such as satellites, and medical systems implanted in the human body.

Various aspects of the power consumption of a system have already been investigated. In [56] a classification is given of current power management solutions for operating systems. A framework is presented that allows the implementation of cooperating power management policies at this level. Additionally, a novel scheduling algorithm is described that finds an energy-efficient setting for modern microprocessors exploiting voltage scaling. In [43] a classification is given of the sources of power dissipation in deep sub-micron CMOS logic. Reduction techniques are presented for each source of dissipation. Also a new technique to reduce the weak-inversion current is presented. This thesis focuses on the effects of design choices on, among others, the energy consumption of a design and how to make these effects quickly visible to the designer.

the failure rate,  $\lambda_0$  a reference value,  $E_a$  the activation energy of the failure mechanism, and k Boltzmann's constant [39]. With an increase of  $10^{\circ}C$  at an operating temperature of  $70^{\circ}C$ , the failure rate increases by a factor of 1.8 to 6.6 for typical values of the activation energy.

## 1.3 Application

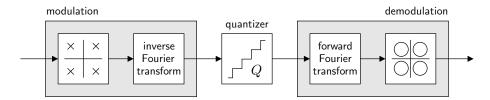

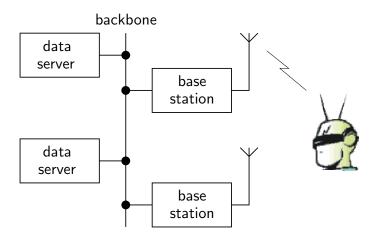

To check whether the tools created operate properly, and whether the design flow is complete, we need a representative application to serve as a test case. For this, an orthogonal frequency-division multiplexing transceiver is selected. The tools and design flow are applied to design the baseband processing of the OFDM modulator and demodulator used in the Ubiquitous Communications (UbiCom) program [36].

In the UbiCom scenario, a user is equipped with a wearable device consisting of a terminal and a see-through display. Text, graphics, images and video can be displayed before the user's eyes, properly aligned and consistent with the real world, thereby enhancing the user's view (so-called augmented reality).

To transfer all this data to and from the user, a high-speed wireless link is necessary using an OFDM transceiver. The design of the baseband processing of this transceiver is selected as a case to test the design flow and tools. It is chosen because the modulation and demodulation are data-dominated operations. Moreover, there are strongly conflicting design constraints, in particular the required high processing speed versus the severe restrictions on the energy consumption, and hence it serves as a challenging test case.

## 1.4 Outline

This thesis describes several methods and tools to come to a consistent design flow, starting with a high-level specification in C. An essential part of this flow is a new tool to automate the hardware-software partitioning. The tool finds an optimal architecture to implement one or more algorithms. The resulting architecture is optimal with respect to the chip area, the execution time, or the energy consumption.

As the successful operation of the partitioning tool depends on the quick availability of accurate estimates for area, latency and energy consumption, we need an additional tool to convert the original C code into a hardware description language, in particular into SystemC. The automated conversion from C to SystemC enables a closed design flow where tedious manual rewrites are no longer necessary. Furthermore, the automated conversion eliminates the chances of coding errors.

To test and verify the new design automation tools, we will apply the design tools to implement an OFDM transceiver. But first, we investigate several techniques to reduce the energy consumption of the OFDM transceiver beforehand.

In chapter 2 we give an overview of existing estimation techniques for area usage, delay and energy consumption. Then, both the partitioning tool and the conversion tool are described in chapter 3. In chapter 4 we describe the novel energy reduction techniques for OFDM, and in chapter 5 we discuss the implementation of the OFDM transceiver using the presented methods and tools. Finally, in chapter 6, we conclude this thesis.

## Design trade-offs

#### 2.1 Introduction

To prevent expensive re-designs in the final part of the development of a system/product the designer needs to obtain feedback about the performance and costs of the current design as early as possible in the design flow. Performance feedback is already incorporated in modern design flows, applying formal analysis, high-level functional simulations and lower-level behavioral and structural simulations.

Cost feedback, on the other hand, is only available at the final stages of the design flow, e.g. only when a net list is available. Yet, choices made at a high level may severely constrain the final product. In particular in the design of a power-limited system, power estimation early in the design cycle is crucial.

This chapter gives an overview of cost estimation techniques, more specifically techniques for determining area, delay and energy consumption. Of course, these three are not independent and therefore their dependencies, i.e., the trade-offs, are discussed in the final section of this chapter.

## 2.2 Area estimation

In the early days of VLSI design, the area consumption was the decisive limit on what could be integrated on a chip. Over the years, as chip area and transistor densities steadily grew, it remained one of the primary design constraints, because of its impact on processing costs and yield. Therefore, chips produced in large quantities are designed to be as small as possible.

The total area used for a circuit can be divided into two main categories, namely the area used by the gates, and the area due to the interconnect. As the interconnect can be positioned on top of the gates, these two overlap and the total area is not merely their sum. However, not all interconnects can be placed over the gates, so some additional area is needed to accommodate the interconnect.

#### 2.2.1 Gate area estimation

Several techniques exist for estimating the area. Depending on the level of detail available, different estimation methods and techniques are used. These include:

- transistor counting,

- complexity-based techniques, and

- Rent's rule.

Each technique is discussed in more detail in the following sections.

#### Transistor count

If a net list is available, the area of the design can be estimated by counting the number of transistors used and by multiplying the result with the area of a single transistor. For every library cell the number of transistors used is available, thus calculating the total area estimate is simply a summing operation.

Obviously, the area due to interconnect is not accounted for. Moreover, ideal placement is assumed, i.e., gaps between cells are not taken into account. Therefore, the transistor count estimate gives a lower bound of the total area.

If a net list is not available, a synthesis step can be made to obtain a preliminary estimate. Depending on the complexity of the design this synthesis can be expensive in terms of computation time. Therefore, for quick iterations when exploring the design space, this approach is not very attractive.

#### Complexity-based area estimation

With complexity-based estimation techniques, it is assumed that the area needed to implement a certain boolean function depends on its area complexity, i.e., it is assumed that the area complexity of a boolean function corresponds to the minimum number of gates required to implement the function and thus can serve as a valid estimate of the gate count. Different measures and approaches exist to express the area complexity in terms of known properties of the function to be implemented. Of course, once the area for the combinatorial part of a design has been estimated, the area needed for the registers and other memory elements should also be accounted for.

In [16] the authors use the number of literals L(f) of a boolean function f as an area complexity measure. An exponential relation with the function's entropy is found via the so-called *computational work* of a function. The computational work is a measure for the computing power of a function.

$$L(f) \propto W(f)$$

(2.1)

The computational work W(f) of an *n*-input combinatorial function f with m outputs is given by [27]

$$W(f) = 2^n H(f). (2.2)$$

Here, H(f) is the entropy of the function and it is defined as

$$H(f) = \sum_{i=1}^{2^m} P_i \log_2 \frac{1}{P_i}.$$

(2.3)

where  $P_i$  is the probability of the  $i^{th}$  output vector  $y_i$ , given by

$$P_i = \frac{n_{y_i}}{2^n} \tag{2.4}$$

with  $n_{y_i}$  the number of input vectors that have  $y_i$  as result.

The authors show that this model is suitable for estimating the area for randomly generated functions. However, it is argued in [48] that this measure for the area complexity does not hold for typical VLSI circuits. Therefore, the authors suggest an extension to the model. They argue that the model should be extended by adding information about the structure of the boolean space of the function, to accommodate typical VLSI circuits.

In order to capture the characteristic structure of a boolean function, the authors introduce the so-called *linear measure* L(f) for a single-output boolean function f. It is defined as

$$L(f) = L_{\text{on}}(f) + L_{\text{off}}(f). \tag{2.5}$$

Here,  $L_{\text{on}}(f)$  and  $L_{\text{off}}(f)$  represent the linear measure of the on-set and off-set of the function f, respectively.

The linear measure for the on-set<sup>1</sup> of an n-input, single-output boolean function f is calculated as the weighted sum of the distinct sizes of the prime implicants in a minimal cover of the on-set [44] of f

$$L_{\rm on}(f) = \sum_{i=1}^{N} c_i \cdot p_i. \tag{2.6}$$

Here, N is the number of distinct sizes of prime implicants in the cover,  $\{c_i\}$  is the ordered set of distinct sizes of these implicants for i = 1...N such that  $c_1 < c_2 < ... < c_N$ , and  $p_i$  is the weight factor on the prime implicants of size  $c_i$ .

The weighing factors are defined as follows

$$p_i = \begin{cases} P(f_i) - P(f_{i-1}), & \text{if } i > 1, \\ P(f_i), & \text{if } i = 1, \end{cases}$$

(2.7)

where  $P(f_i)$  is the probability that  $f_i = 1$ , assuming an equal probability for all points in the boolean space of  $f_i$ . Sub-function  $f_i$  of the original function f is defined such that its on-set solely consists of the prime implicants of the on-set of f with sizes  $c_1, c_2, \ldots c_i$ . With these definitions we get

$$\sum_{i=1}^{N} p_i = P(f). \tag{2.8}$$

<sup>&</sup>lt;sup>1</sup>The linear measure for the off-set is calculated similarly.

Thus  $P(f_i)$  is equivalent to the fraction of the boolean space of f covered by subfunction  $f_i$ .

In order to estimate the area of a boolean function, the authors use almost-exponential relations to translate the linear complexity measure into an area estimate. These relations are derived by randomly generating boolean functions for different entropies H(f), calculating the linear measure, and finally measuring the gate count after synthesis.

In order to apply this technique to multi-output boolean functions, a multi-output function is transformed into an equivalent single-output function. The transformation boils down to adding a multiplexer to the circuit and calculating the linear measure for the result. Finally the additional area of the multiplexer is compensated for.

#### Rent's rule

An empirical method to predict the area of a circuit is based on the observation made by Rent that the average number of terminals T per module is exponentially dependent on the number of gates G used by the module [40]

$$T = t \cdot G^p. \tag{2.9}$$

Here, the Rent coefficient t is interpreted as the average number of terminals required by a single gate and p is known as the Rent exponent. This relationship is commonly known as Rent's rule.

Conversely, the area can be expressed in the number of pins T

$$G = \left(\frac{T}{t}\right)^{\frac{1}{p}}. (2.10)$$

Thus, if the technology and design parameters t and p are known, an estimate of the area can be made based on the number of pins of the circuit.

If the Rent coefficient and exponent are not known beforehand, they have to be estimated. As Rent's rule is an exponential relationship, an error in the prediction of the Rent exponent can have large impact on quantities derived using Rent's rule. It is important to note that the Rent coefficient and exponent cannot be regarded as independent variables [17].

Current methods to determine the Rent coefficient and exponent are based on two approaches. The first is to use statistical estimates from previous designs that are similar (various estimates can be found in literature [5]). The second is to estimate the parameters from the properties of the net list. This again requires a synthesis step. However, because of the self-similarity within the design, the same properties apply throughout the whole design. Therefore, only small sub-circuits have to be synthesized to obtain a representative net list.

#### 2.2.2 Interconnect estimation

The estimation of interconnect characteristics is important as it influences the three main design constraints directly.

- Area: Obviously, the wires have to be placed somewhere on the chip. Especially structures like busses require a large area.

- Delay: The propagation delay is directly dependent on the length of the wires (see also section 2.3.1).

- *Power:* The parasitic capacitance and resistance of the wires are dependent on the length of the wires, thus longer wires require more energy to transport a signal value.

Estimation methods can be divided into a priori and a posteriori methods. As a posteriori techniques usually require a full placement step, this method is not feasible for quick iterations. Therefore, in the remainder of this section we will focus on a priori estimation methods only.

An a priori estimation technique for interconnects is the method introduced by Donath [19]. The author recursively applies Rent's rule to come up with estimates for the average lengths  $\bar{l}_k$  and the expected number of interconnections  $\bar{n}_k$  at each level k of the design hierarchy. Using these, the average length  $\bar{L}$  of the interconnect is calculated

$$\overline{L} = \frac{\sum_{k=0}^{K-1} \overline{n}_k \overline{l}_k}{\sum_{k=0}^{K-1} \overline{n}_k},$$

(2.11)

where K is the top level in the hierarchy. Now, with

$$\overline{n}_k = \alpha C 4^K (1 - 4^{p-1}) 4^{k(p-1)},$$

(2.12)

where C is the total number of gates in the design and p the Rent exponent, and with

$$\bar{l}_k = \frac{2}{9} \left( 7\lambda - \frac{1}{\lambda} \right), \tag{2.13}$$

where  $\lambda = 2^k$ , we have all the information we need to calculate the average interconnection length  $\overline{L}$ . As the width the minimum separation distance of the wiring is usually known, the interconnect area can easily be calculated.

In [77] Donath's model is refined to accommodate additional placement information. It is assumed that an optimal placement procedure will preferably place gates that are interconnected close together. This results in a lower estimate of the lengths of the interconnections. Therefore, Donath's model can be used as an upper bound estimate, whereas the refined model gives more accurate predictions.

## 2.3 Delay estimation

In many systems to be designed, timing is a critical design constraint. This is especially true for real-time systems, i.e., systems that should generate a response within a specified maximum delay after applying a stimulus. In the remaining systems the temporal behavior may not be critical, but it still is an important performance measure. Therefore delay estimation is a crucial aspect of a design trajectory.

In this section we focus on delay estimation of synchronous circuits. The delay or execution time of a synchronous circuit can be expressed by two figures of merit, namely the *cycle time* and the *latency* of the circuit. The cycle time is the period of the fastest clock that can be applied to the circuit, without introducing errors. The latency is the time required to execute operations, expressed in terms of clock cycles. Herewith the product of cycle time and latency gives the overall execution delay of the circuit.

Delay estimation techniques can be subdivided into two main categories: delay estimation for individual resources, and system delay estimation. The methods in the first category try to estimate the delay of relatively small building blocks. Techniques in the second category use these results to estimate the delay of a complete system consisting of several of these building blocks.

#### 2.3.1 Resource delay estimation

Various methods exist for estimating the delay of individual resources. They are based on different principles.

- Measurement: An evident way to obtain a delay estimate is to measure the timing characteristic of a circuit once it has been built. Though accurate, the method is only applicable for relatively small designs, because of the time needed to physically build the circuit and because of the associated costs.

- Calculus: A second method to estimate the delay of a circuit is to calculate the waveforms on all nodes of the circuit either analytically or numerically. These waveforms are then used to calculate the timing behavior of the circuit. The applicability of this method is heavily influenced by the level of detail required. For instance, in a synchronous circuit, the exact calculation of the minimum cycle time is more difficult than the calculation of the latency of a circuit once the cycle time is known.

- Simulation: Simulation-based methods are used at different levels of detail for delay estimation. The underlying models determine the accuracy of the estimation, and range from detailed transistor models to behavioral gate models.

All three methods assume that the implementation of the resource is already known. Thus a net list or a layout specification of the resource must be available. Of course, for measuring the delay of circuit, the circuit has to be realized already.

Calculus and simulation-based methods require knowledge and subsequent modeling of the delay mechanisms. In digital synchronous circuits, two sources of delay can be identified: gate delay, and propagation delay. The former is the time it takes a gate to switch from one level to another. The latter is the time needed to transport a signal over a certain distance on a chip. Each of these is discussed in more detail in the following paragraphs.

#### Gate delay

As CMOS FETs have a limited current driving capability, charging or discharging of the load capacitance of a gate causes some delay larger than zero. In this section a lower bound for this delay is presented.

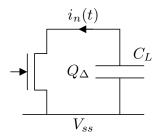

We consider a charged load capacitance which is discharged by a conducting NMOS transistor (see figure 2.1). The amount of electrical charge  $Q_{\Delta}$  that has accumulated on the capacitor equals

$$Q_{\Delta} = C_L \cdot V_{\Delta},\tag{2.14}$$

where  $C_L$  is the load capacitance and  $V_{\Delta}$  is the voltage swing.

Figure 2.1: Discharging a load capacitance through an NMOS transistor.

The total charge transported through the transistor is given by the integral of the transistor current  $i_n(t)$ . If the capacitor is to be fully discharged, this value should be equal to the accumulated charge  $Q_{\Delta}$

$$Q_{\Delta} = \int_{\tau_0}^{\tau_1} i_n(t) \ dt. \tag{2.15}$$

To calculate a lower bound on the delay of the gate, we assume that the transistor conducts the maximum current given by the saturation current  $I_{Dsat}$ . Then substituting  $I_{Dsat}$  for  $i_n(t)$  in equation 2.15 gives

$$Q_{\Delta} = \int_{\tau_0}^{\tau_1} I_{D_{\text{sat}}} dt = (\tau_1 - \tau_0) \cdot I_{D_{\text{sat}}}.$$

(2.16)

Substitution of equation 2.14 gives the lower bound of the delay  $\tau_{\Delta} = \tau_1 - \tau_0$

$$\tau_{\Delta} = \frac{C_L \cdot V_{\Delta}}{I_{Dest}}.\tag{2.17}$$

To further explore the delay bound, we need an expression to calculate the saturation current. A widely used transistor model is the long-channel approximation. In this model the saturation current has a quadratic relation with the gate voltage.

However, the long-channel approximation fails to accurately model recent short-channel FETs, primarily because it does not incorporate carrier velocity saturation effects. To overcome the shortcomings of this model, an alpha-power law model has been developed [71] which models the velocity saturation effects by a velocity saturation index  $\alpha$ . The value of the index varies from 2 for long-channel transistors to ultimately 1 (linear relation) when the speed of the carriers is always at saturation speed.

In the alpha-power law model the saturation current has the following relation with the gate voltage  $V_G$

$$I_{D_{\text{sat}}} = \beta \left( V_G - V_T \right)^{\alpha}, \tag{2.18}$$

where  $V_T$  is the threshold voltage of the transistor and  $\beta$  a transistor-dependent parameter.

Substitution of equation 2.18 in equation 2.17 gives

$$\tau_{\Delta} = \frac{C_L \cdot V_{\Delta}}{\beta \left(V_G - V_T\right)^{\alpha}} \approx \frac{C_L}{\beta \cdot \gamma^{\alpha} V_{dd}^{\alpha - 1}}.$$

(2.19)

Here we used  $V_{\Delta} \approx V_{dd}$  and  $V_G - V_T \approx \gamma V_{dd}$ . Thus the gate delay is inversely proportional with the supply voltage

$$\tau_{\Delta} \propto \frac{1}{V_{dd}^{\alpha - 1}}.\tag{2.20}$$

Apparently the gate delay can be lowered by increasing the supply voltage, i.e., by increasing the driving power. However this has a serious impact on the power consumption of a circuit (see section 2.4.3).

#### Propagation delay

With ever decreasing feature sizes and ever higher switching speeds, the propagation delay becomes more and more important. To model an interconnect, resistance-capacitance (RC) trees are commonly used. A popular and widely used RC delay metric is the Elmore delay [21] because of its simple closed-form expression. However, the Elmore delay metric is derived for point-to-point connections, and lacks consistent accuracy for RC trees, especially at the near end, because it ignores resistive shielding.

It has been shown that the Elmore delay corresponds to the first moment of the impulse response of an RC tree [70]. A natural step is to include higher-order moments to increase the accuracy. A simple and accurate metric is the so-called D2M metric [4]. It is an empirical metric based on the first two moments of the impulse response of the RC tree.

Given an RC tree with nodes  $\{v_0, \ldots, v_N\}$ , where  $v_0$  is the source of the tree, let  $C_i$  be the capacitance at node  $v_i$  for  $0 < i \le N$ . If  $p(v_i)$  is the predecessor of node  $v_i$  then  $R_i$  is defined as the resistance between nodes  $p(v_i)$  and  $v_i$ . Now define  $R_{ki}$  as the total resistance of the portion of the path from  $v_0$  to  $v_i$  that overlaps with the path from  $v_0$  to  $v_k$ .

For  $j \geq 1$ , the  $j^{\text{th}}$  moment  $m_j^i$  of the impulse response for node  $v_i$  is recursively expressed as

$$m_j^i = -\sum_{k=1}^N R_{ki} C_k m_{j-1}^k. (2.21)$$

For j = 0 we have  $m_0^i = 1$  for all nodes.

Now, the D2M delay metric is defined as

$$D_{D2M} = \frac{m_1^2}{\sqrt{m_2}} \ln 2. \tag{2.22}$$

Here,  $m_j$  denotes the  $j^{\text{th}}$  moment for a generic node.

#### 2.3.2 System level delay estimation

As soon as the cycle time and latencies of the resources have been estimated, an estimate can be made of the delay of a system composed of those resources. In most cases the execution order of the resources is not yet known and therefore a schedule has to be made.

Apart from the resource characteristics, the following aspects of the system should be taken into account while defining a schedule.

- Data storage: In synchronous circuits, data should be stored in some form of memory when it has to go from one functional resource to another.

- Wiring: To transport data from one resource to another, wires are needed. Naturally these cause some delay.

- Steering logic: To properly guide the data from one resource to another some steering logic is needed. Usually it consists of some form of multiplexers.

- Control unit: In order to control the resources and the data transports, one needs a control unit. Depending on the type of circuit (data or control-dominated) this unit may significantly contribute to the total delay of the system.

In this thesis we consider data-dominated systems, i.e., we assume that the control part of the system can be neglected with respect to the data part.

Once the schedule is known, the latency of the circuit is known. Additionally, if the cycle time is known, an estimate is available for the total delay of a system. Of course different scheduling strategies evoke different delays. The scheduling problem can be formulated as follows. Given a set of tasks and resources, we have to find an ordering of tasks and assignment to resources while satisfying given constraints. Different constraints can be applied separately or simultaneously. Constraints can be anything ranging from minimizing total latency, restricting the number of resources, to hard deadlines for certain tasks. Depending on the constraints, different scheduling strategies are viable. Three scheduling strategies are covered in more detail in the next sections.

#### Unconstrained scheduling

In unconstrained scheduling we want to find the minimum latency schedule. There are no constraints, neither on the number of resources, nor on time limits to be met. Unconstrained minimum latency scheduling can be solved in polynomial time by applying the ASAP (as soon as possible) scheduling algorithm.

#### Time-constrained scheduling

In time-constrained scheduling only time constraints are set. The number of resources is not limited. Time-constrained scheduling comes in two flavors: latency-constrained scheduling, and scheduling under timing constraints. Also a combination of the two is possible.

In latency-constrained scheduling a global maximum latency constraint is specified. This scheduling problem can be solved by running the ASAP algorithm and by verifying that its solution meets the latency constraint.

When scheduling under timing constraints, one can specify additional constraints for the individual resources. These timing constraints can be either absolute or relative. Scheduling under absolute timing constraints can be solved using the Bellman-Ford algorithm.

#### Resource-constrained scheduling

Resource-constrained scheduling arises from resource-limited circuits, typically incurred by constraints on the total chip area. The number of resources necessary to implement a circuit largely determines the area used by the circuit. Therefore resource-constrained scheduling can be used to find latency vs. area trade-offs.

Resource-constrained scheduling is intractable. However, several exact algorithms and heuristics exist to come up with a, possibly approximate, solution in reasonable time. These include integer linear programming algorithms, list scheduling and force directed scheduling.

## 2.4 Power estimation

In order to properly design for low power, one needs feedback in the form of power estimation techniques. Several power estimation techniques exist for VLSI and can

be applied at different levels in the design flow. The following criteria should be taken into account when comparing estimation techniques.

- Efficiency: The efficiency of a power estimator indicates whether the estimator can deal with large circuits in reasonable time. Especially at the beginning of the design of a system, feedback must be provided quickly, to aid early exploration of the design space.

- Accuracy: The accuracy of a power estimator is determined by the difference between the estimated and the actual (after implementation) power usage. If absolute accuracy is not required, the estimator should at least properly estimate the relative power consumption of design alternatives.

- Uncertainty: Especially in an early stage of the design trajectory, not everything is yet known about the design and its implementation. Therefore a power estimator should be able to cope with these uncertainties and unknowns.

Together these three criteria determine the effectiveness of a power estimator in a particular stage of the design trajectory.

A number of approaches is available to estimate the power consumption of a design [15, 38, 48, 63].

- Measurement: An obvious method to estimate the power usage of a circuit is to build it and to measure the current drawn from the power supply. However this technique is not applicable for other designs than very small ones, as building larger designs rapidly becomes too time consuming and too expensive.

- Calculus: A straightforward way to estimate the power dissipation of a circuit is to calculate all currents and voltages of dissipating elements, either analytically or numerically. The product of these gives the instantaneous power of all these elements. Finally summing the intermediates gives the power consumption of the whole circuit.

- Calculating the exact power consumption is only feasible for relatively small circuits. For larger circuits it is extremely complex, and for some circuits even not possible to find analytical expressions of the currents and voltages and numerical calculation is usually too time consuming.

- Probabilistic methods: If the probabilities of the input signals of a network are known, the probabilities of all signals on all nodes of the network can be calculated. Using these probabilities, activity levels can be estimated and based on these the power usage of the network can be estimated with a charged capacitance model [69].

A drawback of this method is that the inputs must be independent. If they are not, calculating the signal probabilities becomes very complex.

- Statistical methods: Another approach similar to the probabilistic methods is to apply a large number of random inputs to the circuit and to statistically find the activities of the nodes. Again a switched capacitance model can be used to estimate the power usage of the circuit.

- Simulation-based methods: Finally, a large category of power estimators is based on simulation. These simulate a design and use some power model for its components to estimate the power consumption. Simulation techniques can be applied at various levels; they range from methods using detailed transistor models to techniques estimating the power usage of large sub-systems such as full-blown Fourier transforms.

Except for the technique of direct measurement of the power consumption, all techniques rely on models of the power dissipation in an IC. To get a better understanding of power dissipation in CMOS circuits, we take a look at its origins. Power dissipation in CMOS ICs can be divided into two main categories [61]: static power dissipation, and dynamic power dissipation. Both categories will be discussed shortly.

Moreover, several of these methods are based on estimating the activity of the internal signal nodes of the network. Therefore activity-based power estimation will be discussed in more detail in section 2.4.3.

### 2.4.1 Static power dissipation

Assuming ideal transistors, a CMOS circuit does not dissipate any power when it is not switching. However, this is not a realistic assumption: a certain amount of power is always lost due to a number of mechanisms such as leakage currents and substrate injection currents. These currents cause a static power dissipation component in CMOS circuits.

Static power dissipation can be minimized by choosing a proper technology. Once the designer has chosen one, there is little else he can do to influence this type of power dissipation. Therefore we will focus on dynamic power dissipation.

## 2.4.2 Dynamic power dissipation

For CMOS circuits, the dynamic power dissipation can be subdivided into two types.

- Short-circuit current: During a switching transient, for a short time, both the NMOS pull-down network and the PMOS pull-up network of the gate will conduct simultaneously. In this time a short circuit is formed between the voltage supply and ground, resulting in a power loss. This loss can be minimized by carefully designing the devices and the gates.

- Capacitance charging: Every time switching occurs, parasitic capacitances are either charged or discharged. The discharging process does not draw any

current from the power supply. However, for the charging of the capacitors energy is needed, which is drawn from the power supply. Hence, power is dissipated when capacitances are charged. The amount of dissipated power depends on the size of the parasitic capacitances and the voltage swing.

Capacitance charging is the dominating factor in power dissipation in CMOS circuits. Furthermore, at the high level of design we are concerned with, we have little influence (except from choosing a proper technology) on the short circuit currents of individual transistors. Therefore, in the remaining parts of this section, we will focus on power dissipation due to capacitance charging.

### 2.4.3 Activity-based power estimation

Activity-based power estimation is founded on the assumption that dynamic power dissipation is the dominating factor in the total power dissipation of a circuit. Therefore it estimates the amount of capacitance being charged every time a node in the network switches. The energy needed to charge these capacitances gives an estimate of the dissipation in the circuit.

#### Capacitance charging

The amount of capacitance charged during a transition must be translated into a power figure. Therefore we calculate the energy dissipation due to the charging of capacitances in complementary MOS gates.

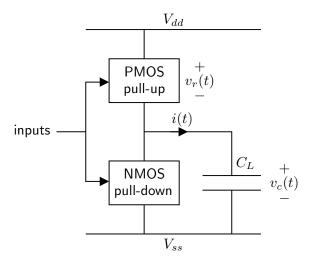

Figure 2.2: Capacitance (dis)charging in CMOS gates.

The current through the capacitive load  $i_c(t)$  of a CMOS gate is given by (see figure 2.2)

$$i(t) = C_L \frac{dv_c(t)}{dt},\tag{2.23}$$

where  $v_c(t)$  is the voltage over the load capacitor and  $C_L$  the load capacitance.<sup>2</sup>

Switching from a low level at time  $\tau_0$  to a high level at  $\tau_1$  results in charging the load capacitance with energy  $E_C$

$$E_C = \int_{\tau_0}^{\tau_1} i(t)v_c(t)dt.$$

(2.24)

Then substitution of equation 2.23 gives

$$E_C = C_L \int_{\tau_0}^{\tau_1} \frac{dv_c(t)}{dt} v_c(t) dt$$

$$= \frac{1}{2} C_L \left( v_c(\tau_1)^2 - v_c(\tau_0)^2 \right).$$

(2.25)

The energy stored in the load capacitance is lost at the consecutive discharging (switching from high to low) of the gate.

In addition to the energy used to charge the capacitive load, the PMOS circuit dissipates energy  $E_R$  in the form of heat

$$E_R = \int_{\tau_0}^{\tau_1} i(t) v_r(t) dt,$$

where  $v_r(t)$  is the voltage drop over the PMOS circuit. Substituting equation 2.23 and using  $v_r(t) = V_{dd} - v_c(t)$  leads to

$$E_R = \int_{\tau_0}^{\tau_1} i(t) \left( V_{dd} - v_c(t) \right) dt$$

$$= C_L V_{dd} \left( v_c(\tau_1) - v_c(\tau_0) \right) - \frac{1}{2} C_L \left( v_c(\tau_1)^2 - v_c(\tau_0)^2 \right).$$

(2.26)

Using equation 2.25 and 2.26, we obtain the total energy E lost during a low to high transition, given by

$$E = E_C + E_R = C_L V_{dd} V_{\Delta}, \tag{2.27}$$

where the voltage swing  $V_{\Delta}$  of the gate is given by

$$V_{\Delta} = v_c(\tau_1) - v_c(\tau_0). \tag{2.28}$$

Assuming the voltage swing approximately equals the supply voltage,  $V_{\Delta} \approx V_{dd}$ , leads to

$$E \approx C_L V_{dd}^2. \tag{2.29}$$

It is important to note that in this approximation the dissipated energy only depends on the capacitive load and the supply voltage. Gate-specific and transistor-specific parameters such as the channel width or length of a FET do not influence the energy dissipation.

If we use the exact equation 2.27 instead, gate and device parameters do influence the energy dissipation as they determine the voltage swing  $V_{\Delta}$  of the gate.

<sup>&</sup>lt;sup>2</sup>The load capacitance  $C_L$  is assumed to be independent of the load voltage  $v_c(t)$ .

#### Load capacitance

To estimate the load capacitance  $C_L$  of a gate we use the following model. If an output of a gate switches from a low to a high level, several capacitances have to be charged, namely:

- the output capacitance of the gate,

- the input capacitances of the connected gates, and

- the wire capacitances of the interconnect.

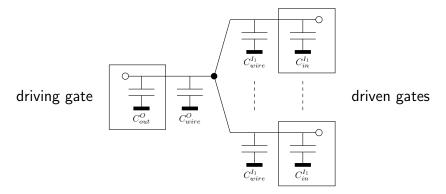

An example is shown in figure 2.3.

Figure 2.3: Example of the switched capacitance model.

The total capacitance  $C_L$  charged by the gate is given by

$$C_L = C_{out}^O + C_{wire} + C_{in},$$

(2.30)

where  $C_{out}^O$  is the output capacitance of the driving gate,  $C_{wire}$  the capacitance due to the interconnect and  $C_{in}$  the total input capacitance of the gates being driven.

The interconnect capacitance is modeled by an output wire capacitance  $C_{wire}^{O}$  and several input wire capacitances  $C_{wire}^{I_i}$ . The total wire capacitance is given by

$$C_{wire} = C_{wire}^{O} + \sum_{i=1}^{N} C_{wire}^{I_i}.$$

(2.31)

The input capacitance of the gates being driven is given by the sum of the input capacitances of every gate  $C_{in}^{I_i}$ . Then the total input capacitance is

$$C_{in} = \sum_{i=1}^{N} C_{in}^{I_i}.$$

(2.32)

Substituting equation 2.31 and 2.32 into equation 2.30 leads to

$$C_L = C_{out}^O + C_{wire}^O + \sum_{i=1}^N \left( C_{wire}^{I_i} + C_{in}^{I_i} \right). \tag{2.33}$$

Here the total switched capacitance is clearly divided into capacitances related to either the driving or the driven side. Therefore the total switched capacitance of a circuit can be calculated by summing the switched input, output and wire capacitances per gate.

#### Circuit level power estimation

The total energy dissipated in a large integrated circuit is calculated using

$$E = \sum_{i=1}^{N} a_i C_{Li} V_{dd}^2 \tag{2.34}$$

where N is the number of nodes in the circuit,  $a_i$  the number of times the  $i^{\text{th}}$  node switches from a low to a high level, and  $C_{Li}$  is the load capacitance of node i.

The load capacitance is approximated by the average load capacitance given by

$$C_{Li} \approx \overline{C}_L = \frac{C}{N} \tag{2.35}$$

where C represents the total capacitance. Substituting equation 2.35 in 2.34 gives

$$E \approx \frac{1}{N} \sum_{i=1}^{N} a_i C V_{dd}^2 = \alpha C V_{dd}^2.$$

(2.36)

Here  $\alpha$  is the average switching activity of the circuit

$$\alpha = \frac{1}{N} \sum_{i=1}^{N} a_i.$$

(2.37)

It should be noted that equation 2.36 is a rough estimate of the total energy used by the circuit, based on global averages.

## 2.4.4 System level power estimation

A major obstacle in estimating the energy or power consumption at a high level is that in general detailed structural information of the design is still lacking. This kind of information is usually only available after scheduling, and the final net list only after a full synthesis step. Although they are more accurate, it takes too much time to compute these estimates so they cannot be used for a quick estimate in an iterative process.

If however, a design is constructed using fixed sub-circuits, the time needed to estimate the cost figures of a sub-circuit once may be acceptable with respect to the overall design time. If the sub-circuits have been used in a previous design, these numbers might even be available beforehand.

Nevertheless, if only the functional description is available, simulation is currently the most obvious way to quickly estimate the power consumption of a design. It typically involves estimating the average activity  $\alpha$  and the capacitive load C of the circuit.

## 2.5 Area, delay, power trade-offs

Obviously, the area, delay and power of a circuit are strongly interdependent. As a result, design constraints are often in conflict and trade-offs have to be made. Of course, trade-offs can be made between every combination of two or more constraints. This results in four possible trade-off combinations:

- area delay,

- delay power,

- power area, and

- area delay power.

The third option, power versus area, is usually considered the least interesting and also mostly covered in the last combination. Therefore only the other three are discussed in the next sections.

## 2.5.1 Area versus delay

For many years area and delay were the primary cost and performance measures of a design. With the recent rise of power usage as an important design issue, the focus has moved a little. However, trade-offs between area and delay are still of prime importance in most designs.

This section starts with a discussion on circuit techniques. Here a circuit is assumed to be given and techniques are discussed to exchange area for delay and vice versa. This pragmatic approach leads to the more fundamental question of what these techniques can achieve theoretically. Thus, in the remainder of this section some theoretical bounds on area and time (delay), the so-called AT bounds, are discussed.

#### Circuit techniques

Circuit techniques are used to modify the area and delay of a given circuit, without changing the circuit behavior. Two alternatives are discussed: re-timing and pipelining.

**Re-timing** A synchronous network can be modified by shifting, adding or deleting registers. This process is called re-timing. The logical behavior of the circuit does not change during or after re-timing.

Re-timing can be applied to achieve different optimization goals.

- Cycle time minimization: In cycle time minimization the delay of the longest path (not interrupted by registers) in the circuit is reduced. This is done by shifting the registers such that the longest path is shortened or replaced by another path, hereby reducing the path delay. Thus after re-timing it is possible to reduce the cycle time to match the newly found longest path delay.

- Area minimization: As adding or removing registers respectively increases or decreases the area of the circuit, re-timing can also be used to minimize the area.

Obviously, cycle time and area minimization are not independent. Thus, joint optimization requires another approach. Besides re-timing, combined area and delay optimization requires combinatorial optimization. In this scheme, combinatorial optimization is used to remove combinatorial bottlenecks in the circuit. Afterwards re-timing is applied to meet the cycle time requirements.

**Pipelining** Pipelining is a technique used to increase the throughput of a circuit. Throughput is defined as the number of data samples processed per clock cycle. Strictly speaking, pipelining does not reduce the delay of a circuit. However, given an increased throughput after pipelining, the cycle time of the circuit can be lowered to get the same overall processing rate (data samples per time unit).

Of course, pipelining is not for free and usually increases the area of the circuit because of the extra registers and control logic needed.

#### Area-time (AT) bounds

Given a certain implementation of an algorithm, the area and the execution delay are known. When another implementation is used with a different area and delay, the question arises how the area and delay of the first implementation relate to the second and vice versa.

Lower bound arguments for three different relations are summarized in [81]. These are based on three different observations regarding the information processing capabilities of a circuit with a certain area A and a certain execution delay T.

• *Memory limited:* A circuit can only remember a limited number of bits from one time step to the next. This number of bits is proportional to the area. Therefore,

$$A = constant. (2.38)$$

Another interpretation of this rule is that the area of the registers in the data path of a circuit does not depend on the delay of the circuit. • IO limited: A circuit can only process and generate a limited number of inputs and outputs. This number is proportional to the product of the area and the delay. Thus,

$$AT = constant.$$

(2.39)

For instance to read n input ports, one needs n input terminals for a single time unit, or only one input port for n time units.

• Information exchange limited: The amount of information that can flow from one part of the area to the other in a single time unit is limited to the square root of the area. Thus the total information flow is limited to the product of the square root of the area and the delay. Hence,

$$AT^2 = constant. (2.40)$$

An equivalent interpretation is that the number of interconnections (wires) is limited to the square root of the area (i.e. the largest possible value for the shortest side of a rectangular area).

It is assumed that the circuits considered contain a large number of operations. Furthermore it is assumed that numerous alternative implementations can be found.

In [55] these bounds were experimentally verified. It appeared that the first two bounds can be used as good approximations. The third, however, was not validated. Still, it was noted that almost all experiments showed the following relationship

$$AT^r = constant, (2.41)$$

where r varied between 1.2 and 1.5.

## 2.5.2 Delay versus power

The average power used by the circuit is defined by

$$P = \frac{E}{T},\tag{2.42}$$

where E is the total energy consumed by a circuit in T time. The total energy can be approximated by (see equation 2.36)

$$E = \alpha C V_{dd}^2, \tag{2.43}$$

where  $\alpha$  is a measure of the average switching activity of the circuit,  $C_{av}$  the average total switched capacitance, and  $V_{dd}$  the supply voltage. This expression is similar to equation 2.29, where the load capacitance  $C_L$  is replaced by the total switched capacitance C.

Substitution of equation 2.43 in 2.42 gives

$$P = \alpha \frac{CV_{dd}^2}{T}. (2.44)$$

This expression clearly shows the dependence between the power usage, the supply voltage and the execution delay of the circuit.

Once a circuit is implemented, its power can be reduced by either increasing the execution delay or by decreasing the supply voltage. These methods are known as frequency and voltage scaling.

### Frequency scaling

Obviously, the power can be reduced by increasing the execution delay T. This corresponds in a synchronous circuit to decreasing the frequency f as  $f = \frac{1}{T}$ . Substitution in equation 2.44 leads to the relation

$$P \propto f.$$

(2.45)

Thus, the power linearly depends of the frequency and it can be reduced by decreasing the frequency.

### Voltage scaling

In frequency scaling, the power reduction is only linear in frequency. At first sight, a quadratic reduction can be achieved by scaling down the supply voltage of the circuit

$$P \propto V_{dd}^2. \tag{2.46}$$

However, when we lower the supply voltage, the gate delay increases (see equation 2.19). As a result, the power is even more reduced<sup>3</sup>, ultimately resulting in a cubic dependency on the supply voltage

$$P \propto V_{dd}^3. \tag{2.47}$$

It should be noted that the voltage cannot be reduced indefinitely, because when the supply voltage approaches the threshold voltages of the transistors, the robustness of the transistors against noise is severely lowered and proper circuit behavior is compromised.

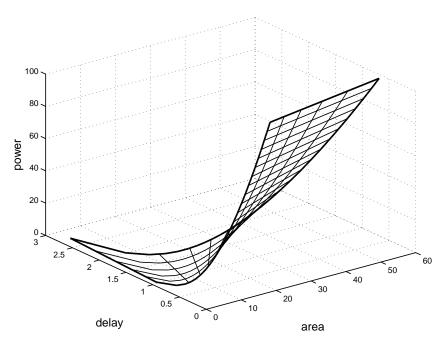

## 2.5.3 Area versus delay versus power

Above, power reduction techniques were discussed. These techniques are used for already implemented circuits and consequently the area is assumed to be fixed. If we release this restriction, the influence of the area on the capacitance and delay has also to be taken into account.

<sup>&</sup>lt;sup>3</sup>It is assumed that the circuit is running as fast as possible, i.e., the gate delay directly influences the delay of the circuit. If not, the quadratic dependency remains valid.

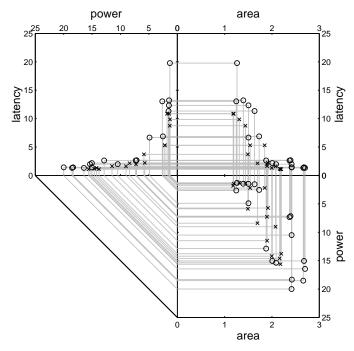

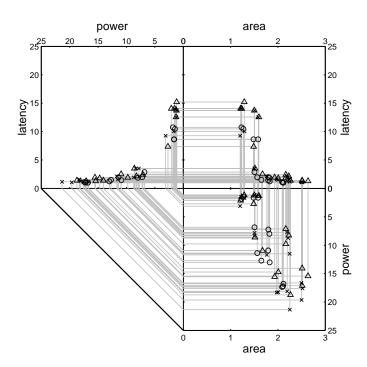

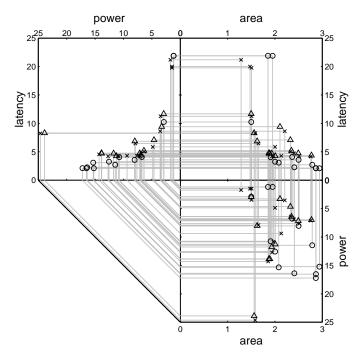

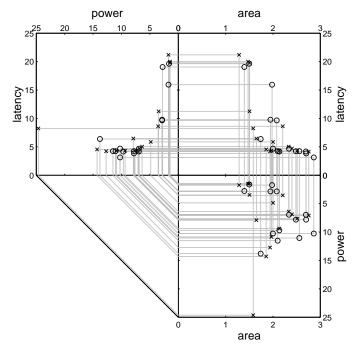

To relate area to delay, we use the lower bound specified in equation 2.40 in a slightly modified form

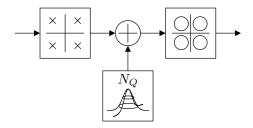

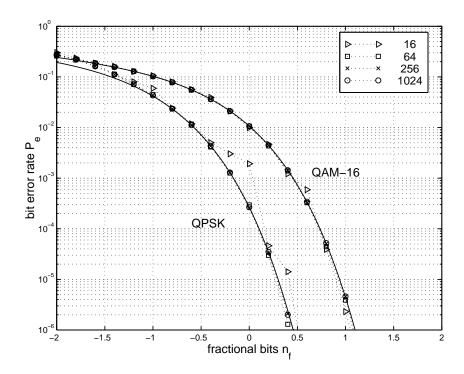

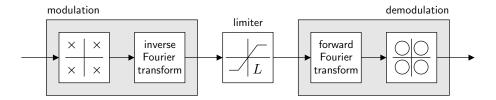

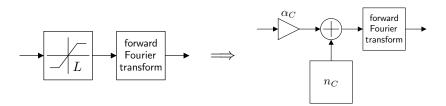

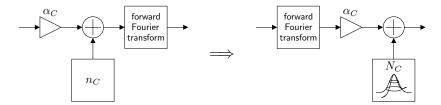

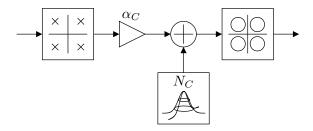

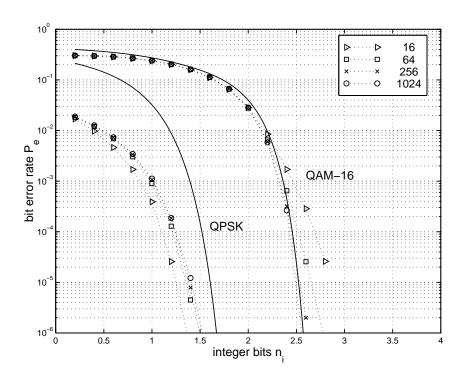

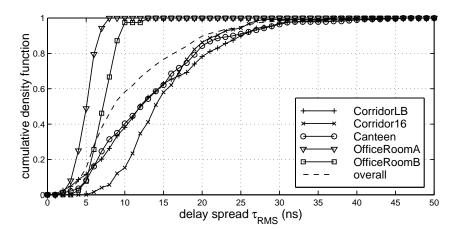

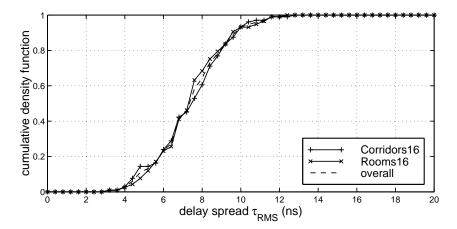

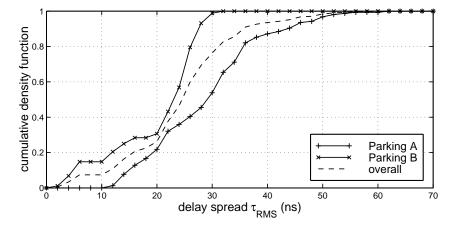

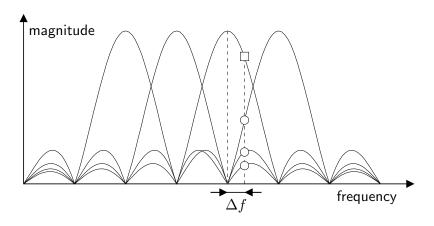

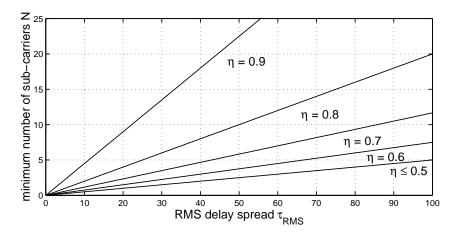

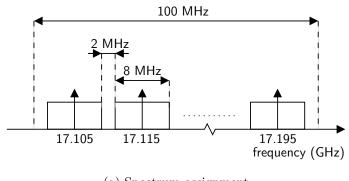

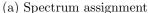

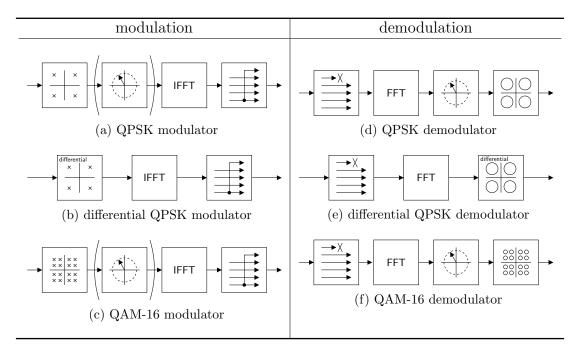

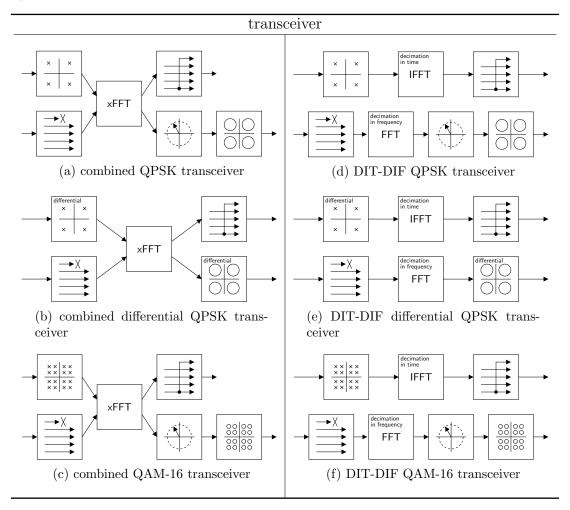

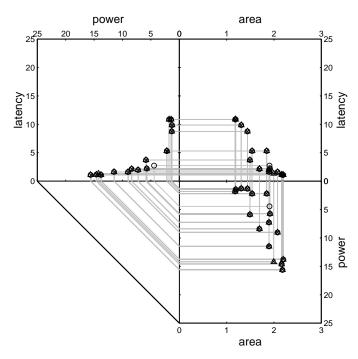

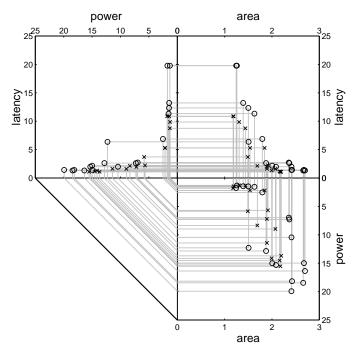

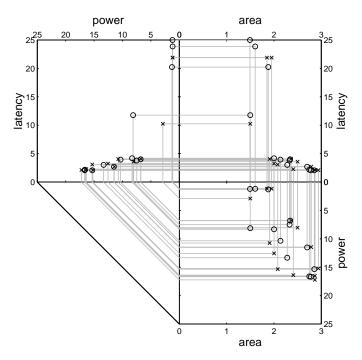

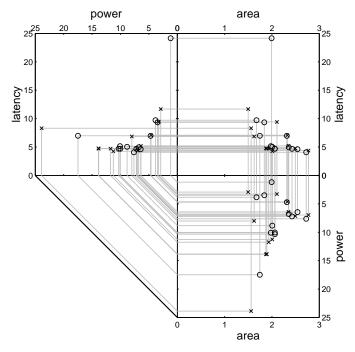

$$AT^r = \gamma, \tag{2.48}$$