# A first single-photon avalanche diode fabricated in standard SOI CMOS technology with a full characterization of the device

# Myung-Jae Lee,\* Pengfei Sun, and Edoardo Charbon

Faculty of Electrical Engineering, Delft University of Technology, Mekelweg 4, 2628 CD Delft, the Netherlands

\*M.J.Lee@tudelft.nl

**Abstract:** This paper reports on the first implementation of a single-photon avalanche diode (SPAD) in standard silicon on insulator (SOI) complementary metal-oxide-semiconductor (CMOS) technology. The SPAD is realized in a circular shape, and it is based on a P<sup>+</sup>/N-well junction along with a P-well guard-ring structure formed by lateral diffusion of two closely spaced N-well regions. The SPAD electric-field profile is analyzed by means of simulation to predict the breakdown voltage and the effectiveness of premature edge breakdown. Measurements confirm these predictions and also provide a complete characterization of the device, including current-voltage characteristics, dark count rate (DCR), photon detection probability (PDP), afterpulsing probability, and photon timing jitter. The SOI CMOS SPAD has a PDP above 25% at 490-nm wavelength and, thanks to built-in optical sensitivity enhancement mechanisms, it is as high as 7.7% at 850-nm wavelength. The DCR is 244 Hz/µm<sup>2</sup>, and the afterpulsing probability is less than 0.1% for a dead time longer than 200 ns. The SPAD exhibits a timing response without exponential tail and provides a remarkable timing jitter of 65 ps (FWHM). The new device is well suited to operate in backside illumination within complex three-dimensional (3D) integrated circuits, thus contributing to a great improvement of fill factor and jitter uniformity in large arrays.

©2015 Optical Society of America

OCIS codes: (040.1345) Avalanche photodiodes (APDs); (040.0040) Detectors; (130.3120) Integrated optics devices; (040.3780) Low light level; (280.4788) Optical sensing and sensors; (040.5160) Photodetectors; (230.5170) Photodiodes; (040.5250) Photomultipliers; (030.5260) Photon counting; (130.5990) Semiconductors; (130.6010) Sensors; (040.6040) Silicon; (050.6875) Three-dimensional fabrication.

# References and links

- A. Rochas, M. Gani, B. Furrer, P. A. Besse, R. S. Popovic, G. Ribordy, and N. Gisin, "Single photon detector fabricated in a complementary metal—oxide—semiconductor high-voltage technology," Rev. Sci. Instrum. 74(7), 3263–3270 (2003).

- A. Rochas, "Single photon avalanche diodes in CMOS technology," Ph.D. dissertation (École Polytechnique Fédérale de Lausanne, Lausanne, Switzerland, 2003).

- S. Mandai, M. W. Fishburn, Y. Maruyama, and E. Charbon, "A wide spectral range single-photon avalanche diode fabricated in an advanced 180 nm CMOS technology," Opt. Express 20(6), 5849–5857 (2012).

- 4. C. Veerappan and E. Charbon, "A substrate isolated CMOS SPAD enabling wide spectral response and low electrical crosstalk," IEEE J. Sel. Top. Quantum Electron. **20**(6), 299–305 (2014).

- F. Zappa and A. Tosi, "MiSPIA: Microelectronic single-photon 3D imaging arrays for low-light high-speed safety and security applications," Proc. SPIE 8727, 87270L (2013).

- 6. Y. Zou, D. Bronzi, F. Villa, and S. Weyers, "Backside illuminated wafer-to-wafer bonding single photon avalanche diode array," in *Conf. Ph.D. Research Microelectron. Electron.* (2014), pp. 1–4.

- 7. M.-J. Lee, H. Rücker, and W.-Y. Choi, "Effects of guard-ring structures on the performance of silicon avalanche photodetectors fabricated with standard CMOS technology," IEEE Electron Device Lett. **33**(1), 80–82 (2012).

- 8. G. F. D. Betta, Advances in Photodiodes (InTech, 2011), Chap. 11.

- 9. S. M. Sze and K. K. Ng, *Physics of Semiconductor Devices*, 3<sup>rd</sup> ed. (Wiley, 2007).

- M. Ghioni, G. Armellini, P. Maccagnani, I. Rech, M. K. Emsley, and M. S. Ünlü, "Resonant-cavity-enhanced single-photon avalanche diodes on reflecting silicon substrates," IEEE Photon. Technol. Lett. 20(6), 413

–415 (2008).

- 11. P. Sun, E. Charbon, and R. Ishihara, "A flexible ultra-thin-body single-photon avalanche diode with dual side illumination," IEEE J. Sel. Top. Quantum Electron. 20(6), 3804708 (2014).

- 12. M. W. Fishburn, "Fundamentals of CMOS single-photon avalanche diodes," Ph.D. dissertation (Delft Univ. of Technology, Delft, the Netherlands, 2012).

- 13. J.-Y. Wu, S.-C. Li, F.-Z. Hsu, and S.-D. Lin, "Two-dimensional mapping of photon counts in low-noise single-photon avalanche diodes," in *International Image Sensor Workshop* (2013).

- T. Leitner, A. Feiningstein, R. Turchetta, R. Coath, S. Chick, G. Visokolov, V. Savuskan, M. Javitt, L. Gal, I. Brouk, S. Bar-Lev, and Y. Nemirovsky, "Measurements and simulations of low dark count rate single photon avalanche diode device in a low voltage 180-nm CMOS image sensor technology," IEEE Trans. Electron. Dev. 60(6), 1982–1988 (2013).

- C. Niclass, M. Gersbach, R. Henderson, L. Grant, and E. Charbon, "A single photon avalanche diode implemented in 130-nm CMOS technology," IEEE J. Sel. Top. Quantum Electron. 13(4), 863–869 (2007).

- M. Gersbach, C. Niclass, E. Charbon, J. Richardson, R. Henderson, and L. Grant, "A single photon detector implemented in a 130nm CMOS imaging process," in *European Solid-State Device Research Conf.* (2008), pp. 270–273

- J. A. Richardson, L. A. Grant, and R. K. Henderson, "Low dark count single-photon avalanche diode structure compatible with standard nanometer scale CMOS technology," IEEE Photon. Technol. Lett. 21(14), 1020–1022 (2009).

- E. Charbon, H.-J. Yoon, and Y. Maruyama, "A geiger mode APD fabricated in standard 65nm CMOS technology," in *IEEE International Electron Devices Meeting* (2013).

- C. Niclass, M. Sergio, and E. Charbon, "A single photon avalanche diode array fabricated in 0.35μm CMOS and based on an event-driven readout for TCSPC experiments," Proc. SPIE 6372, 63720S (2006).

- D. Stoppa, D. Mosconi, L. Pancheri, and L. Gonzo, "Single-photon avalanche diode CMOS sensor for timeresolved fluorescence measurements," IEEE Sens. J. 9(9), 1084–1090 (2009).

- F. Villa, D. Bronzi, Y. Zou, C. Scarcella, G. Boso, S. Tisa, A. Tosi, F. Zappa, D. Durini, S. Weyers, U. Paschen, and W. Brockherde, "CMOS SPADs with up to 500 μm diameter and 55% detection efficiency at 420 nm," J. Mod. Opt. 61(2), 102–115 (2014).

- F. Zappa, M. Ghioni, S. Cova, L. Varisco, B. Sinnis, A. Morrison, and A. Mathewson, "Integrated array of avalanche photodiodes for single-photon counting," in *European Solid-State Device Research Conf.* (1997), pp. 600–603

- W. J. Kindt, H. W. van Zeijl, and S. Middelhoek, "Optical cross talk in geiger mode avalanche photodiode arrays: modeling, prevention and measurement," in *European Solid-State Device Research Conf.* (1998), pp. 192–195.

# 1. Introduction

Recently, silicon single-photon avalanche diodes (SPADs) based on standard complementary metal-oxide-semiconductor (CMOS) technology have received a great amount of attention by scientific and also industrial communities, because their compatibility with standard processes makes SPADs a cost-effectiveness solution to applications requiring photon-counting and photon-starved imaging. Examples of such applications include positron emission tomography (PET), single-photon emission computed tomography (SPECT), fluorescence-lifetime imaging microscopy (FLIM), fluorescence correlation spectroscopy (FCS), time-of-flight (TOF) three-dimensional (3D) imaging, etc. [1–5]. Due to the dynamic nature of single-photon detection, in situ processing is often a preferred solution, but the monolithic integration of SPADs and electronic circuits results in relatively low fill factor, which is the ratio of photon-sensitive area to total area in an image sensor.

In order to increase fill factor, there has been growing interest in backside-illumination (BSI) SPADs, possibly involving 3D integration schemes [5, 6]. BSI solutions may greatly increase fill factor and pixel density and consequently enable much better photon statistics and higher quality imaging. In general, however, CMOS-compatible SPADs have been implemented using a bulk silicon wafer, which makes it difficult to realize the BSI SPADs for the 3D-integration scheme without modifying the fabrication process. On the other hand, implementation of SPADs using standard silicon on insulator (SOI) CMOS technology can be an attractive solution, because the buried oxide (BOX) layer in the SOI wafer can be easily used as an etching stop during the wafer backside etching process. However, to the best of our knowledge, no SPAD has yet to be demonstrated in a standard deep-submicron SOI CMOS

technology. Recently, Zou *et al.* has reported a SPAD fabricated in 0.35-µm SOI CMOS technology for a wafer-to-wafer bonding 3D structure, but only dark count rate (DCR) and current-voltage characteristics of the SPAD were reported without any further characterization [6].

In this paper, we present the first SPAD fabricated in standard deep-submicron SOI CMOS technology complete of a full characterization of the device. The fabricated SPAD has a photon detection probability (PDP) of 25.4% at 490-nm wavelength with PDP enhancement at around 800-nm wavelength. The DCR is 244 Hz/ $\mu$ m<sup>2</sup>, afterpulsing probability is less than 0.1% with a 200-ns dead time, and timing jitter is a record 65 ps at room temperature and 3-V excess bias voltage.

### 2. Device structure and simulation

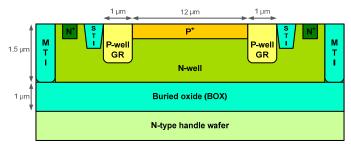

Figure 1 shows a cross section of the SPAD. It was fabricated in standard 140-nm SOI CMOS technology, in which thicknesses of the BOX layer and silicon layer over the BOX are about 1  $\mu$ m and 1.5  $\mu$ m, respectively. N-well and P-well are deposited over the p-type epi layer, because it is not based on substrate.

Fig. 1. Cross section of the fabricated SOI CMOS SPAD (MTI: medium trench isolation, STI: shallow trench isolation).

The SPAD was realized in a circular shape based on a  $P^+/N$ -well junction with an active-area diameter of 12  $\mu m$ . Shallow trench isolation (STI), generally provided in CMOS process technology nodes of 250 nm and smaller, can be used as a guard-ring (GR) structure to achieve the largest electric field at the junction [7], but in general it can bring high DCR due to etching-induced lattice defects and charge trapping associated with STI [8]. In the proposed SPAD, a merged implant GR structure was used to prevent premature edge breakdown, implemented by lateral diffusion of two closely spaced N-well regions. The width of the P-well GR was designed to have a 1  $\mu m$  width, considering the lateral diffusion length of the N-well. Most importantly, no process modification was required, so as to make the device fully compatible with the requirements of reliability of industrial SOI CMOS processes.

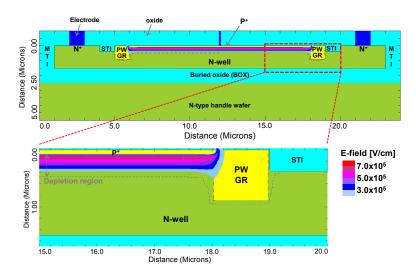

In order to investigate the effect of the GR structure and the electric field profiles at the planar junction, we performed device simulation with MEDICI, as shown in Fig. 2. It shows the simulated electric-field distribution when the SOI CMOS SPAD is biased above its breakdown voltage for Geiger-mode operation. As can be seen in this figure, the premature edge breakdown is effectively suppressed by the P-well (PW) GR. Consequently, the electric field is high enough (over  $6 \times 10^5$  V/cm) to ensure impact ionization all over the planar junction, which is much higher than the breakdown field in silicon of  $3 \times 10^5$  V/cm [9].

Fig. 2. Electric field in a SPAD biased above breakdown by an excess bias voltage  $V_E$  of 3 V.

### 3. Experimental results

For the SOI CMOS SPAD characterization, the SPAD chip was packaged and then measured. Because the SPAD is connected to PADs directly, it was operated in Geiger mode using a passive quenching resistor of about 20 k $\Omega$ . The P<sup>+</sup>/N-well junction is reverse biased with a positive voltage applied to the N-well contact, which is the sum of its breakdown voltage,  $V_B$ , and an excess bias voltage,  $V_E$ , and the P<sup>+</sup> contact is connected to the quenching resistor. Then the P<sup>+</sup> contact is connected to a high-performance oscilloscope to measure DCR, PDP, afterpulsing probability, and photon timing jitter. Measurements were done at room temperature except when indicated otherwise.

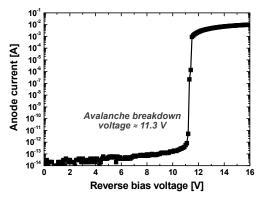

### 3.1. I-V characteristics

The I-V characteristic of the fabricated SPAD was firstly measured to check its breakdown voltage and consequently to measure the SPAD at the correct excess bias conditions. As shown in Fig. 3, the SPAD exhibits very low dark current, below 1 pA, before avalanche breakdown at about 11.3 V, where the current starts to increase drastically due to the avalanche multiplication process. The SPAD's breakdown voltage indicates a relatively high doping concentration of N-well at around 10<sup>17</sup> cm<sup>-3</sup> in this technology. In addition, it is experimentally demonstrated that the SPAD could not operate above about 23 V because the depletion region below the P-well GR reaches the BOX layer.

Fig. 3. Steady-state current-voltage characteristics under dark conditions at room temperature.

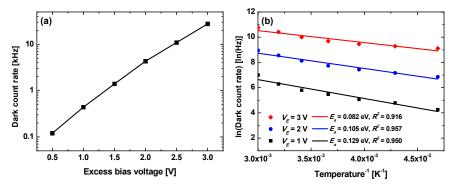

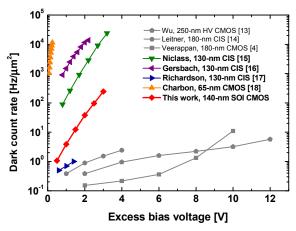

Figure 4 shows DCR characteristics of the SPAD measured at the different excess bias voltages in the dark; the DCR varies from a minimum of  $1.1 \text{ Hz/µm}^2$  to a maximum of  $244 \text{ Hz/µm}^2$ , at room temperature. Figure 4(b) shows the Arrhenius plot of DCR at three different excess bias voltages. DCR exhibits weak dependence on temperature, which indicates that the contribution of band-to-band tunneling to the DCR is much higher than that of Shockley-Read-Hall (SRH) thermal generation [2]. In addition, the low activation energies,  $E_a = 0.129$ , 0.105, and 0.082 eV, for the three excess bias voltages estimated from Fig. 4(b) are accordance with the band-to-band tunneling. We believe that a relatively high doping concentration of the N-well is responsible for this behavior, as confirmed by the I-V characteristics of Fig. 3. The DCR of this device is comparable to or about one order of magnitude higher than that of SPADs fabricated in bulk wafers. However, the DCR is similar to or better than that of SPADs based on SOI wafers in non-standard processes which is in the range between 3.5 kHz and 100 kHz [6, 10, 11].

Fig. 4. DCR (a) as a function of the excess bias voltage at room temperature and (b) as a function of the inverse of temperature for various excess bias voltages.

### 3.3. PDP

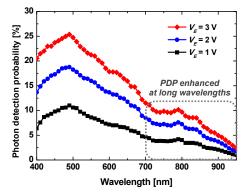

The measured PDP for incident-light wavelengths from 400 nm to 950 nm at three different excess bias voltages are plotted in Fig. 5. The SOI CMOS SPAD has a maximum PDP of about 25.4% at the 490-nm wavelength. Then, the PDP decreases for longer wavelengths because of the longer penetration depth of photons than the shallow  $P^+/N$ -well junction. However, it still provides 7.7-% PDP at the 850-nm wavelength where silicon has very low absorption coefficient, because the PDP of the SOI CMOS SPAD is enhanced at long wavelengths due to the cavity-like behavior of the interface between silicon and BOX layers. Such effect has been also reported in [10, 11].

Fig. 5. PDP as a function of wavelength for various excess bias voltages at room temperature.

# 3.4. Afterpulsing probability

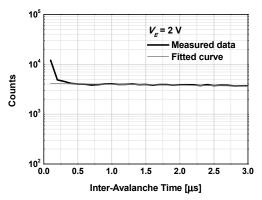

Afterpulsing is caused by carriers that were trapped in previous avalanches and that trigger spurious avalanches. The afterpulsing statistics of the SOI CMOS SPAD was measured using an inter-arrival time histogram method [12]. Figure 6 shows the measured inter-arrival time histogram of the SPAD with a fitted exponential curve. The afterpulsing probability is computed as the area between the histogram and the fitted exponential curve; in this device this value is about 1.7% setting a 100-ns dead time, but it can be further reduced down to 1% by increasing the dead time to 200 ns.

Fig. 6. Afterpulsing: inter-arrival time histogram measured at room temperature and exponential curve fit.

### 3.5. Timing jitter

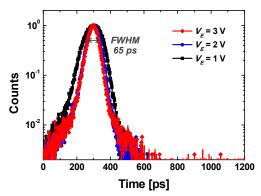

Timing jitter is defined as the uncertainty of time response of the SPAD to photons impinging the device. The time response was measured using the time-correlated single-photon counting (TCSPC) technique, whereas a fast laser source (Advanced Laser Diode Systems GmbH) at 405 nm and a repetition rate of 40 MHz was used. The histogram of the time interval between the laser output trigger and the SPAD raising edge was measured using an oscilloscope (LeCroy WavePro 760Zi-A) operating as a time-to-digital converter with a time bin of 2 ps (LSB). The resulting normalized histograms are shown in Fig. 7 for several excess bias voltages. The single-photon time resolution (SPTR) is as low as 65 ps (FWHM) for  $V_E = 3$  V, and it degrades, as expected, at lower excess bias voltages. The measured laser timing jitter was about 25 ps.

Fig. 7. Timing jitter performance as a function of excess bias voltage at room temperature using a 405-nm wavelength laser.

# 4. Comparison with the state-of-the-art CMOS SPADs

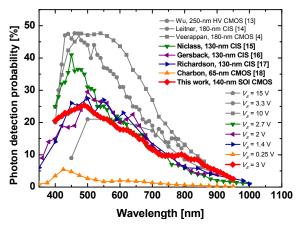

In general, deep-submicron SPADs have many advantages such as smaller pixel size, better timing resolution, larger array, higher speed, and higher fill factor. At the same time, however, there are also some disadvantages: lower and narrower PDP as well as higher tunneling noise due to higher doping concentrations. In order to compare performance of the proposed SPAD fabricated in 140-nm SOI CMOS technology to the literature in similar technology nodes, we restricted our attention to all reported substrate-isolated SPADs implemented in a feature size smaller than 250 nm [4, 13–18]. Consequently, SPADs fabricated in 350-nm CMOS technology are excluded in this comparison, although they exhibit good performance [19–21]. The reason for ruling out non-substrate-isolated SPADs is that they are not suitable for array configurations and for integration with electronic circuits in the same substrate due to high optical crosstalk and electrical interference from digital circuits [4, 22, 23].

Fig. 8. SPAD-performance comparison: PDP.

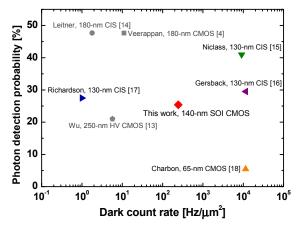

Figure 8 shows a PDP-performance comparison. The SPAD reported by Veerappan *et al.* shows a high and wide PDP profile due to the wide depletion region using a deep N-well (DNW) having a lower doping concentration and very high excess bias voltage [4]. Leitner *et al.* and Niclass *et al.* also reported SPADs providing relatively high PDP because of a retrograde DNW and optimized dielectrics for optical detection, respectively, supported by the CMOS image sensor (CIS) technologies [14, 15]. Compared to other CMOS SPADs, the SOI CMOS SPAD exhibits medium PDP at short wavelengths but overperforms most SPADs in the literature above 750 nm.

Fig. 9. SPAD-performance comparison: area-normalized DCR.

Figure 9 presents a DCR-performance comparison with the state-of-the-art CMOS SPADs. The SPADs fabricated in feature sizes larger than 180 nm tend to show better DCR performance. This is generally attributed to the fact that advanced CMOS technologies use narrower depletion widths and higher doping levels, which in turn cause higher band-to-band tunneling dark counts. Richardson *et al.* achieved low DCR using a low-doped P-well/retrograde DNW junction in the 130-nm CIS technology [17]. Compared with the similar-structure SPADs, which are based on P<sup>+</sup>/N-well or N<sup>+</sup>/P-well junctions, the DCR of the SOI CMOS SPAD is better than that of other SPADs implemented in 130-nm or 65-nm technologies. The state-of-the-art comparison of SPADs in terms of peak PDP and DCR is presented in Fig. 10.

Fig. 10. SPAD-performance comparison: peak PDP vs. area-normalized DCR.

The performance of the SPAD implemented in the standard 140-nm SOI CMOS technology reported in this paper is summarized in Table 1. In addition, it reports a performance comparison with substrate-isolated SPADs fabricated in advanced CMOS technologies (140-nm technology nodes and below).

Table 1. Performance summary and comparison with substrate-isolated SPADs fabricated in advanced CMOS technologies (140-nm technology nodes and below)

|                             | This work                            | [15]                                 | [16]                                    | [17]                              | [18]                                              |

|-----------------------------|--------------------------------------|--------------------------------------|-----------------------------------------|-----------------------------------|---------------------------------------------------|

| Technology                  | 140-nm SOI<br>CMOS<br>Technology     | 130-nm CMOS<br>Imaging<br>Process    | 130-nm CMOS<br>Imaging<br>Process       | 130-nm CMOS<br>Imaging<br>Process | 65-nm CMOS<br>Technology                          |

| PN junction<br>GR structure | P <sup>+</sup> /N-well P-<br>well GR | P <sup>+</sup> /N-well P-<br>well GR | P <sup>+</sup> /N-well<br>P&STI GR      | P-well/DNW<br>virtual GR          | N <sup>+</sup> /P-well N-<br>well GR              |

| Active area (diameter)      | 113.1 μm² (12 μm)                    | 87.5 μm <sup>2</sup> (10 μm)         | 58 μm <sup>2</sup> (8.6 μm)             | 50 μm <sup>2</sup> (8 μm)         | 56 μm <sup>2</sup> (8 μm)                         |

| Shape                       | Circular                             | Octagonal                            | Circular                                | Circular                          | Octagonal                                         |

| $V_B$                       | 11.3 V                               | 9.7 V                                | 9.4 V                                   | 14.4 V                            | 9.1 V                                             |

| $V_E$                       | 3 V                                  | 2.7 V                                | 2 V                                     | 1.4 V                             | 0.25 V                                            |

| DCR (@RT)                   | $27.6~kHz~0.24\\kHz/\mu m^2$         | 800 kHz 9.1<br>kHz/μm²               | 670 kHz 11.6<br>kHz/μm²                 | 50 Hz 1<br>Hz/μm²                 | 640 kHz 11.4<br>kHz/μm²                           |

| PDP peak                    | 25.4%<br>(@490 nm)                   | 41%<br>(@450 nm)                     | 30%<br>(@500 nm)                        | 28%<br>(@500 nm)                  | 5.5%<br>(@425 nm)                                 |

| PDP @850<br>nm              | 7.7%                                 | 3.8%                                 | 4.2%                                    | 5%                                | 0.5%                                              |

| Afterpulsing probability    | < 0.1% (@200-<br>ns dead time)       | n.a.                                 | < 1% (@180-ns<br>dead time)             | 0.02% (@100-<br>ns dead time)     | < 1% (@5-µs dead time)                            |

| Timing jitter               | 65 ps (@405<br>nm)                   | 144 ps (@637<br>nm)                  | 125 ps (@637 nm) $(@V_E = 1 \text{ V})$ | 200 ps<br>(@470, 815<br>nm)       | 235 ps<br>(@637 nm)<br>(@ $V_E = 0.4 \text{ V}$ ) |

DNW: deep N-well, GR: guard ring,  $V_B$ : Avalanche breakdown voltage,  $V_E$ : Excess bias voltage, RT: room temperature

# 5. Conclusion

We presented the first SPAD fabricated in standard SOI CMOS technology. The SPAD has been simulated, fabricated, and fully characterized in relation to the literature. Despite relatively high doping concentrations and higher defectivity of the SOI wafer, the realized SPAD has a DCR of 1.1 Hz/μm² at 0.5 V and 244 Hz/μm² at 3 V of excess bias, which is comparable to or better than DCR of similar-structure SPADs, based on P⁺/N-well or N⁺/P-well junctions, fabricated in advanced bulk CMOS technologies. The SOI CMOS SPAD achieves a peak PDP over 25% at 490-nm wavelength, along with enhanced PDP performance at long wavelengths due to the interface between silicon and BOX layers that acts as an optical cavity. With a dead time longer than 200 ns, the SPAD exhibits a remarkably low afterpulsing probability of less than 0.1%, and moreover it shows an excellent SPTR of 65-ps FWHM. The SPADs based on standard SOI CMOS technology will enable to provide future 3D-integrated image-sensor solutions.

# Acknowledgments

The authors would like to thank Frank Thus, Vishwas Jain, Chockalingam Veerappan, and Esteban Venialgo for providing feedback and comments.